622

EQEN

LOOPEN

TCLK

标记

时钟

选择

VCO

过滤

阶段 /

FREQ

发现

输入

选择

CAP0

CAP1

0.1 µf

输入

SAMPLER

框架

DEMUX

时钟

发生器

状态

机器

d-地方

解码器

c-地方

解码器

DAV*

CAV*

FF

LINKRDY

STAT1

STAT0

d0..d19

DIN

LIN

TCLKSEL

DIV1

DIV0

SMRTST1*

SMRTST0*

起作用的

FLAGSEL

错误

M20SEL

内部的

CLOCKS

FDIS

PH1

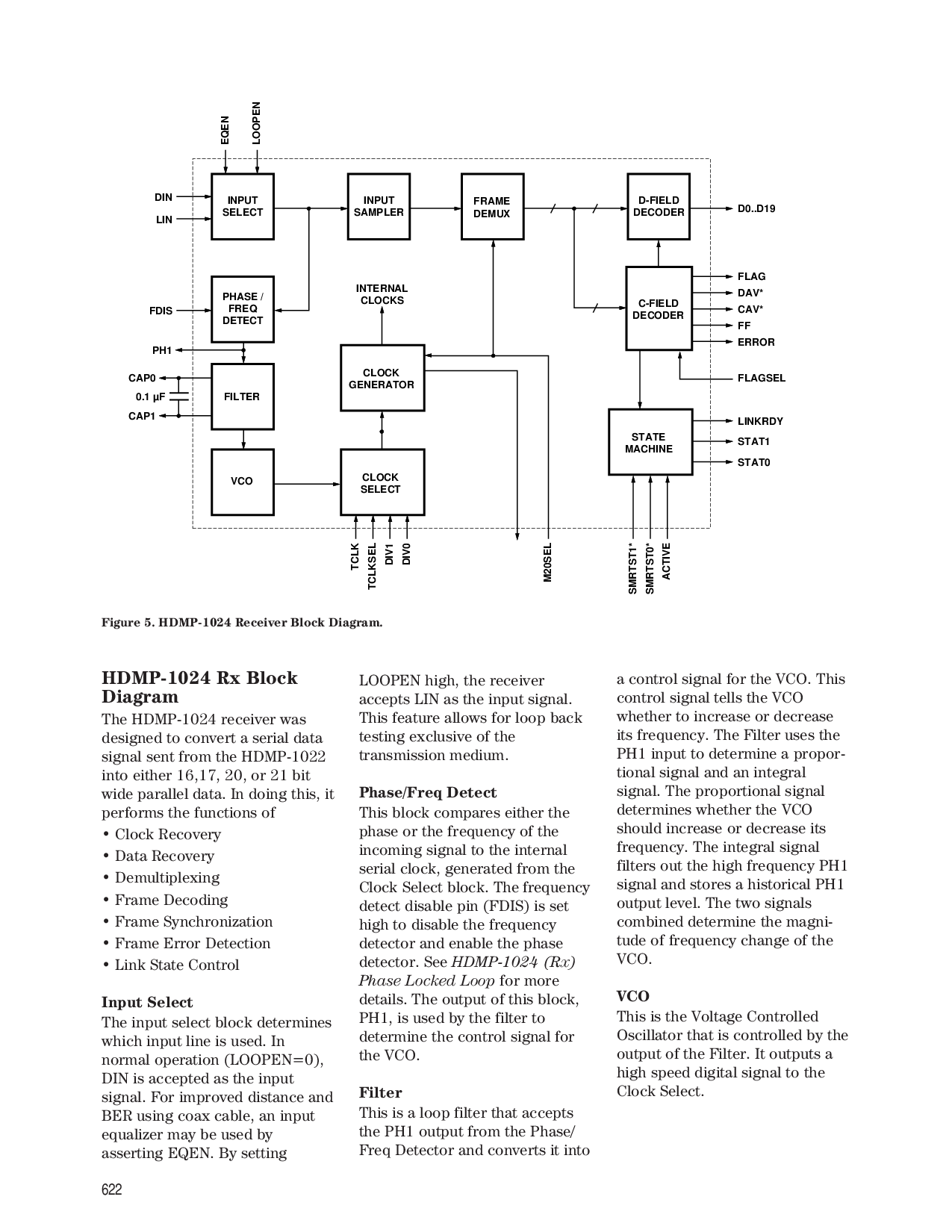

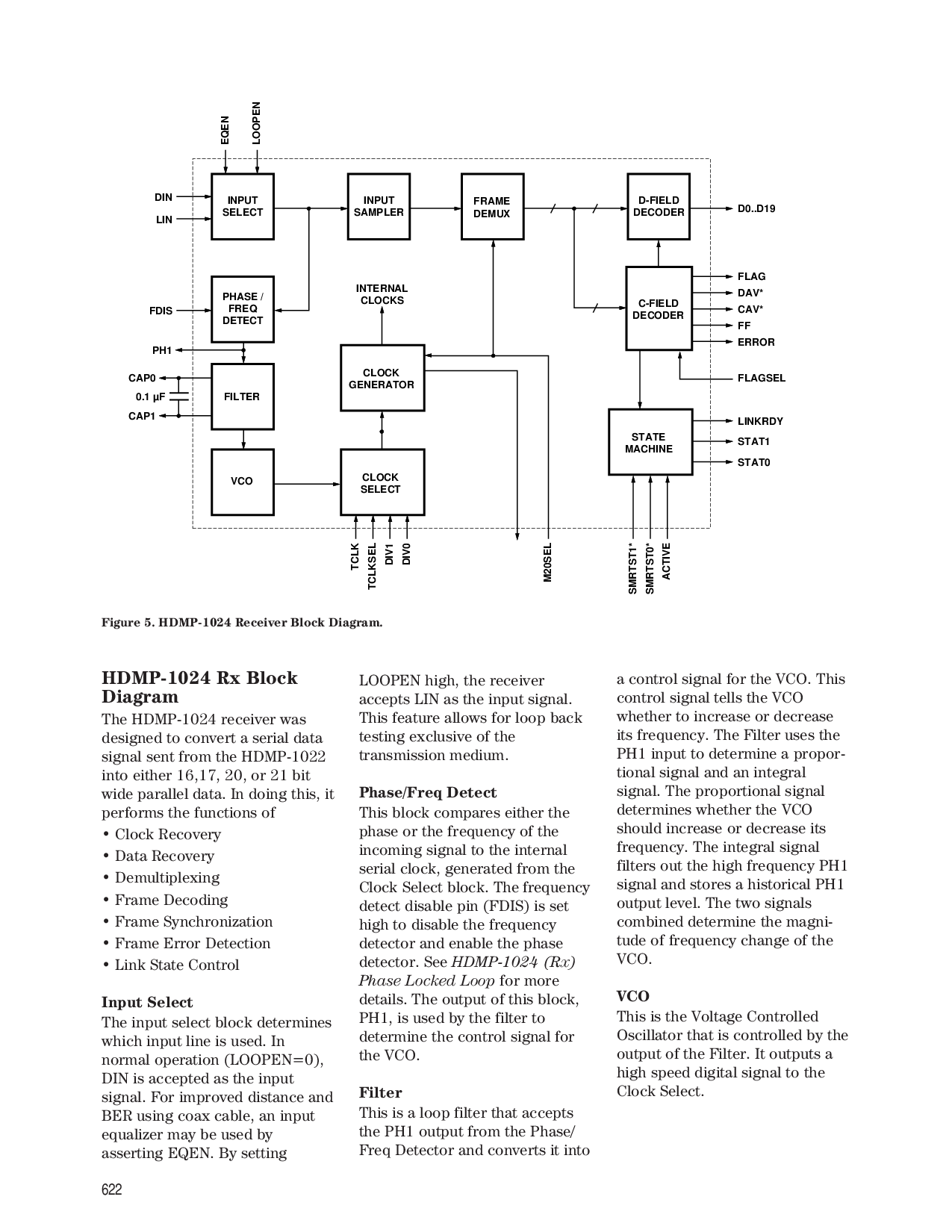

hdmp-1024 rx 块

图解

这 hdmp-1024 接受者 是

设计 至 转变 一个 串行 数据

信号 sent 从 这 hdmp-1022

在 也 16,17, 20, 或者 21 位

宽 并行的 数据. 在 做 这个, 它

执行 这 功能 的

• 时钟 恢复

• 数据 恢复

• demultiplexing

• 框架 解码

• 框架 同步

• 框架 错误 发现

• link 状态 控制

输入 选择

这 输入 选择 块 确定

这个 输入 线条 是 使用. 在

正常的 运作 (loopen=0),

din 是 accepted 作 这 输入

信号. 为 改进 距离 和

ber 使用 coax 缆索, 一个 输入

equalizer 将 是 使用 用

asserting eqen. 用 设置

loopen 高, 这 接受者

accepts lin 作 这 输入 信号.

这个 特性 准许 为 循环 后面的

测试 独有的 的 这

传递 中等.

阶段/freq 发现

这个 块 比较 也 这

阶段 或者 这 频率 的 这

新当选的 信号 至 这 内部的

串行 时钟, 发生 从 这

时钟 选择 块. 这 频率

发现 使不能运转 管脚 (fdis) 是 设置

高 至 使不能运转 这 频率

探测器 和 使能 这 阶段

探测器. 看

hdmp-1024 (rx)

阶段 锁 循环

为 更多

详细信息. 这 输出 的 这个 块,

ph1, 是 使用 用 这 过滤 至

决定 这 控制 信号 为

这 vco.

过滤

这个 是 一个 循环 过滤 那 accepts

这 ph1 输出 从 这 阶段/

freq 探测器 和 converts 它 在

一个 控制 信号 为 这 vco. 这个

控制 信号 tells 这 vco

whether 至 增加 或者 decrease

它的 频率. 这 过滤 使用 这

ph1 输入 至 决定 一个 propor-

tional 信号 和 一个 integral

信号. 这 均衡的 信号

确定 whether 这 vco

应当 增加 或者 decrease 它的

频率. 这 integral 信号

过滤 输出 这 高 频率 ph1

信号 和 stores 一个 historical ph1

输出 水平的. 这 二 信号

联合的 决定 这 magni-

tude 的 频率 改变 的 这

vco.

VCO

这个 是 这 电压 控制

振荡器 那 是 控制 用 这

输出 的 这 过滤. 它 输出 一个

高 速 数字的 信号 至 这

时钟 选择.

图示 5. hdmp-1024 接受者 块 图解.