6

绝对 最大 比率 热的 信息

supplyvoltage......................................3.6v

输入, 输出 或者 i/o 电压 . . . . . . . . . . . . 地 -0.5v 至 V

CC

+0.5v

esdclassification.................................class2

运行 情况

voltagerange.....................................+3.3v

temperaturerange.......................... -40

o

Cto85

o

C

热的 阻抗 (典型, 便条 3)

θ

JA

(

o

c/w)

lqfppackage............................. 50

maximumstoragetemperaturerange.......... -65

o

Cto150

o

C

MaximumJunctionTemperature.......................100

o

C

最大 含铅的 温度 (焊接 10s) . . . . . . . . . . . . .300

o

C

(含铅的 Tips 仅有的)

提醒: 压力 在之上 那些 列表 在 “Absolute 最大 Ratings” 将 导致 永久的 损坏 至 这 设备. 这个 是 一个 压力 仅有的 比率 和 operationofthe

设备 在 这些 或者 任何 其它 情况 在之上 那些 表明 在 这 运算的 sections 的 这个 规格 是 不 暗指.

便条:

4.

θ

JA

是 量过的 和 这 组件 挂载 在 一个 低 有效的 热的 conductivity 测试 板 在 自由 空气. 看 Tech Brief TB379 为 详细信息.

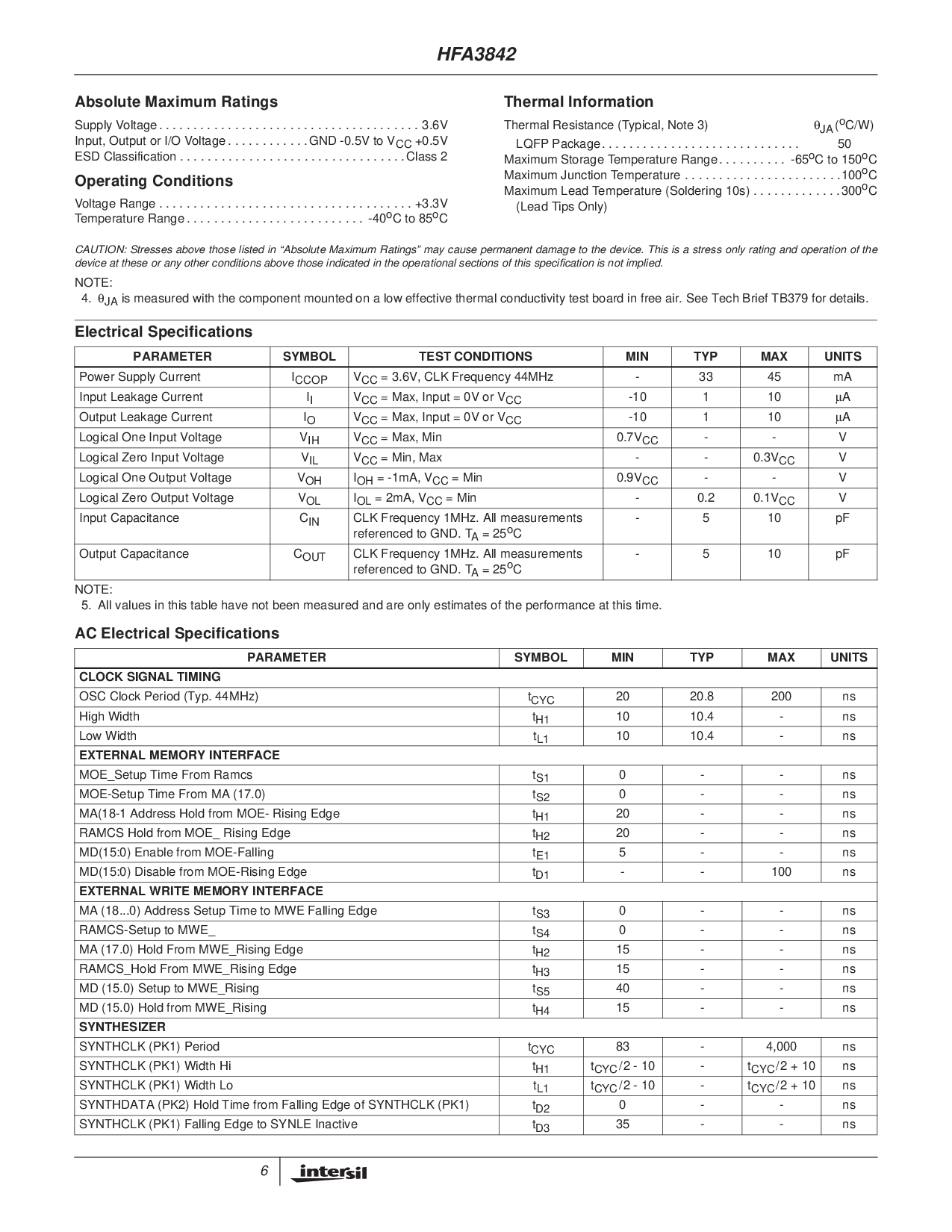

电的 规格

参数 标识 测试 情况 最小值 典型值 最大值 单位

电源 供应 电流 I

CCOP

V

CC

= 3.6v, CLK 频率 44MHz - 33 45 毫安

输入 泄漏 电流 I

I

V

CC

= 最大值, 输入 = 0V 或者 V

CC

-10 1 10

µ

一个

输出 泄漏 电流 I

O

V

CC

= 最大值, 输入 = 0V 或者 V

CC

-10 1 10

µ

一个

Logical 一个 输入 电压 V

IH

V

CC

= 最大值, 最小值 0.7v

CC

--v

Logical 零 输入 电压 V

IL

V

CC

= 最小值, 最大值 - - 0.3v

CC

V

Logical 一个 输出 电压 V

OH

I

OH

=-1ma,v

CC

=Min 0.9v

CC

--v

Logical 零 输出 电压 V

OL

I

OL

=2ma,v

CC

=Min - 0.2 0.1v

CC

V

输入 电容 C

在

CLK 频率 1mhz. 所有 度量

关联 至 地. T

一个

=25

o

C

-510pf

输出 电容 C

输出

CLK 频率 1mhz. 所有 度量

关联 至 地. T

一个

=25

o

C

-510pf

便条:

5. 所有 值 在 这个 表格 有 不 被 量过的 和 是 仅有的 估计 的 这 效能 在 这个 时间.

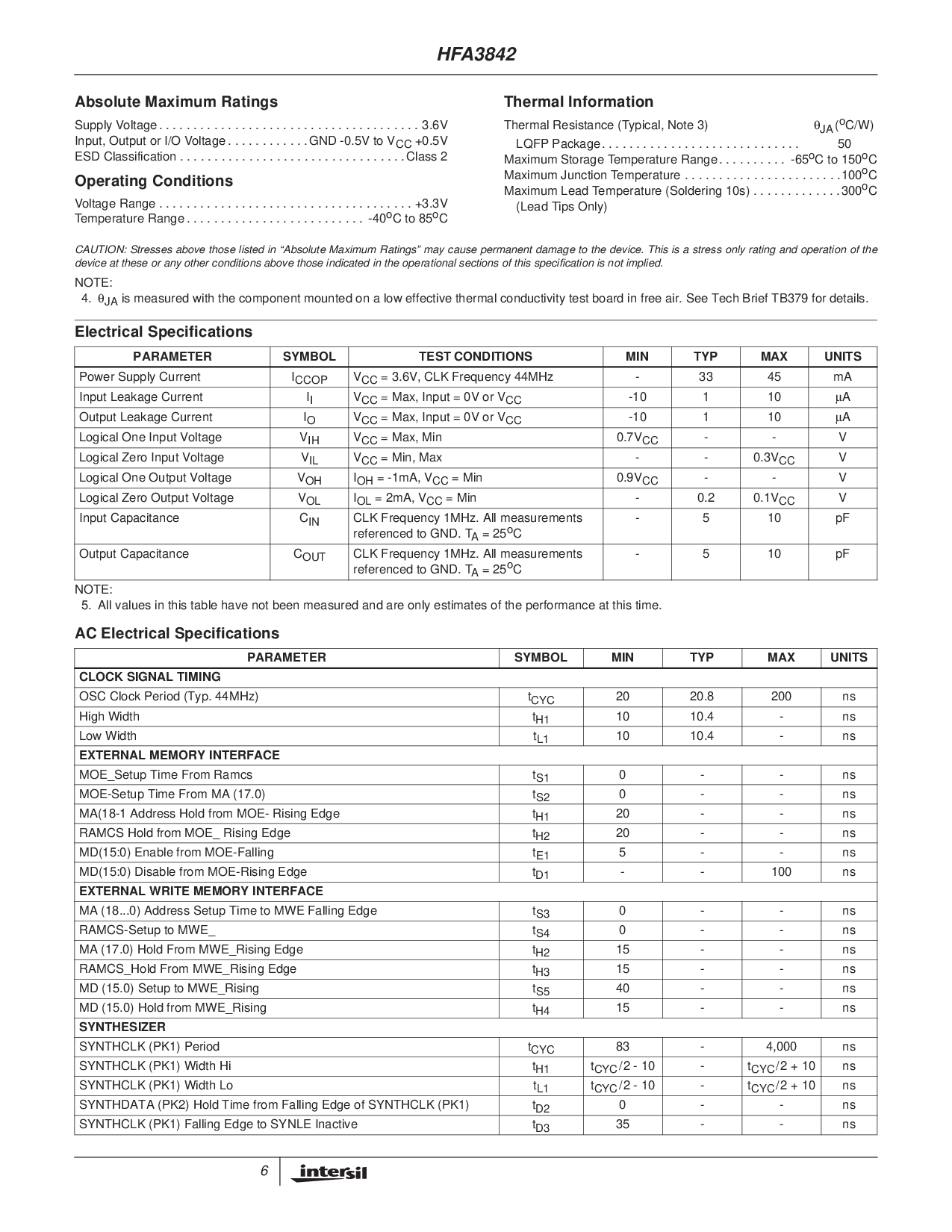

交流 电的 规格

参数 标识 最小值 典型值 最大值 单位

时钟 信号 定时

OSC 时钟 时期 (典型值. 44mhz) t

CYC

20 20.8 200 ns

高 宽度 t

H1

10 10.4 - ns

低 宽度 t

L1

10 10.4 - ns

外部 记忆 接口

moe_建制 时间 从 Ramcs t

S1

0--ns

moe-建制 时间 从 毫安 (17.0) t

S2

0--ns

毫安(18-1 地址 支撑 从 moe- Rising 边缘 t

H1

20 - - ns

ramcsholdfrommoe_risingedge t

H2

20 - - ns

md(15:0) 使能 从 moe-下落 t

E1

5--ns

md(15:0) 使不能运转 从 moe-rising 边缘 t

D1

--100ns

外部 写 记忆 接口

毫安 (18...0) 地址 建制 时间 至 MWE 下落 边缘 t

S3

0--ns

ramcs-setuptomwe_ t

S4

0--ns

毫安 (17.0) 支撑 从 mwe_rising 边缘 t

H2

15 - - ns

ramcs_支撑 从 mwe_rising 边缘 t

H3

15 - - ns

MD (15.0) 建制 至 mwe_rising t

S5

40 - - ns

MD (15.0) 支撑 从 mwe_rising t

H4

15 - - ns

SYNTHESIZER

SYNTHCLK (pk1) 时期 t

CYC

83 - 4,000 ns

SYNTHCLK (pk1) 宽度 Hi t

H1

t

CYC

/2 - 10 - t

CYC

/2 + 10 ns

SYNTHCLK (pk1) 宽度 Lo t

L1

t

CYC

/2 - 10 - t

CYC

/2 + 10 ns

SYNTHDATA (pk2) 支撑 时间 从 下落 边缘 的 SYNTHCLK (pk1) t

D2

0--ns

SYNTHCLK (pk1) 下落 边缘 至 SYNLE Inactive t

D3

35 - - ns

HFA3842