4-5

控制 端口 (4 线)

这 串行 控制 端口 是 使用 至 serially 写 和 读

数据 至/从 这 设备. 这个 串行 端口 能 运作 向上 至 一个

11mhz 比率 或者 1/2 这 最大 主控 时钟 比率 的 这

设备, MCLK (whichever 是 更小的). MCLK 必须 是 运动

和 重置 必须 是 inactive 在 程序编制. 这个

端口 是 使用 至 程序 和 至 读 所有 内部的 寄存器.

这 第一 8 位 总是 代表 这 地址 followed

立即 用 这 8 数据 位 为 那 寄存器. 这 lsb 的

这 地址 是 一个 don’t 小心, 但是 保留 为 future

expansion. 这 串行 transfers 是 accomplished 通过

这 串行 数据 管脚 (sd). sd 是 一个 双向的 串行 数据

总线. 碎片 选择 (

cs), 和 读/write (r/w) 是 也

必需的 作 handshake 信号 为 这个 端口. 这 时钟 使用

在 conjunction 和 这 地址 和 数据 在 sd 是 sclk.

这个 时钟 是 提供 用 这 外部 源 和 它 是 一个

输入 至 这 hfa3863. 这 定时 relationships 的 这些

信号 是 illustrated 在 计算数量 2 和 3. r/

W 是 高 当

数据 是 至 是 读, 和 低 当 它 是 至 是 写.

CS 是 一个

异步的 重置 至 这 状态 机器.

cs 必须 是

起作用的 (低) 在 这 全部 数据 转移 循环.

CS 选择

这 串行 控制 端口 设备 仅有的. 这 串行 控制 端口

运作 asynchronously 从 这 tx 和 rx 端口 和 它

能 accomplish 数据 transfers 独立 的 这 activity 在

这 其它 数字的 或者 相似物 端口.

这 hfa3863 有 96 内部的 寄存器 那 能 是

配置 通过 这 控制 端口. 这些 寄存器 是

列表 在 这 配置 和 控制 内部的 寄存器

表格. 表格 9 lists 这 配置 寄存器 号码, 一个 brief

名字 描述 这 寄存器, 这 十六进制 地址 至 进入

各自 的 这 寄存器 和 典型 值. 这 类型 indicates

whether 这 相应的 寄存器 是 读 仅有的 (r) 或者

读/写 (r/w). 一些 寄存器 是 二 字节 宽 作

表明 在 这 表格 (高 和 低 字节).

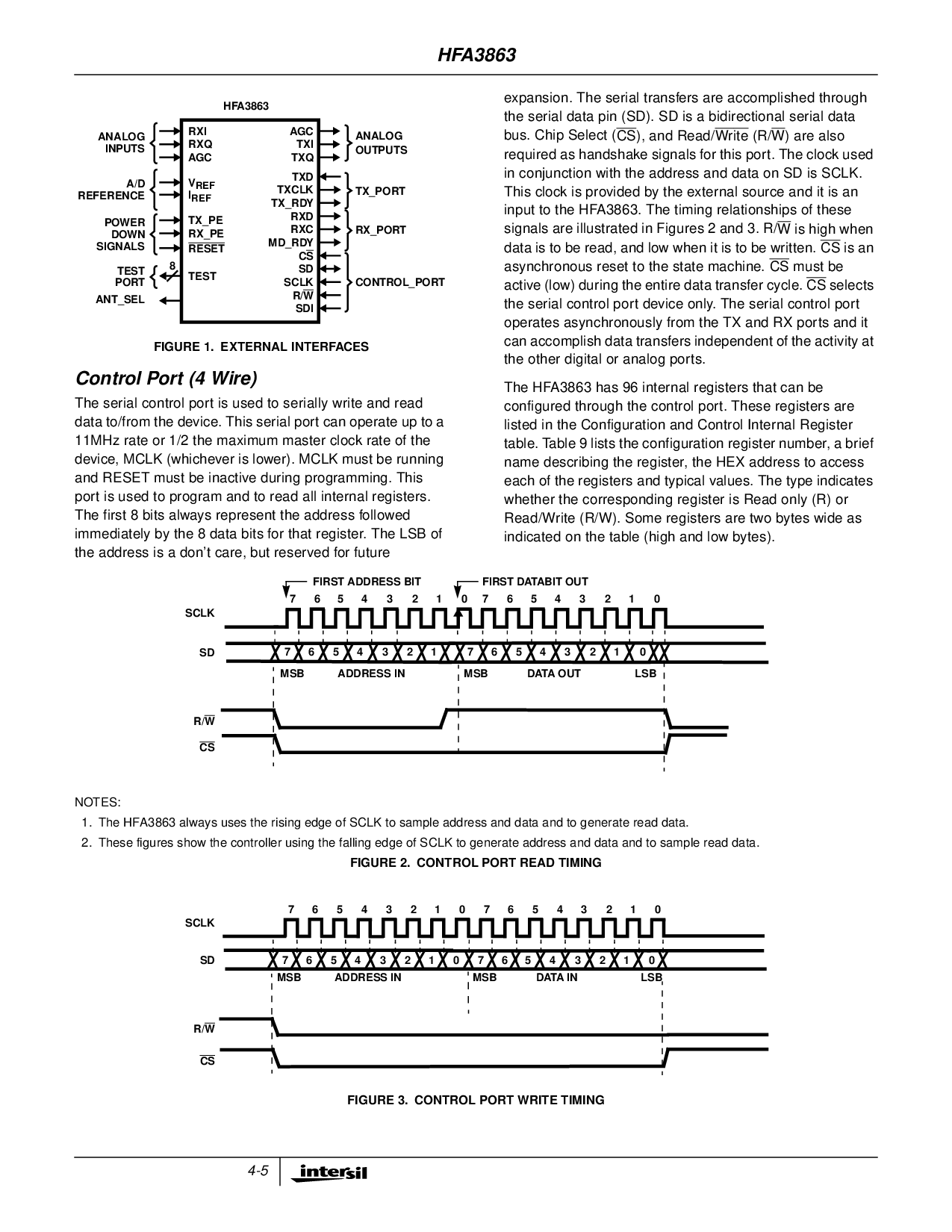

TXD

TXCLK

tx_rdy

RXD

RXC

md_rdy

C

S

SD

SCLK

r/

W

SDI

RXI

RXQ

AGC

V

REF

I

REF

tx_pe

rx_pe

重置

测试

tx_端口

rx_端口

控制_端口

相似物

输入

一个/d

涉及

电源

向下

信号

测试

端口

8

HFA3863

图示 1. 外部 接口

ant_sel

AGC

TXI

TXQ

相似物

输出

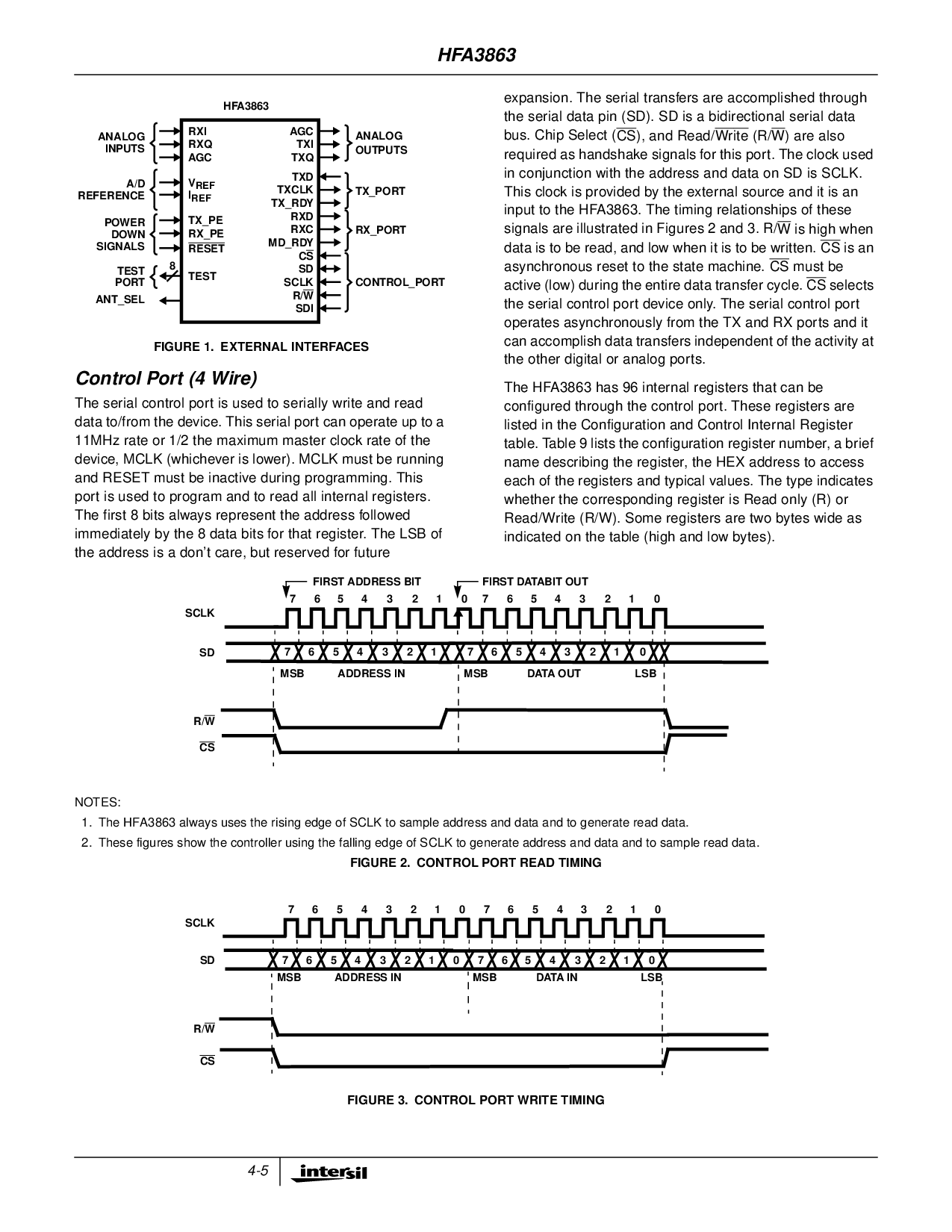

注释:

1. 这 hfa3863 总是 使用 这 rising 边缘 的 sclk 至 样本 地址 和 数据 和 至 发生 读 数据.

2. 这些 计算数量 显示 这 控制 使用 这 下落 边缘 的 sclk 至 发生 地址 和 数据 和 至 样本 读 数据.

图示 2. 控制 端口 读 定时

图示 3. 控制 端口 写 定时

7654321076543210

1234567 01234567

SCLK

SD

CS

r/

W

lsbdata outmsbmsb 地址 在

第一 地址 位 第一 databit 输出

7654321076543210

1234567 012345670

SCLK

SD

CS

r/w

lsbdata inmsbmsb 地址 在

HFA3863