8

看 向上 表格 模式

一个 看 向上 表格 (lut) 是 使用 至 执行 一个 fixed

transformation 函数 在 pixel 值. 这个 是 特别

有用的 当 这 transformation 是 非线性的 和 不能 是

认识到 直接地 和 硬件. 一个 例子 是 这 remapping

的 这 原来的 pixel 值 至 一个 新 设置 的 值 为基础 在

这 cdf 得到 通过 histogram accumulation.

这 transformation 函数 能 是 承载 在 这 lut 在

一个 的 三 方法: 在 lut 模式, 通过 din0-23; 在 也

异步的 模式, 在 这 dio 总线 作 描述 在下

下面 异步的 16/24 模式; 在 这 histogram

accumulate 模式 这 transformation 函数 是 计算

内部 (看 描述 在之上). 这 transformation

函数 能 然后 是 使用 用 deactivating

开始, putting

这 部分 在 lut 模式 和 clocking 这 数据 至 是

transformed 面向 这 管脚 总线. 便条 那 它 是 需要 至

wait 一个 时钟 循环 之后 changing 这 模式 在之前 clocking

数据 在 这 部分.

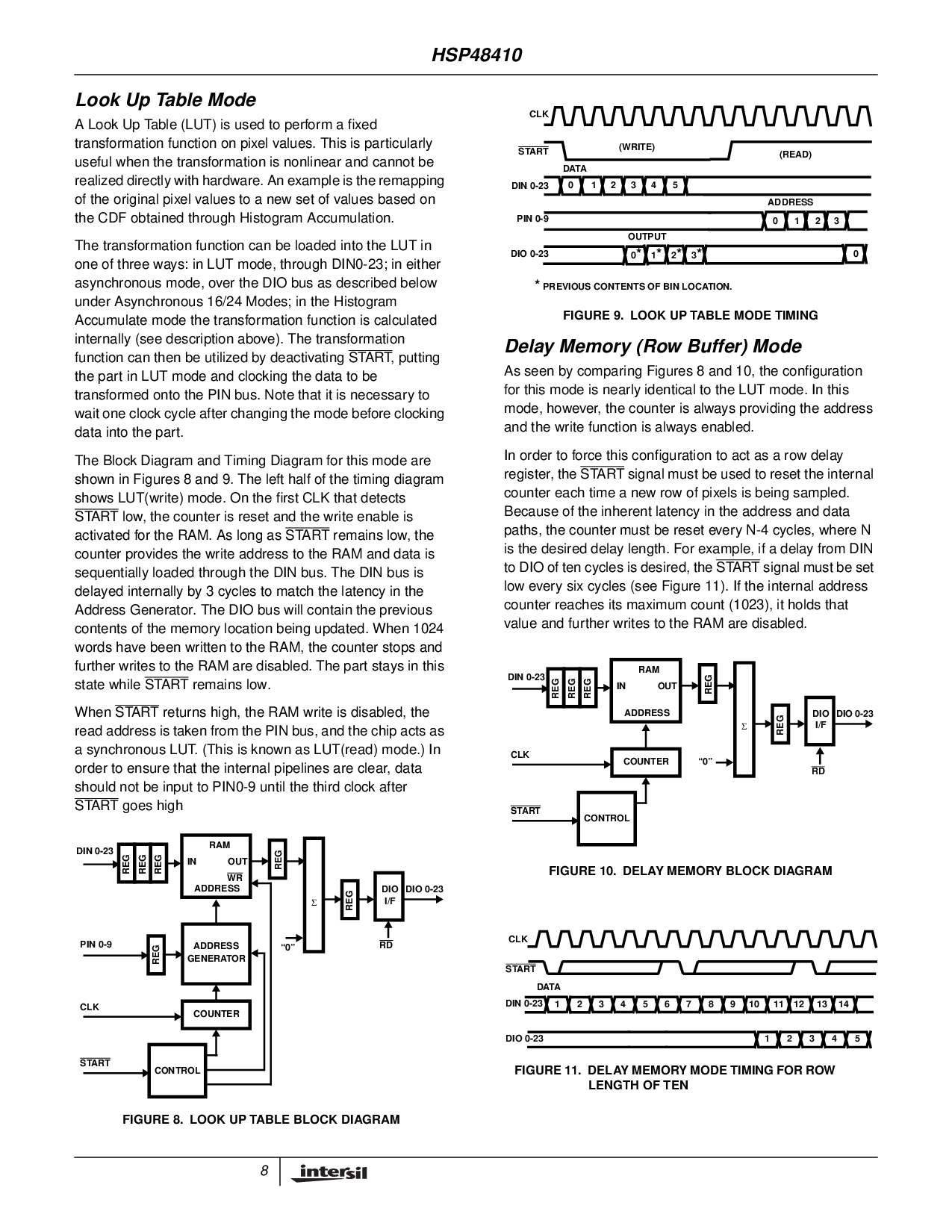

这 块 图解 和 定时 图解 为 这个 模式 是

显示 在 计算数量 8 和 9. 这 left half 的 这 定时 图解

显示 lut(写) 模式. 在 这 first clk 那 发现

开始 低, 这 计数器 是 重置 和 这 写 使能 是

使活动 为 这 内存. 作 长 作

开始 仍然是 低, 这

计数器 提供 这 写 地址 至 这 内存 和 数据 是

sequentially 承载 通过 这 din 总线. 这 din 总线 是

delayed 内部 用 3 循环 至 相一致 这 latency 在 这

地址 发生器. 这 dio 总线 将 包含 这 previous

内容 的 这 记忆 location 正在 updated. 当 1024

words 有 被 写 至 这 内存, 这 计数器 stops 和

更远 写 至 这 内存 是 无能. 这 部分 stays 在 这个

状态 当

开始 仍然是 低.

当 开始 returns 高, 这 内存 写 是 无能, 这

读 地址 是 带去 从 这 管脚 总线, 和 这 碎片 acts 作

一个 同步的 lut. (这个 是 知道 作 lut(读) 模式.) 在

顺序 至 确保 那 这 内部的 pipelines 是 clear, 数据

应当 不 是 输入 至 pin0-9 直到 这 第三 时钟 之后

开始 变得 高

延迟 记忆 (行 缓存区) 模式

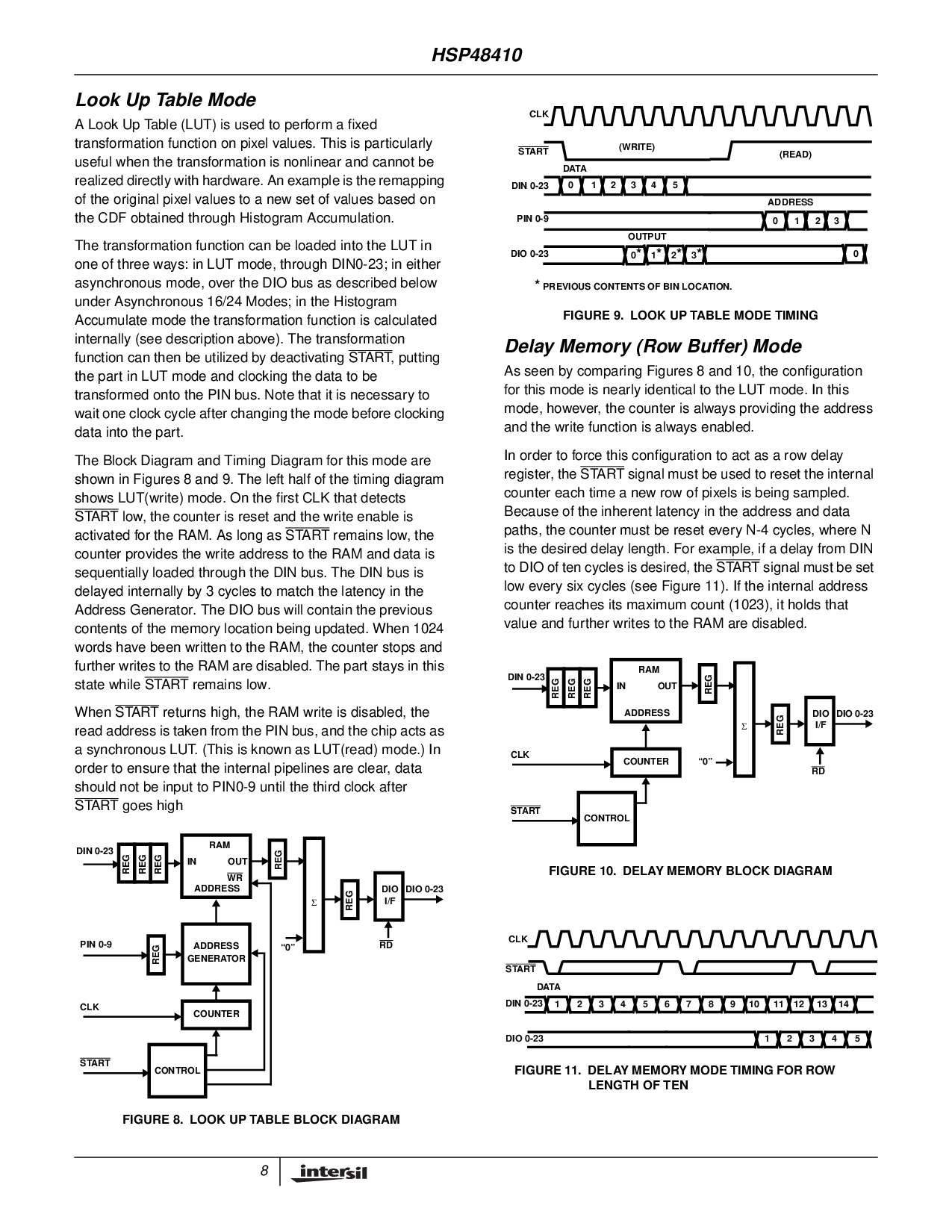

作 seen 用 comparing 计算数量 8 和 10, 这 configuration

为 这个 模式 是 nearly 完全同样的 至 这 lut 模式. 在 这个

模式, 不管怎样, 这 计数器 是 总是 供应 这 地址

和 这 写 函数 是 总是 使能.

在 顺序 至 强迫 这个 configuration 至 act 作 一个 行 延迟

寄存器, 这

开始 信号 必须 是 使用 至 重置 这 内部的

计数器 各自 时间 一个 新 行 的 pixels 是 正在 抽样.

因为 的 这 固有的 latency 在 这 地址 和 数据

paths, 这 计数器 必须 是 重置 每 n-4 循环, 在哪里 n

是 这 desired 延迟 长度. 为 例子, 如果 一个 延迟 从 DIN

至 DIO 的 ten 循环 是 desired, 这

开始 信号 必须 是 设置

低 每 六 循环 (看 图示 11). 如果 这 内部的 地址

计数器 reaches 它的 最大 计数 (1023), 它 holds 那

值 和 更远 写 至 这 内存 是 无能.

地址

发生器

内存

Σ

在 输出

地址

dio 0-23

CLK

开始

控制

DIO

i/f

REG

REG

计数器

管脚 0-9

REG

REG

REG

REG

“0”

WR

din 0-23

RD

图示 8. 看 向上 表格 块 图解

图示 9. 看 向上 表格 模式 定时

CLK

管脚 0-9

开始

dio 0-23

din 0-23

数据

0

输出

0

*

(写)

地址

1

0

(读)

*

previous 内容 的 bin location.

1234 5

1

*

2

*

3

*

230

内存

Σ

在 输出

地址

dio 0-23

CLK

开始

控制

DIO

i/f

REG

REG

计数器

REG

REG

REG

“0”

din 0-23

RD

图示 10. 延迟 记忆 块 图解

CLK

din 0-23

开始

dio 0-23

数据

12345678910111213

1234

14

5

图示 11. 延迟 记忆 模式 定时 为 行

长度 的 ten

HSP48410