hy57v561620(l)t

修订 1.8 / apr.01

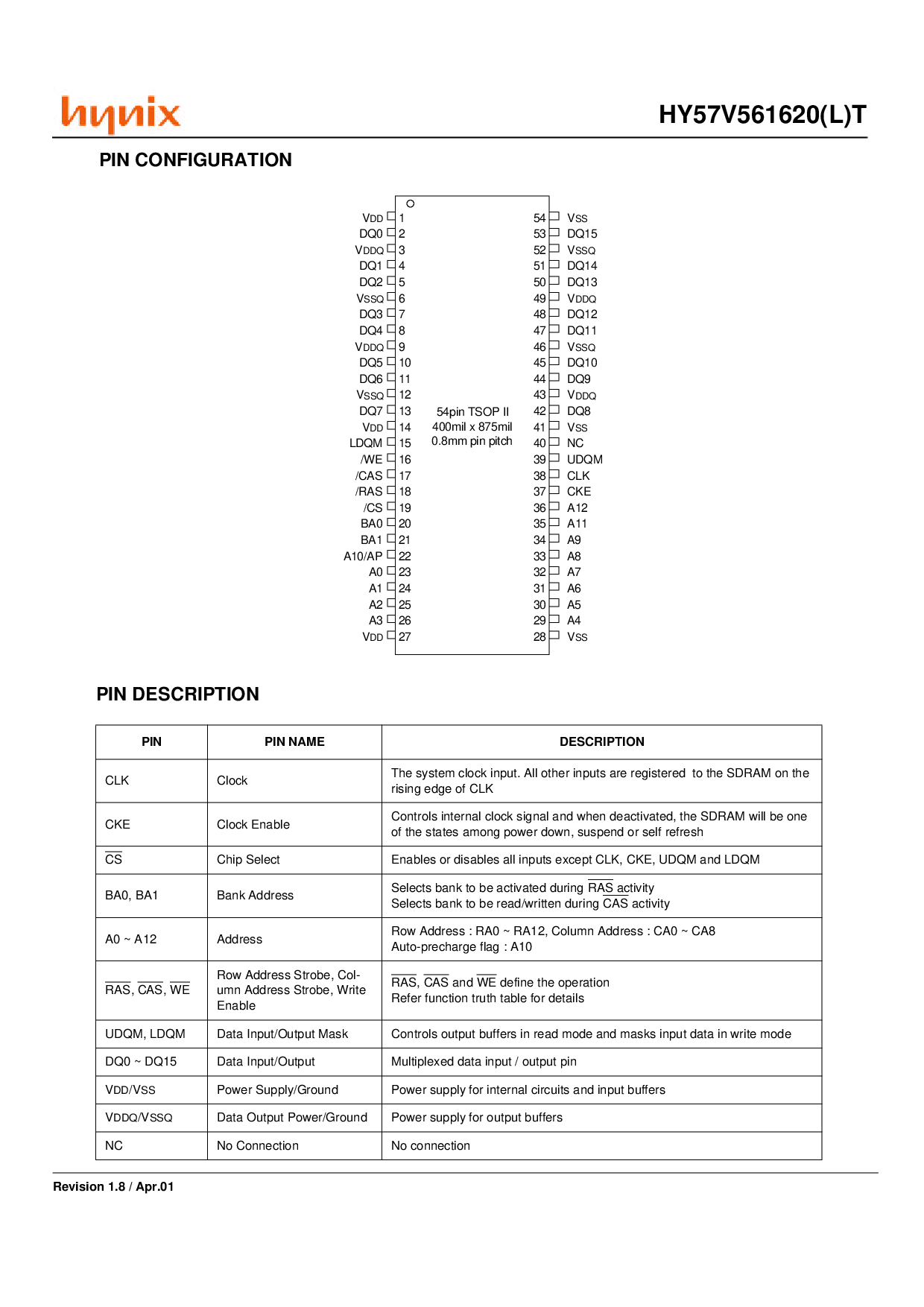

管脚 配置

VSS

DQ15

V

SSQ

DQ14

DQ13

V

DDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

V

DDQ

DQ8

V

SS

NC

UDQM

CLK

CKE

A12

A11

A9

A8

A7

A6

A5

A4

V

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

VDD

DQ0

V

DDQ

DQ1

DQ2

V

SSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

V

SSQ

DQ7

V

DD

LDQM

/我们

/CAS

/RAS

/CS

BA0

BA1

a10/ap

A0

A1

A2

A3

V

DD

54管脚 tsop ii

400mil x 875mil

0.8mm 管脚 程度

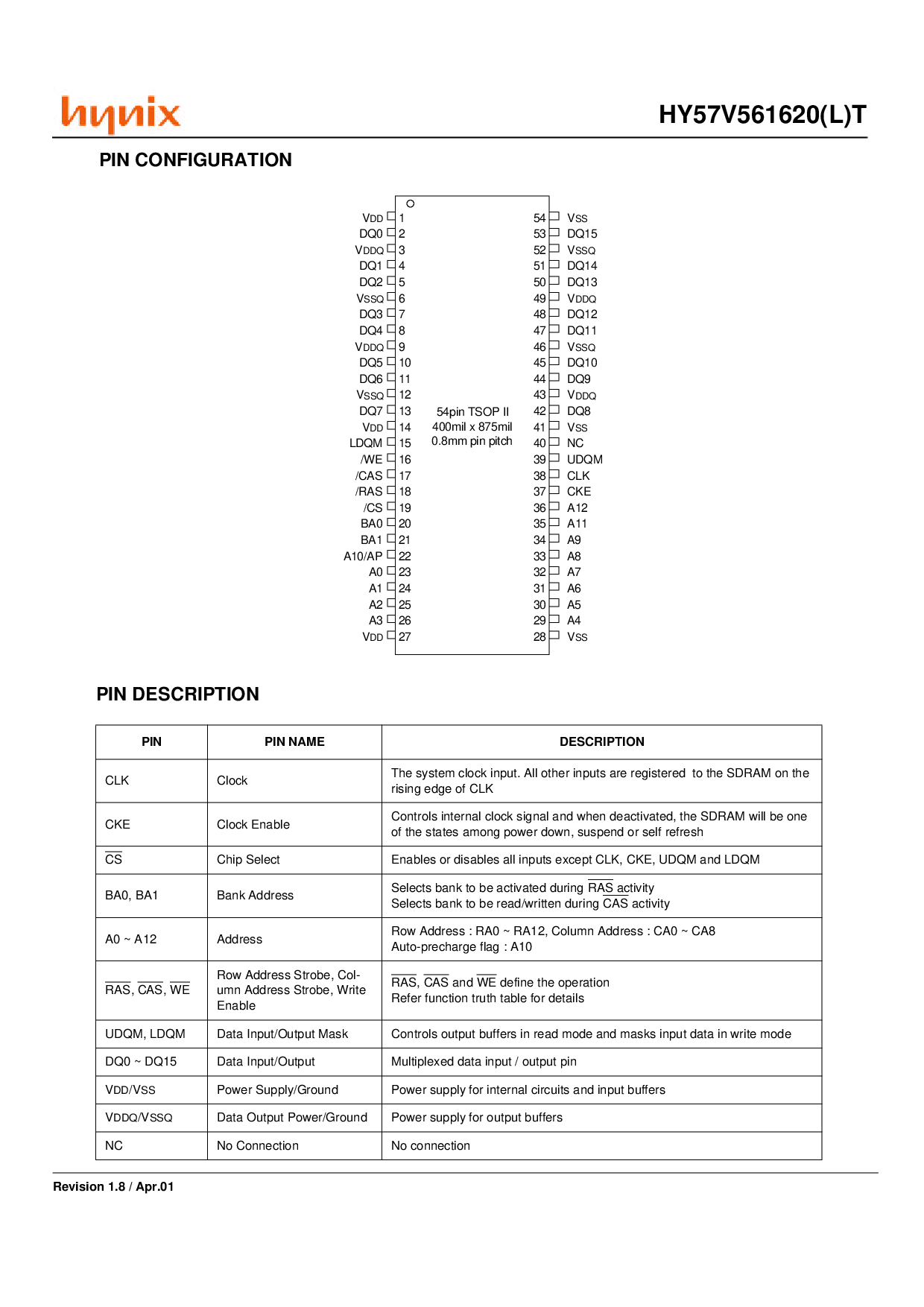

管脚 描述

管脚 管脚 名字 描述

CLK 时钟

这 系统 时钟 输入. 所有 其它 输入 是 注册 至 这 sdram 在 这

rising 边缘 的 clk

CKE 时钟 使能

控制 内部的 时钟 信号 和 当 deactivated, 这 sdram 将 是 一个

的 这 states among 电源 向下, suspend 或者 自 refresh

CS 碎片 选择 使能 或者 使不能运转 所有 输入 除了 clk, cke, udqm 和 ldqm

ba0, ba1 bank 地址

选择 bank 至 是 使活动 在RASactivity

选择 bank 至 是 读/写 在CASactivity

a0 ~ a12 地址

行 地址 : ra0 ~ ra12, column 地址 : ca0 ~ ca8

自动-precharge 标记 : a10

RAS,CAS,我们

行 地址 strobe, col-

umn 地址 strobe, 写

使能

RAS,CAS和我们定义 这 运作

谈及 函数 真实 表格 为 详细信息

udqm, ldqm 数据 输入/输出 掩饰 控制 输出 缓存区 在 读 模式 和 masks 输入 数据 在 写 模式

dq0 ~ dq15 数据 输入/输出 多路复用 数据 输入 / 输出 管脚

VDD/vSS 电源 供应/地面 电源 供应 为 内部的 电路 和 输入 缓存区

VDDQ/vSSQ 数据 输出 电源/地面 电源 供应 为 输出 缓存区

NC 非 连接 非 连接