飞利浦 半导体

SC16C2552

双 uart 和 16-字节 transmit 和 receive fifos

产品 数据 rev. 03 — 20 六月 2003 4 的 38

9397 750 11636

© koninklijke 飞利浦 electronics n.v. 2003. 所有 权利 保留.

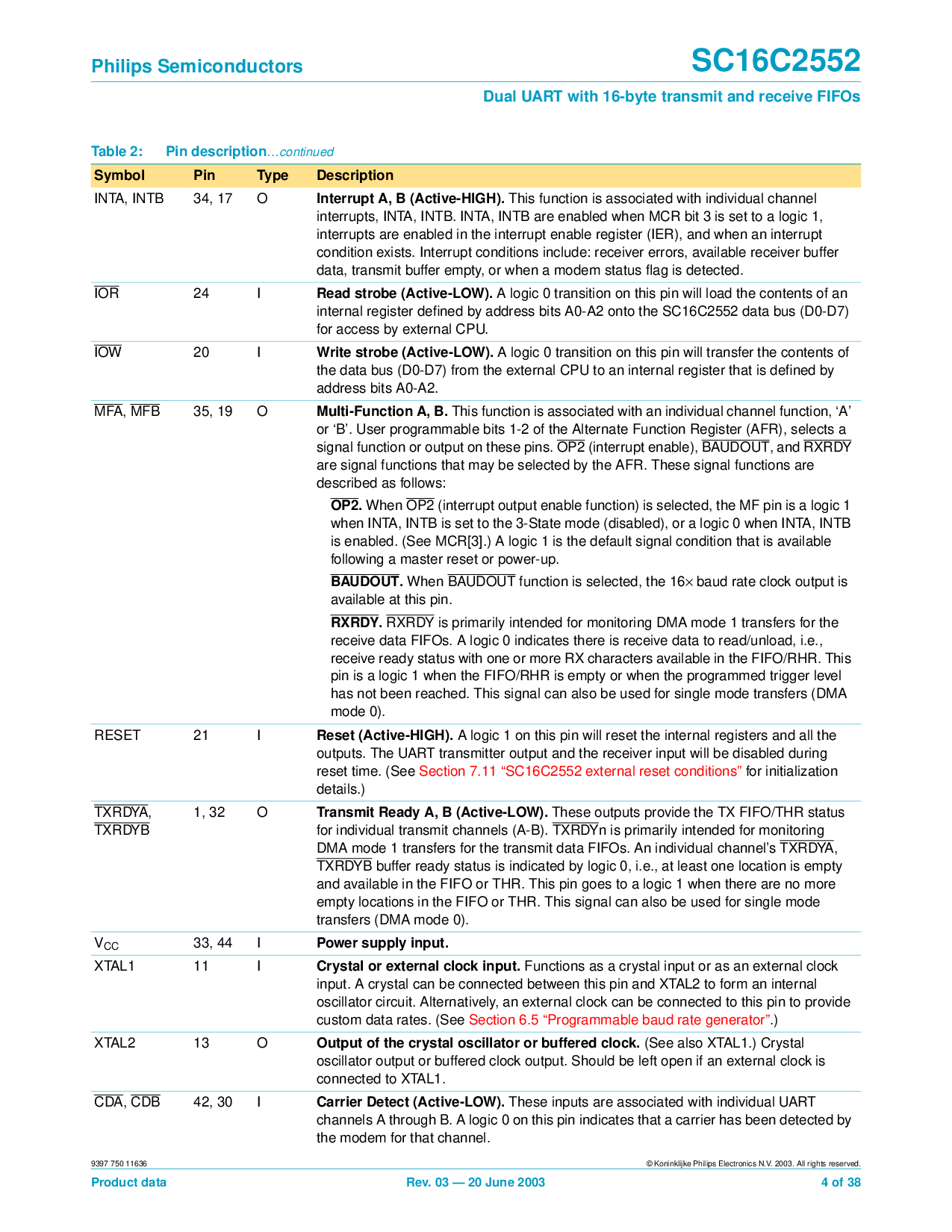

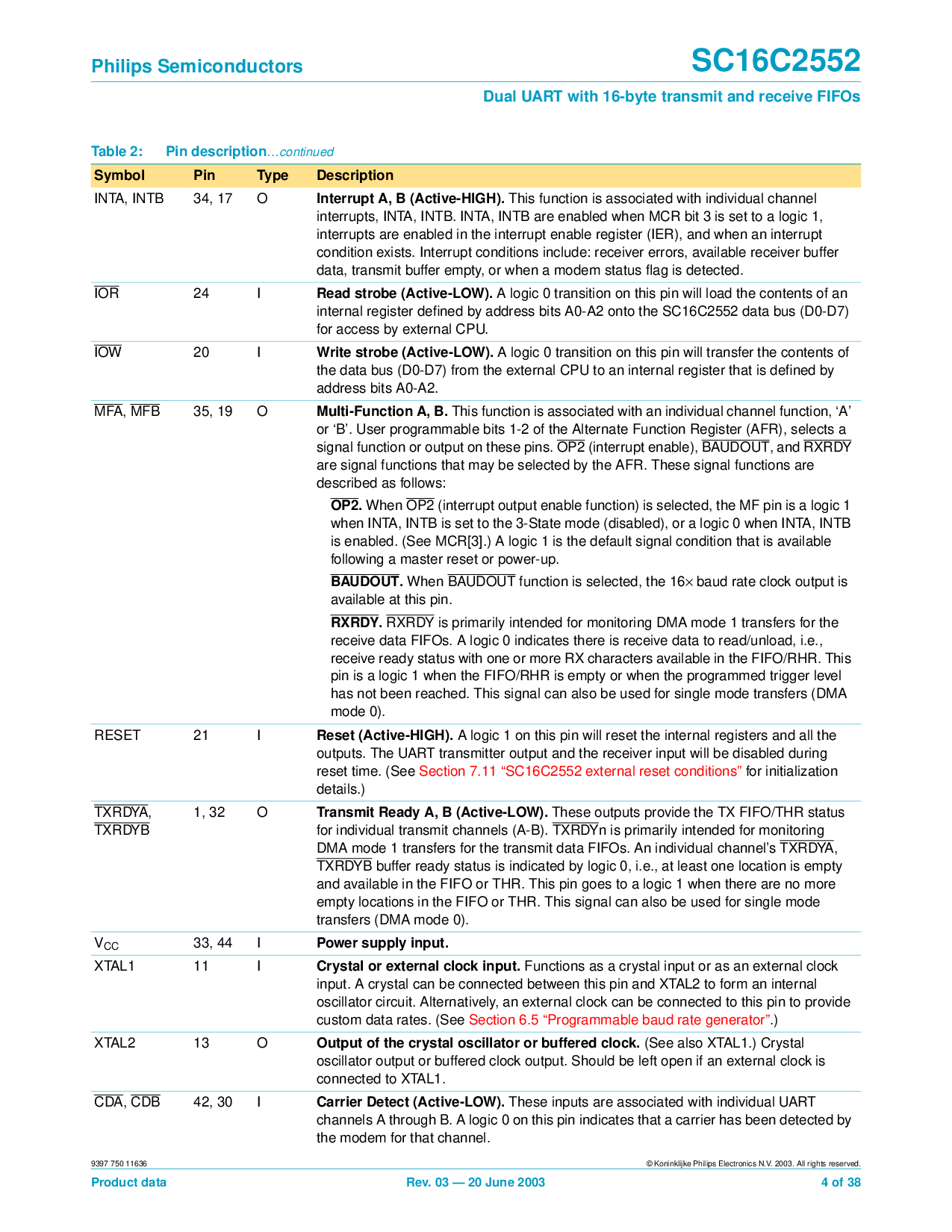

inta, intb 34, 17 O

中断 一个, b (起作用的-高).

这个 函数 是 有关联的 和 单独的 频道

中断, inta, intb. inta, intb 是 使能 当 mcr 位 3 是 设置 至 一个 逻辑 1,

中断 是 使能 在 这 中断 使能 寄存器 (ier), 和 当 一个 中断

情况 exists. 中断 情况 包含: 接受者 errors, 有 接受者 缓存区

数据, transmit 缓存区 empty, 或者 当 一个 modem 状态 flag 是 发现.

IOR 24 I

读 strobe (起作用的-低).

一个 逻辑 0 转变 在 这个 管脚 将 加载 这 内容 的 一个

内部的 寄存器 defined 用 地址 位 a0-a2 面向 这 sc16c2552 数据 总线 (d0-d7)

为 进入 用 外部 cpu.

IOW20I

写 strobe (起作用的-低).

一个 逻辑 0 转变 在 这个 管脚 将 转移 这 内容 的

这 数据 总线 (d0-d7) 从 这 外部 cpu 至 一个 内部的 寄存器 那 是 defined 用

地址 位 a0-a2.

mfa, MFB 35, 19 O

multi-函数 一个, b.

这个 函数 是 有关联的 和 一个 单独的 频道 函数, ‘A’

或者 ‘b’. 用户 可编程序的 位 1-2 的 这 alternate 函数 寄存器 (afr), 选择 一个

信号 函数 或者 输出 在 这些 管脚.

OP2 (中断 使能), baudout, 和 RXRDY

是 信号 功能 那 将 是 选择 用 这 afr. 这些 信号 功能 是

描述 作 跟随:

op2.

当 OP2 (中断 输出 使能 函数) 是 选择, 这 MF 管脚 是 一个 逻辑 1

当 inta, INTB 是 设置 至 这 3-状态 模式 (无能), 或者 一个 逻辑 0 当 inta, INTB

是 使能. (看 mcr[3].) 一个 逻辑 1 是 这 default 信号 情况 那 是 有

下列的 一个 主控 重置 或者 电源-向上.

baudout.

当 baudout 函数 是 选择, 这 16

×

波特 比率 时钟 输出 是

有 在 这个 管脚.

rxrdy.

rxrdy 是 primarily 将 为 monitoring dma 模式 1 transfers 为 这

receive 数据 fifos. 一个 逻辑 0 indicates 那里 是 receive 数据 至 读/unload, i.e.,

receive 准备好 状态 和 一个 或者 更多 RX characters 有 在 这 先进先出/rhr. 这个

管脚 是 一个 逻辑 1 当 这 先进先出/rhr 是 empty 或者 当 这 编写程序 触发 水平的

有 不 被 reached. 这个 信号 能 也 是 使用 为 单独的 模式 transfers (dma

模式 0).

重置 21 I

重置 (起作用的-高).

一个 逻辑 1 在 这个 管脚 将 重置 这 内部的 寄存器 和 所有 这

输出. 这 uart 传输者 输出 和 这 接受者 输入 将 是 无能 在

重置 时间. (看 部分 7.11 “sc16c2552 外部 重置 conditions”为 initialization

详细信息.)

txrdya,

TXRDYB

1, 32 O

transmit 准备好 一个, b (起作用的-低).

这些 输出 提供 这 tx 先进先出/thr 状态

为 单独的 transmit 途径 (一个-b). txrdyn 是 primarily 将 为 monitoring

dma 模式 1 transfers 为 这 transmit 数据 fifos. 一个 单独的 频道’s

txrdya,

txrdyb 缓存区 准备好 状态 是 表明 用 逻辑 0, i.e., 在 least 一个 location 是 empty

和 有 在 这 先进先出 或者 thr. 这个 管脚 变得 至 一个 逻辑 1 当 那里 是 非 更多

empty locations 在 这 先进先出 或者 thr. 这个 信号 能 也 是 使用 为 单独的 模式

transfers (dma 模式 0).

V

CC

33, 44 I

电源 供应 输入.

XTAL1 11 I

结晶 或者 外部 时钟 输入.

功能 作 一个 结晶 输入 或者 作 一个 外部 时钟

输入. 一个 结晶 能 是 连接 在 这个 管脚 和 xtal2 至 表格 一个 内部的

振荡器 电路. alternatively, 一个 外部 时钟 能 是 连接 至 这个 管脚 至 提供

custom 数据 比率. (看 部分 6.5 “programmable 波特 比率 generator”.)

XTAL2 13 O

输出 的 这 结晶 振荡器 或者 缓冲 时钟.

(看 也 xtal1.) 结晶

振荡器 输出 或者 缓冲 时钟 输出. 应当 是 left 打开 如果 一个 外部 时钟 是

连接 至 xtal1.

cda, CDB 42, 30 I

运输车 发现 (起作用的-低).

这些 输入 是 有关联的 和 单独的 uart

途径 一个 通过 b. 一个 逻辑 0 在 这个 管脚 indicates 那 一个 运输车 有 被 发现 用

这 modem 为 那 频道.

表格 2: 管脚 描述

…continued

标识 管脚 类型 描述