4

ICS1522

电源-在 initialization

这

ICS1522

有 一个 内部的 电源-在 重置 电路 那

sets 这 频率 的 这 clk+and clk- 输出 至 是 half

这 结晶 或者 涉及 频率 假设 那 它们 是

在 10 mhz 和 25 mhz (谈及 至 default settings 在

寄存器 定义). 因为 这 电源-在 重置 电路 是

在 这 vdd 供应, 和 因为 那 供应 是 filtered,

小心 必须 是 带去 至 准许 这 重置 至 de-assert 在之前

程序编制. 一个 safe 指导原则 是 至 准许 20 microseconds

之后 这vdd 供应 reaches 四 伏特.

板 测试 支持

它 是 常常 desirable 至 statically 控制 这 水平 的 这

输出 管脚 为 电路 板 测试. 这

ICS1522

支持

这个 通过 一个 寄存器 可编程序的 模式, auxen. 当

这个 模式 是 设置, auxclk 将 直接地 控制 这 逻辑

水平 的 这 clk+ 和 clk- 管脚 当 omux1, omux2,

omux3, 和 omux4 将 控制 out1, out2, out3

和 out4, 各自.

电源 供应 和 解耦

The

ICS1522

有 三

VSS

管脚 至 减少 这 影响 的

包装 电感. 两个都 管脚 是 连接 至 这 一样

潜在的 在 这 消逝 (这 地面 总线). 这些 管脚 应当

连接 至 这 地面 平面 的 这 video 板 作 关闭 至

这 包装 作 是 可能.

这

ICS1522

有 一个

VDDO

管脚 这个 是 这 供应 的 +5

volt 电源 至 所有 输出 驱动器. 这个 管脚 应当 是 连接

至 这 电源 平面 (或者 总线) 使用 标准 高-频率

解耦 实践. 那 是, 电容 应当 有 低

序列 电感 和 是 挂载 关闭 至 这

ICS1522

.

这

VDD

管脚 是 这 电源 supply 管脚 为 这 pll synthesizer

电路系统 和 其它 更小的 电流 digital 功能. 我们

推荐 那 rc 解耦 或者 齐纳 规章制度 是

提供 为 这个 管脚 (作 显示 在 这 推荐

应用 电路系统). 这个 将 准许 这 pll 至 “track”

通过 电源 供应 fluctuations 没有 visible 影响.

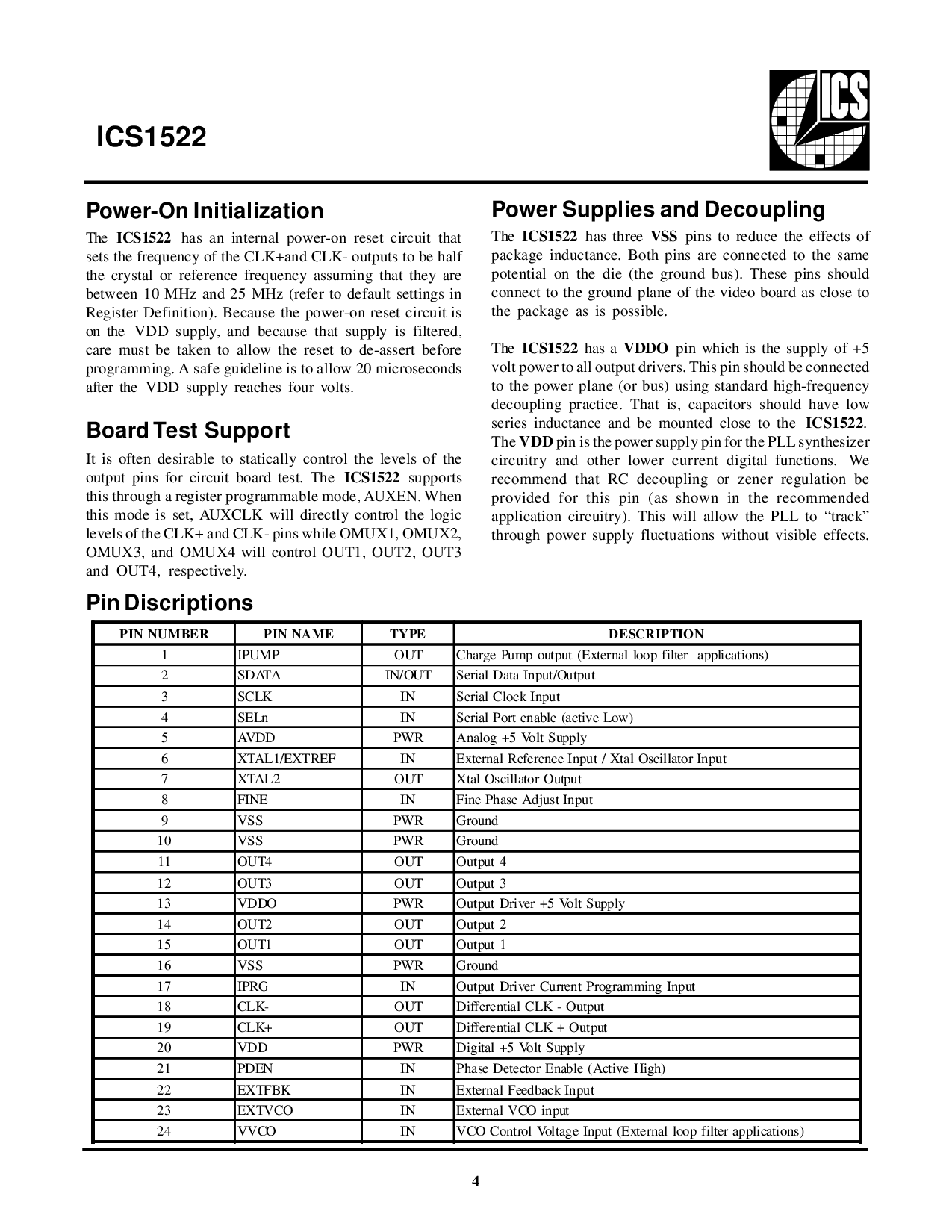

管脚 号码 管脚 名字 类型 描述

1 IPUMP 输出 承担 打气 输出 (外部 循环 过滤 产品)

2 SDATA 在/输出 串行 数据 输入/输出

3 SCLK 在 串行 时钟 输入

4 SELn 在 串行 端口 使能 (起作用的 低)

5 AVDD PWR 相似物 +5 volt 供应

6 xtal1/extref 在 外部 涉及 输入 / xtal 振荡器 输入

7 XTAL2 输出 xtal 振荡器 输出

8 FINE 在 fine 阶段 调整 输入

9 VSS PWR 地面

10 VSS PWR 地面

11 OUT4 输出 输出 4

12 OUT3 输出 输出 3

13 VDDO PWR 输出 驱动器 +5 volt 供应

14 OUT2 输出 输出 2

15 OUT1 输出 输出 1

16 VSS PWR 地面

17 IPRG 在 输出 驱动器 电流 程序编制 输入

18 clk- 输出 差别的 clk - 输出

19 CLK+ 输出 差别的 clk + 输出

20 VDD PWR 数字的 +5 volt 供应

21 PDEN 在 阶段 探测器 使能 (起作用的 高)

22 EXTFBK 在 外部 反馈 输入

23 EXTVCO 在 外部 vco 输入

24 VVCO 在 vco 控制 电压 输入 (外部 循环 过滤 产品)

管脚 discriptions