sn65lv1023a/sn65lv1224a

10-mhz 至 66-mhz, 10:1 lvds serializer/deserializer

SLLS570A

–

六月 2003

–

修订 六月 2003

6

邮递 办公室 盒 655303

•

达拉斯市, 德州 75265

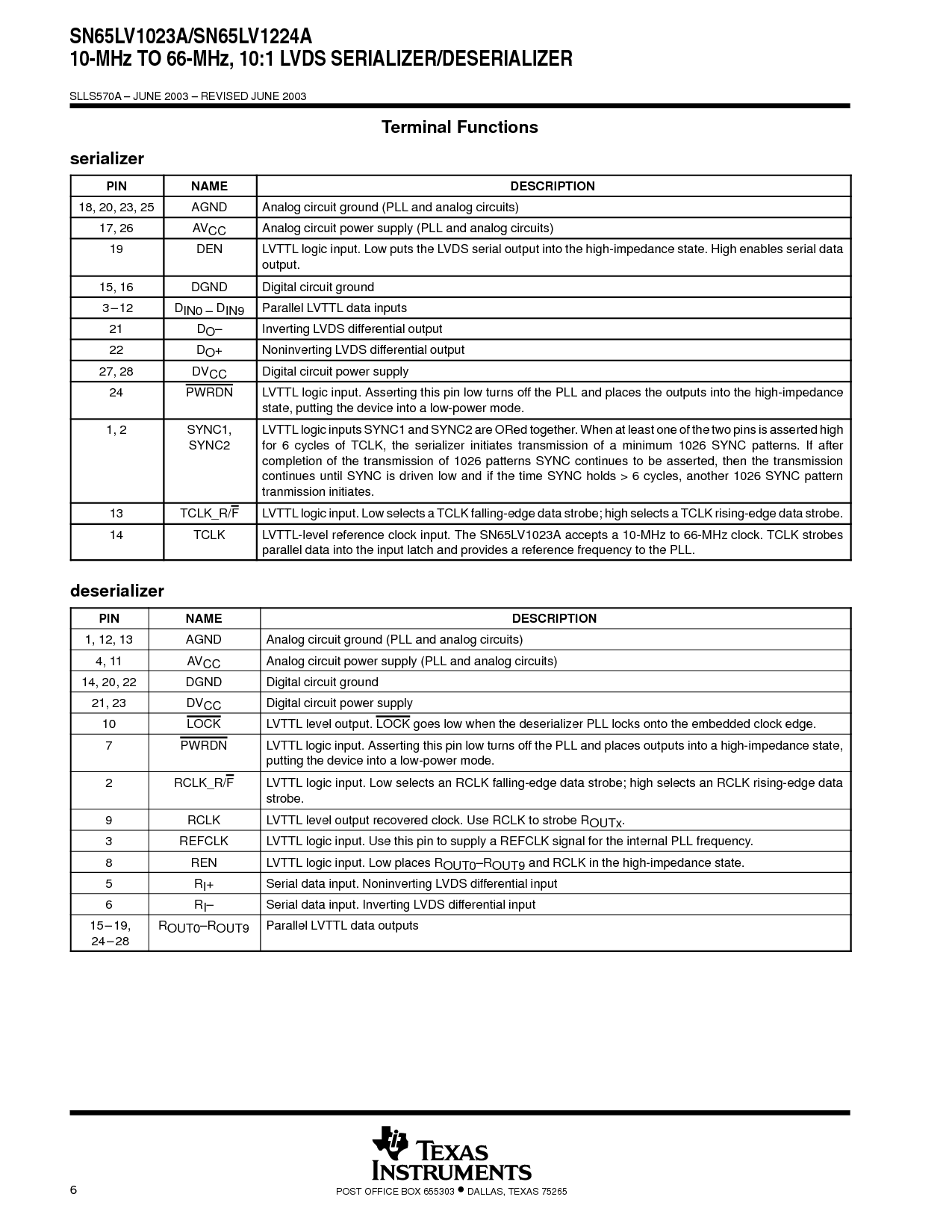

终端 功能

serializer

管脚 名字 描述

18, 20, 23, 25 AGND 相似物 电路 地面 (pll 和 相似物 电路)

17, 26 AV

CC

相似物 电路 电源 供应 (pll 和 相似物 电路)

19 DEN lvttl 逻辑 输入. 低 puts 这 lvds 串行 输出 在 这 高-阻抗 状态. 高 使能 串行 数据

输出.

15, 16 DGND 数字的 电路 地面

3

–

12 D

IN0

–

D

IN9

并行的 lvttl 数据 输入

21 D

O

–

反相的 lvds 差别的 输出

22 D

O

+ 同相 lvds 差别的 输出

27, 28 DV

CC

数字的 电路 电源 供应

24 PWRDN lvttl 逻辑 输入. asserting 这个 管脚 低 转变 止 这 pll 和 places 这 输出 在 这 高-阻抗

状态, putting 这 设备 在 一个 低-电源 模式.

1, 2 sync1,

SYNC2

lvttl 逻辑 输入 sync1 和 sync2 是 ored 一起. 当 在 least 一个 的 这 二 管脚 是 asserted 高

为 6 循环 的 tclk, 这 serializer initiates 传递 的 一个 最小 1026 同步 patterns. 如果 之后

completion 的 这 传递 的 1026 patterns 同步 持续 至 是 asserted, 然后 这 传递

持续 直到 同步 是 驱动 低 和 如果 这 时间 同步 holds > 6 循环, 另一 1026 同步 模式

tranmission initiates.

13 tclk_r/f lvttl 逻辑 输入. 低 选择 一个 tclk 下落-边缘 数据 strobe; 高 选择 一个 tclk rising-边缘 数据 strobe.

14 TCLK lvttl-水平的 涉及 时钟 输入. 这 sn65lv1023a accepts 一个 10-mhz 至 66-mhz clock. tclk strobes

并行的 数据 在 这 输入 获得 和 提供 一个 涉及 频率 至 这 pll.

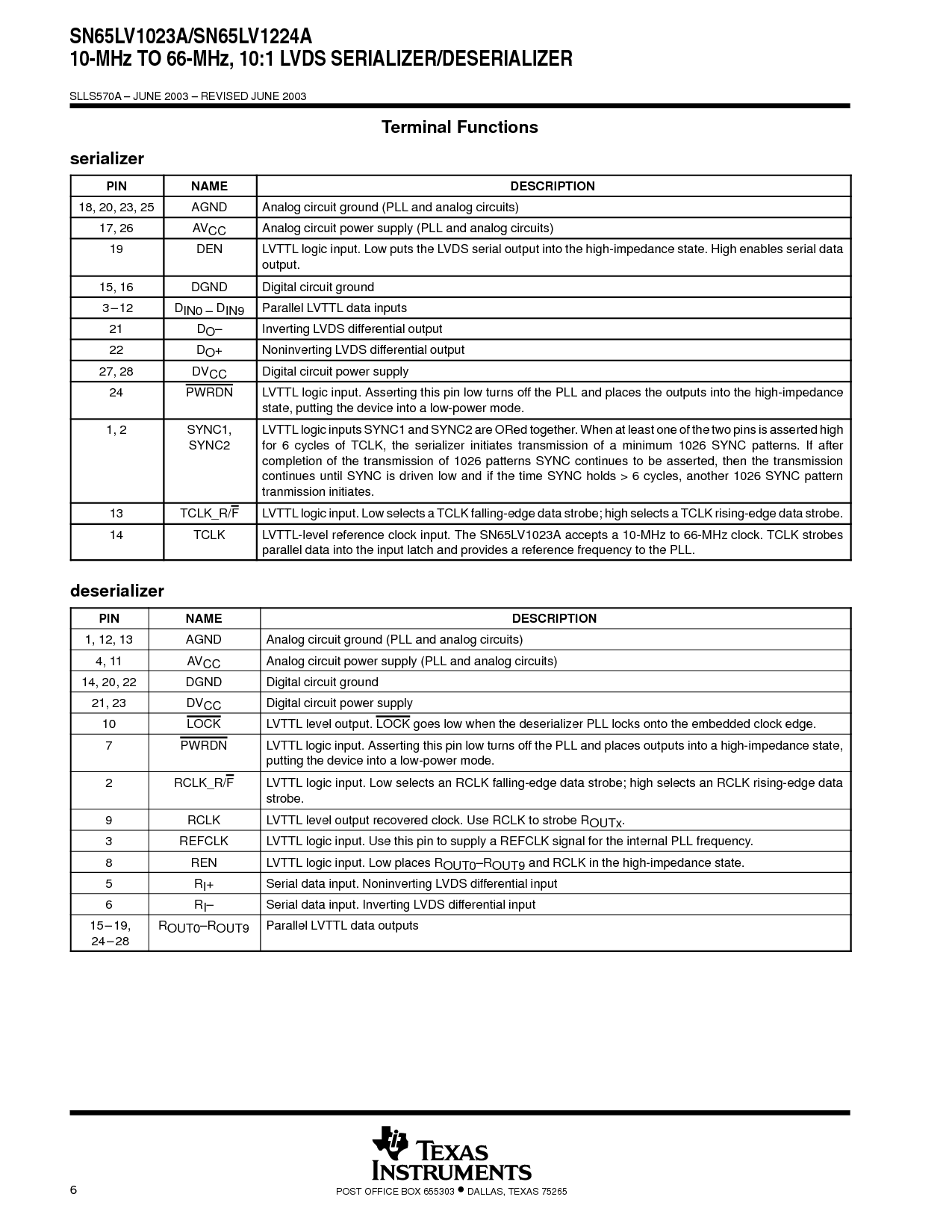

deserializer

管脚 名字 描述

1, 12, 13 AGND 相似物 电路 地面 (pll 和 相似物 电路)

4, 11 AV

CC

相似物 电路 电源 供应 (pll 和 相似物 电路)

14, 20, 22 DGND 数字的 电路 地面

21, 23 DV

CC

数字的 电路 电源 供应

10 锁 lvttl 水平的 输出. 锁变得 低 当 这 deserializer pll locks 面向 这 embedded 时钟 边缘.

7 PWRDN lvttl 逻辑 输入. asserting 这个 管脚 低 转变 止 这 pll 和 places 输出 在 一个 高-阻抗 状态,

putting 这 设备 在 一个 低-电源 模式.

2 rclk_r/f lvttl 逻辑 输入. 低 选择 一个 rclk 下落-边缘 数据 strobe; 高 选择 一个 rclk rising-边缘 数据

strobe.

9 RCLK lvttl 水平的 输出 recovered 时钟. 使用 rclk 至 strobe r

OUTx

.

3 REFCLK lvttl 逻辑 输入. 使用 这个 管脚 至 供应 一个 refclk 信号 为 这 内部的 pll 频率.

8 REN lvttl 逻辑 输入. 低 places r

OUT0

–

R

OUT9

和 rclk 在 这 高-阻抗 状态.

5 R

I

+ 串行 数据 输入. 同相 lvds 差别的 输入

6 R

I

–

串行 数据 输入. 反相的 lvds 差别的 输入

15

–

19,

24

–

28

R

OUT0

–

R

OUT9

并行的 lvttl 数据 输出