L1

ëðììè

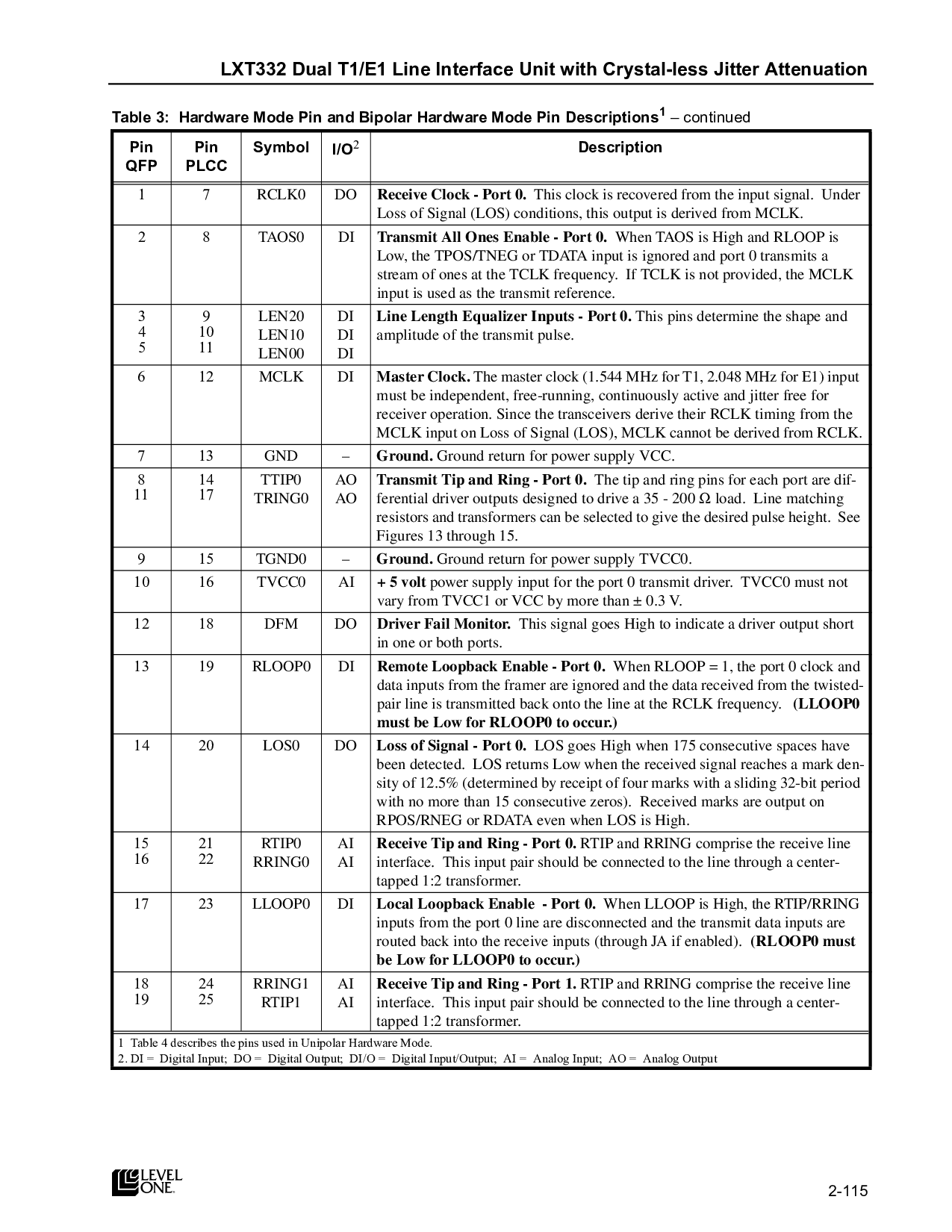

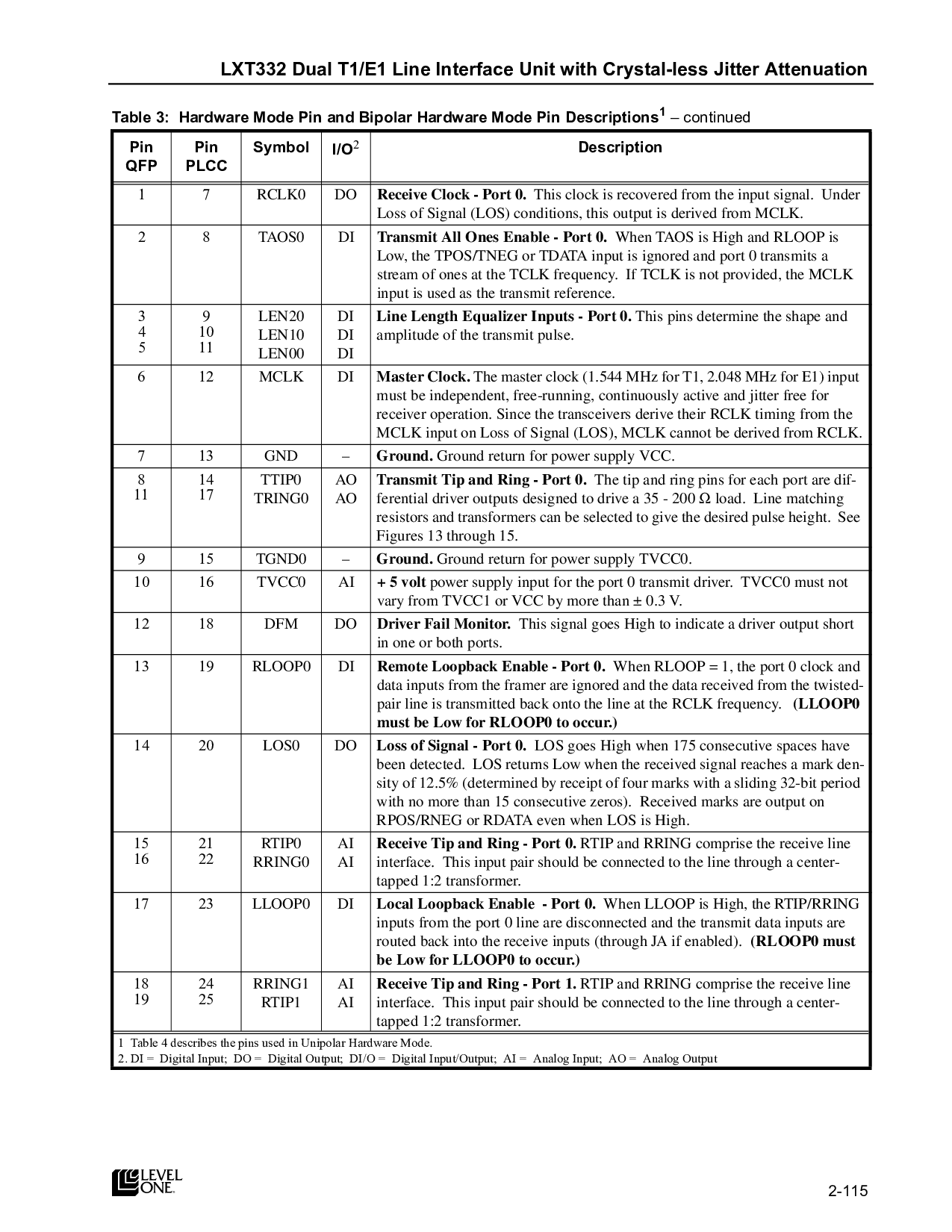

/;7êêë 'xdo 7ìî(ì /lqh ,qwhuidfh 8QLW ZLWK &放大;u\vwdoðohvv -lwwhu $WWHQXDWLRQ

ìæ

RCLK0 做

receive 时钟 - 端口 0.

这个 时钟 是 recovered 从 这 输入 信号. 下面

丧失 的 信号 (los) 情况, 这个 输出 是 获得 从 mclk.

ëå

TAOS0 DI

transmit 所有 ones 使能 - 端口 0.

当 taos 是 高 和 rloop 是

低, 这 tpos/tneg 或者 tdata 输入 是 ignored 和 端口 0 transmits 一个

stream 的 ones 在 这 tclk 频率. 如果 tclk 是 不 提供, 这 mclk

输入 是 使用 作 这 transmit 涉及.

ê

é

è

ä

ìí

ìì

LEN20

LEN10

LEN00

DI

DI

DI

线条 长度 equalizer 输入 - 端口 0.

这个 管脚 决定 这 shape 和

振幅 的 这 transmit 脉冲波.

çìë

MCLK DI

主控 时钟.

这 主控 时钟 (1.544 mhz 为 t1, 2.048 mhz 为 e1) 输入

必须 是 独立, 自由-运动, continuously 起作用的 和 jitter 自由 为

接受者 运作. 自从 这 transceivers derive 它们的 rclk 定时 从 这

mclk 输入 在 丧失 的 信号 (los), mclk 不能 是 获得 从 rclk.

æìê

地 –

地面.

地面 返回 为 电源 供应 vcc.

å

ìì

ìé

ìæ

TTIP0

TRING0

AO

AO

transmit tip 和 环绕 - 端口 0.

这 tip 和 环绕 管脚 为 各自 端口 是 dif-

ferential 驱动器 输出 设计 至 驱动 一个 35 - 200

Ω

加载. 线条 相一致

电阻器 和 transformers 能 是 选择 至 给 这 desired 脉冲波 height. 看

计算数量 13 通过 15.

äìè

TGND0 –

地面.

地面 返回 为 电源 供应 tvcc0.

ìí ìç

TVCC0 AI

+ 5 volt

电源 供应 输入 为 这 端口 0 transmit 驱动器. tvcc0 必须 不

相异 从 tvcc1 或者 vcc 用 更多 比 ± 0.3 v.

ìë ìå

DFM 做

驱动器 失败 监控.

这个 信号 变得 高 至 表明 一个 驱动器 输出 短的

在 一个 或者 两个都 端口.

ìê ìä

RLOOP0 DI

偏远的 loopback 使能 - 端口 0.

当 rloop = 1, 这 端口 0 时钟 和

数据 输入 从 这 framer 是 ignored 和 这 数据 received 从 这 twisted-

一双 线条 是 transmitted 后面的 面向 这 线条 在 这 rclk 频率.

(lloop0

必须 是 低 为 rloop0 至 出现.)

ìé ëí

LOS0 做

丧失 的 信号 - 端口 0.

los 变得 高 当 175 consecutive spaces 有

被 发现. los returns 低 当 这 received 信号 reaches 一个 mark den-

sity 的 12.5% (决定 用 receipt 的 四 marks 和 一个 sliding 32-位 时期

和 非 更多 比 15 consecutive zeros). received marks 是 输出 在

rpos/rneg 或者 rdata 甚至 当 los 是 高.

ìè

ìç

ëì

ëë

RTIP0

RRING0

AI

AI

receive tip 和 环绕 - 端口 0.

rtip 和 rring comprise 这 receive 线条

接口. 这个 输入 一双 应当 是 连接 至 这 线条 通过 一个 中心-

抽头的 1:2 变压器.

ìæ ëê

LLOOP0 DI

local loopback 使能 - 端口 0.

当 lloop 是 高, 这 rtip/rring

输入 从 这 端口 0 线条 是 disconnected 和 这 transmit 数据 输入 是

routed 后面的 在 这 receive 输入 (通过 ja 如果 使能).

(rloop0 必须

是 低 为 lloop0 至 出现.)

ìå

ìä

ëé

ëè

RRING1

RTIP1

AI

AI

receive tip 和 环绕 - 端口 1.

rtip 和 rring comprise 这 receive 线条

接口. 这个 输入 一双 应当 是 连接 至 这 线条 通过 一个 中心-

抽头的 1:2 变压器.

7DEOH êã +DUGZDUH 0RGH 3LQ DQG %LSRODU +DUGZDUH 0RGH 3LQ 'hvfulswlrqv

ì

¤ FRQWLQXHG

3LQ

4)3

3LQ

3/&放大;&放大;

6\PERO

,î2

ë

'hvfulswlrq

ì 7DEOH é GHVFULEHV WKH SLQV XVHG LQ 8QLSRODU +DUGZDUH 0RGHï

ëï ', 'ljlwdo ,qsxwâ '2 'ljlwdo 2XWSXWâ ',î2 'ljlwdo ,qsxwî2xwsxwâ $, $QDORJ ,qsxwâ $2 $QDORJ 2XWSXW