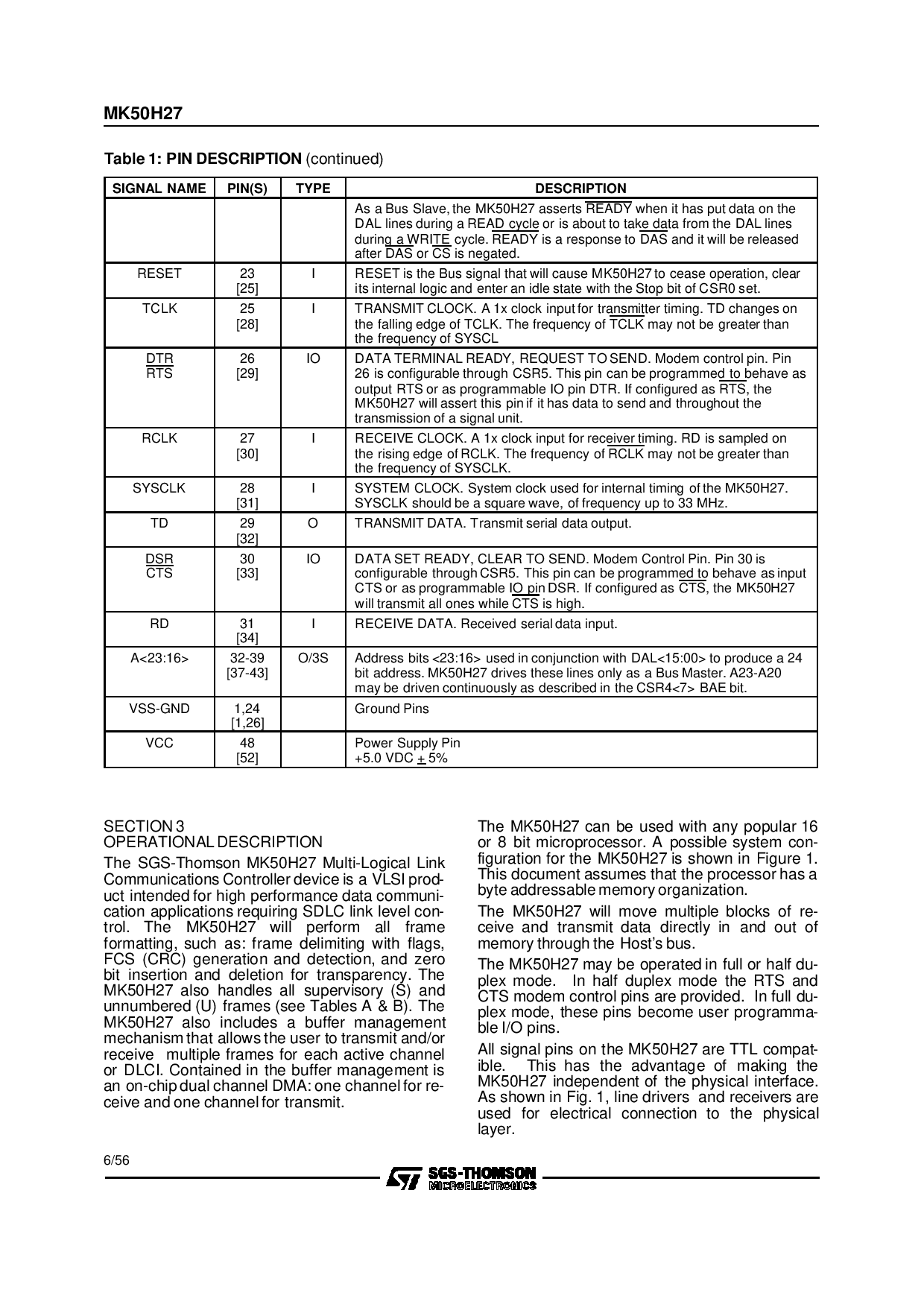

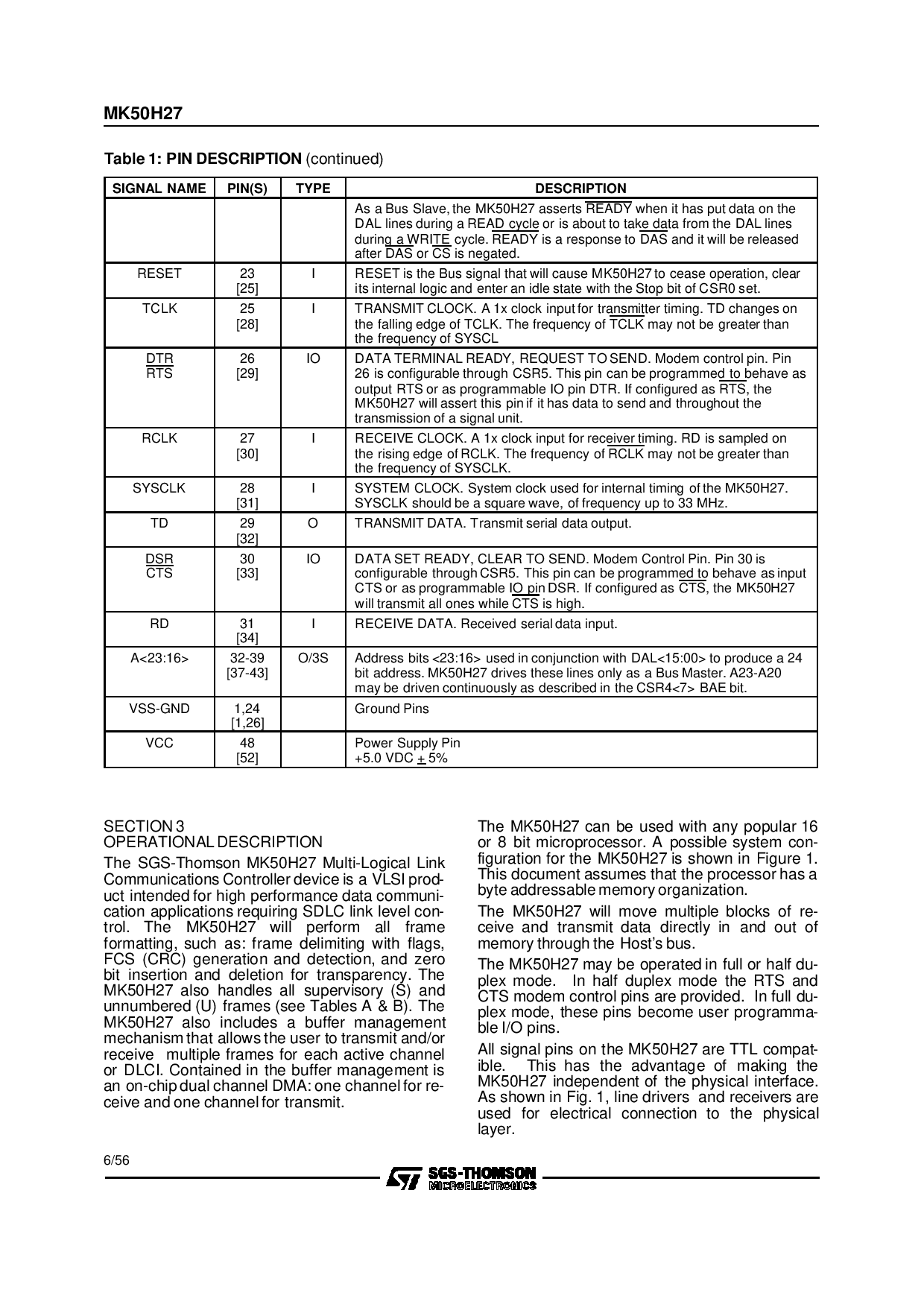

表格 1: 管脚 描述

(持续)

信号 名字 管脚(s) 类型 描述

作 一个 总线 从动装置, 这 MK50H27 asserts 准备好 当 它 有 放 数据 在 这

DAL 线条 在 一个 读 循环 或者 是 关于 至 引领 数据 从 这 DAL 线条

在 一个 写 循环. 准备好 是 一个 回馈 至 DAS 和 它 将 是 released

之后 DAS 或者 CS 是 negated.

重置 23

[25]

I 重置 是 这 总线 信号 那 将 导致 MK50H27 至 cease 运作, clear

它的 内部的 逻辑 和 enter 一个 空闲 状态 和 这 停止 位 的 CSR0 设置.

TCLK 25

[28]

I TRANSMIT 时钟. 一个 1x 时钟 输入 为 传输者 定时. TD 改变 在

这 下落 边缘 的 tclk. 这 频率 的 TCLK 将 不 是 更好 比

这 频率 的 SYSCL

DTR

RTS

26

[29]

IO 数据 终端 准备好, 要求 至 send. Modem 控制 管脚. 管脚

26 是 configurable 通过 csr5. 这个 管脚 能 是 编写程序 至 behave 作

输出 RTS 或者 作 可编程序的 IO 管脚 dtr. 如果 配置 作 rts, 这

MK50H27 将 assert 这个 管脚 如果 它 有 数据 至 send 和 全部地 这

transmission 的 一个 信号 单位.

RCLK 27

[30]

I RECEIVE 时钟. 一个 1x 时钟 输入 为 接受者 定时. RD 是 抽样 在

这 rising 边缘 的 rclk. 这 频率 的 RCLK 将 不 是 更好 比

这 频率 的 sysclk.

SYSCLK 28

[31]

I 系统 时钟. 系统 时钟 使用 为 内部的 定时 的 这 mk50h27.

SYSCLK 应当 是 一个 正方形的 波, 的 频率 向上 至 33 mhz.

TD 29

[32]

O TRANSMIT 数据. Transmit 串行 数据 输出.

DSR

CTS

30

[33]

IO 数据 设置 准备好, CLEAR 至 send. Modem 控制 管脚. 管脚 30 是

configurable 通过 csr5. 这个 管脚 能 是 编写程序 至 behave 作 输入

CTS 或者 作 可编程序的 IO 管脚 dsr. 如果 配置 作 cts, 这 MK50H27

将 transmit 所有 ones 当 CTS 是 高.

RD 31

[34]

I RECEIVE 数据. Received 串行 数据 输入.

一个<23:16> 32-39

[37-43]

o/3s 地址 位 <23:16> 使用 在 conjunction 和 dal<15:00> 至 生产 一个 24

位 地址. MK50H27 驱动 这些 线条 仅有的 作 一个 总线 主控. a23-a20

将 是 驱动 continuously 作 描述 在 这 csr4<7> BAE 位.

vss-地 1,24

[1,26]

Ground 管脚

VCC 48

[52]

电源 供应 管脚

+5.0 VDC + 5%

部分 3

运算的 描述

这 sgs-thomson MK50H27 multi-logical Link

Communications 控制 设备 是 一个 VLSI prod-

uct 将 为 高 效能 数据 communi-

cation 产品 需要 SDLC link 水平的 con-

trol. 这 MK50H27 将 执行 所有 框架

formatting, 此类 作: 框架 delimiting 和 flags,

FCS (crc) 一代 和 发现, 和 零

位 嵌入 和 deletion 为 transparency. 这

MK50H27 也 handles 所有 supervisory (s) 和

unnumbered (u) frames (看 Tables 一个 &放大; b). 这

MK50H27 也 包含 一个 缓存区 管理

mechanism 那 准许 这 用户 至 transmit 和/或者

receive 多样的 frames 为 各自 起作用的 频道

或者 dlci. 包含 在 这 缓存区 管理 是

一个 在-碎片 双 频道 dma: 一个 频道 为 re-

ceive 和 一个 频道 为 transmit.

这 MK50H27 能 是 使用 和 任何 popular 16

或者 8 位 微处理器. 一个 可能 系统 con-

figuration 为 这 MK50H27 是 显示 在 图示 1.

这个 文档 假设 那 这 处理器 有 一个

字节 addressable 记忆 organization.

这 MK50H27 将 move 多样的 blocks 的 re-

ceive 和 transmit 数据 直接地 在 和 输出 的

记忆 通过 这 Host’s 总线.

这 MK50H27 将 是 运作 在 全部 或者 half du-

plex 模式. 在 half duplex 模式 这 RTS 和

CTS modem 控制 管脚 是 提供. 在 全部 du-

plex 模式, 这些 管脚 变为 用户 programma-

ble i/o 管脚.

所有 信号 管脚 在 这 MK50H27 是 TTL compat-

ible. 这个 有 这 advantage 的 制造 这

MK50H27 独立 的 这 物理的 接口.

作 显示 在 图. 1, 线条 驱动器 和 接受者 是

使用 为 电的 连接 至 这 物理的

layer.

MK50H27

6/56