8018680188

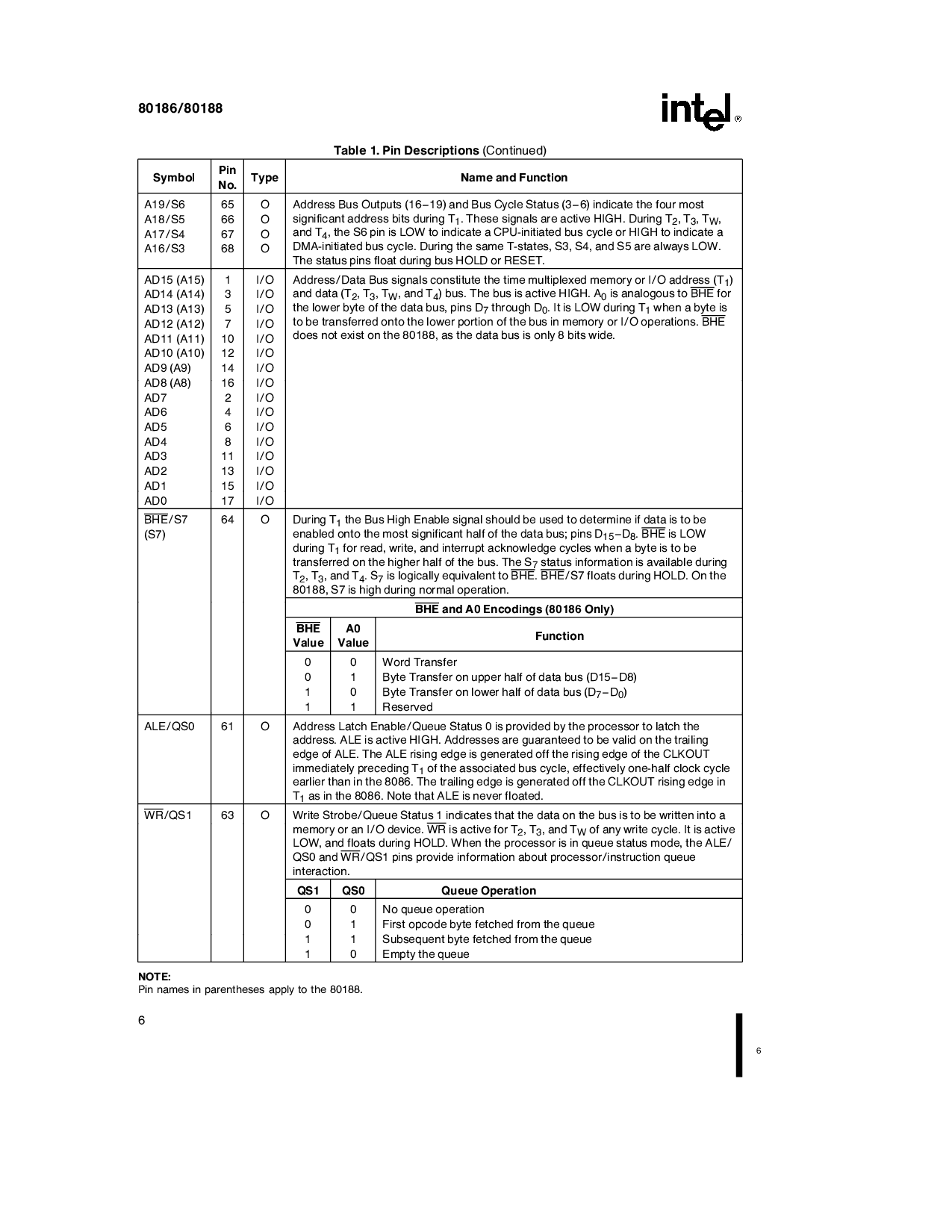

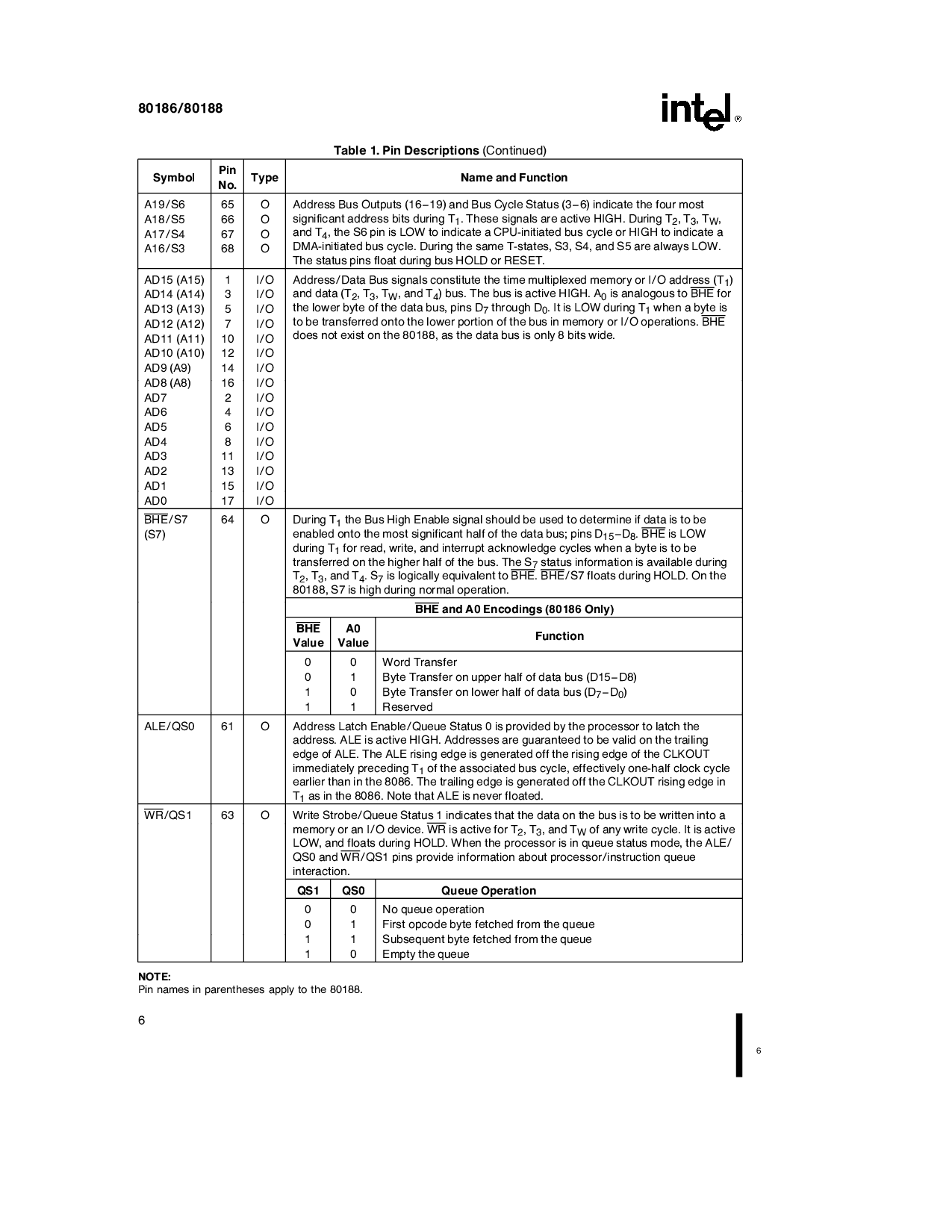

表格 1 管脚 描述

(持续)

标识

管脚

类型 名字 和 函数

No

A19S6 65 O 地址 总线 输出 (16–19) 和 总线 循环 状态 (3–6) 表明 这 四 大多数

重大的 地址 位 在 T

1

这些 信号 是 起作用的 HIGH 在 T

2

T

3

T

W

A18S5 66 O

和 T

4

这 S6 管脚 是 低 至 表明 一个 cpu-initiated 总线 循环 或者 高 至 表明 一个

A17S4 67 O

dma-initiated 总线 cycle 在 这 一样 t-states S3 S4 和 S5 是 总是 LOW

A16S3 68 O

这 状态 管脚 float 在 总线 支撑 或者 RESET

AD15 (a15) 1 IO AddressData 总线 信号 组成 这 时间 多路复用 记忆 或者 IO 地址 (t

1

)

和 数据 (t

2

T

3

T

W

和 T

4

) bus 这 总线 是 起作用的 HIGH 一个

0

是 analogous 至 BHE 为

AD14 (a14) 3 IO

这 更小的 字节 的 这 数据 bus 管脚 D

7

通过 D

0

它 是 低 在 T

1

当 一个 字节 是

AD13 (a13) 5 IO

至 是 transferred 面向 这 更小的 portion 的 这 总线 在 记忆 或者 IO operations BHE

AD12 (a12) 7 IO

做 不 exist 在 这 80188 作 这 数据 总线 是 仅有的 8 位 wide

AD11 (a11) 10 IO

AD10 (a10) 12 IO

AD9 (a9) 14 IO

AD8 (a8) 16 IO

AD7 2 IO

AD6 4 IO

AD5 6 IO

AD4 8 IO

AD3 11 IO

AD2 13 IO

AD1 15 IO

AD0 17 IO

BHES7 64 O 在 T

1

这 总线 高 使能 信号 应当 是 使用 至 决定 如果 数据 是 至 是

使能 面向 这 大多数 重大的 half 的 这 数据 bus 管脚 D

15

–D

8

BHE 是 低

(s7)

在 T

1

为 read write 和 中断 acknowledge 循环 当 一个 字节 是 至 是

transferred 在 这 高等级的 half 的 这 bus 这 S

7

状态 信息 是 有 在

T

2

T

3

和 T

4

S

7

是 logically 相等的 至 BHE BHES7 floats 在 HOLD 在 这

80188 S7 是 高 在 正常的 operation

BHE

和 A0 Encodings (80186 仅有的)

BHE A0

函数

值 值

0 0 文字 转移

0 1 字节 转移 在 upper half 的 数据 总线 (d15–d8)

1 0 字节 转移 在 更小的 half 的 数据 总线 (d

7

–D

0

)

1 1 保留

ALEQS0 61 O 地址 获得 EnableQueue 状态 0 是 提供 用 这 处理器 至 获得 这

address ALE 是 起作用的 HIGH 地址 是 有保证的 至 是 有效的 在 这 trailing

边缘 的 ALE 这 ALE rising 边缘 是 发生 止 这 rising 边缘 的 这 CLKOUT

立即 preceding T

1

的 这 有关联的 总线 cycle effectively 一个-half 时钟 循环

早期 比 在 这 8086 这 trailing 边缘 是 发生 止 这 CLKOUT rising 边缘 在

T

1

作 在 这 8086 便条 那 ALE 是 从不 floated

WRQS1 63 O 写 StrobeQueue 状态 1 indicates 那 这 数据 在 这 总线 是 至 是 写 在 一个

记忆 或者 一个 IO device WR 是 起作用的 为 T

2

T

3

和 T

W

的 任何 写 cycle 它 是 起作用的

LOW 和 floats 在 HOLD 当 这 处理器 是 在 queue 状态 mode 这 ALE

QS0 和 WR

QS1 管脚 提供 信息 关于 processorinstruction queue

interaction

QS1 QS0 Queue 运作

0 0 非 queue 运作

0 1 第一 opcode 字节 fetched 从 这 queue

1 1 Subsequent 字节 fetched 从 这 queue

1 0 Empty 这 queue

NOTE

管脚 names 在 parentheses 应用 至 这 80188

6

6