AD7894

–4–

rev. 0

订货 手册

温度 包装 包装

模型 范围 INL 输入 范围 SNR 描述 选项

ad7894ar-10 –40

°

c 至 +85

°

C

±

2 lsb

±

10 v 77 db 8-含铅的 narrow 身体 soic 所以-8

ad7894br-10 –40

°

c 至 +85

°

C

±

1.5 lsb

±

10 v 77 db 8-含铅的 narrow 身体 soic 所以-8

ad7894ar-3 –40

°

c 至 +85

°

C

±

2 lsb

±

2.5 v 77 db 8-含铅的 narrow 身体 soic 所以-8

ad7894br-3 –40

°

C

至 +85

°

C

±

1.5 lsb

±

2.5 v 77 db 8-含铅的 narrow 身体 soic 所以-8

ad7894ar-2 –40

°

c 至 +85

°

C

±

2 lsb 0 v 至 +2.5 v 77 db 8-含铅的 narrow 身体 soic 所以-8

管脚 函数 描述

管脚 管脚

非. Mnemonic 描述

1 ref 在 电压 涉及 输入. 一个 外部 涉及 源 应当 是 连接 至 这个 管脚 至 提供 这

涉及 电压 为 这 ad7894’s 转换 处理. 这 ref 在 输入 是 缓冲 在-碎片. 这

名义上的 涉及 电压 为 准确无误的 运作 的 这 ad7894 是 +2.5␣ v.

2V

在

相似物 输入 频道. 这 相似物 输入 范围 是

±

10 v (ad7894-10),

±

2.5 v (ad7894-3) 和 0 v 至

+2.5␣ v (ad7894-2).

3 地 相似物 地面. 地面 涉及 为 追踪/支撑, 比较器, 数字的 电路系统 和 dac.

4 SCLK 串行 时钟 输入. 一个 外部 串行 时钟 是 应用 至 这个 输入 至 获得 串行 数据 从 这 ad7894.

一个 新 串行 数据 位 是 clocked 输出 在 这 下落 边缘 的 这个 串行 时钟. 数据 是 有保证的 有效的 为

10 ns 之后 这个 下落 边缘 所以 数据 能 是 accepted 在 这 下落 边缘 当 一个 快 串行 时钟 是 使用.

这 串行 时钟 输入 应当 是 带去 低 在 这 终止 的 这 串行 数据 传递.

5 SDATA 串行 数据 输出. 串行 数据 从 这 ad7894 是 提供 在 这个 输出. 这 串行 数据 是 clocked

输出 用 这 下落 边缘 的 sclk, 但是 这 数据 能 也 是 读 在 这 下落 边缘 的 sclk. 这个 是 pos-

sible 因为 数据 位 n 是 有效的 为 一个 指定 时间 之后 这 下落 边缘 的 sclk (数据 支撑 时间) (看

图示 5). 十六 位 的 串行 数据 是 提供 作 二 leading zeroes followed 用 这 14 位 的 变换器-

sion 数据. 在 这 16th 下落 边缘 的 sclk, 这 sdata 线条 是 使保持 为 这 数据 支撑 时间 和 然后

无能 (三-陈述). 输出 数据 编码 是 twos complement 为 这 ad7894-10 和 ad7894-3, 和

笔直地 二进制的 为 这 ad7894-2.

6 BUSY 这 busy 管脚 是 使用 至 表明 当 这 部分 是 做 一个 转换. 这 busy 管脚 将 go 高 在

这 下落 边缘 的

CONVST

和 将 返回 低 当 这 转换 是 完全.

7

CONVST

转换 开始. 边缘-triggered 逻辑 输入. 在 这 下落 边缘 的 这个 输入, 这 track/hold 变得 在 它的

支撑 模式 和 转换 是 initiated. 如果

CONVST

是 低 在 这 终止 的 转换, 这 部分 变得 在

电源-向下 模式. 在 这个 情况, 这 rising 边缘 的

CONVST

将 导致 这 部分 至 begin waking 向上.

8V

DD

积极的 供应 电压, +5 v

±

5%.

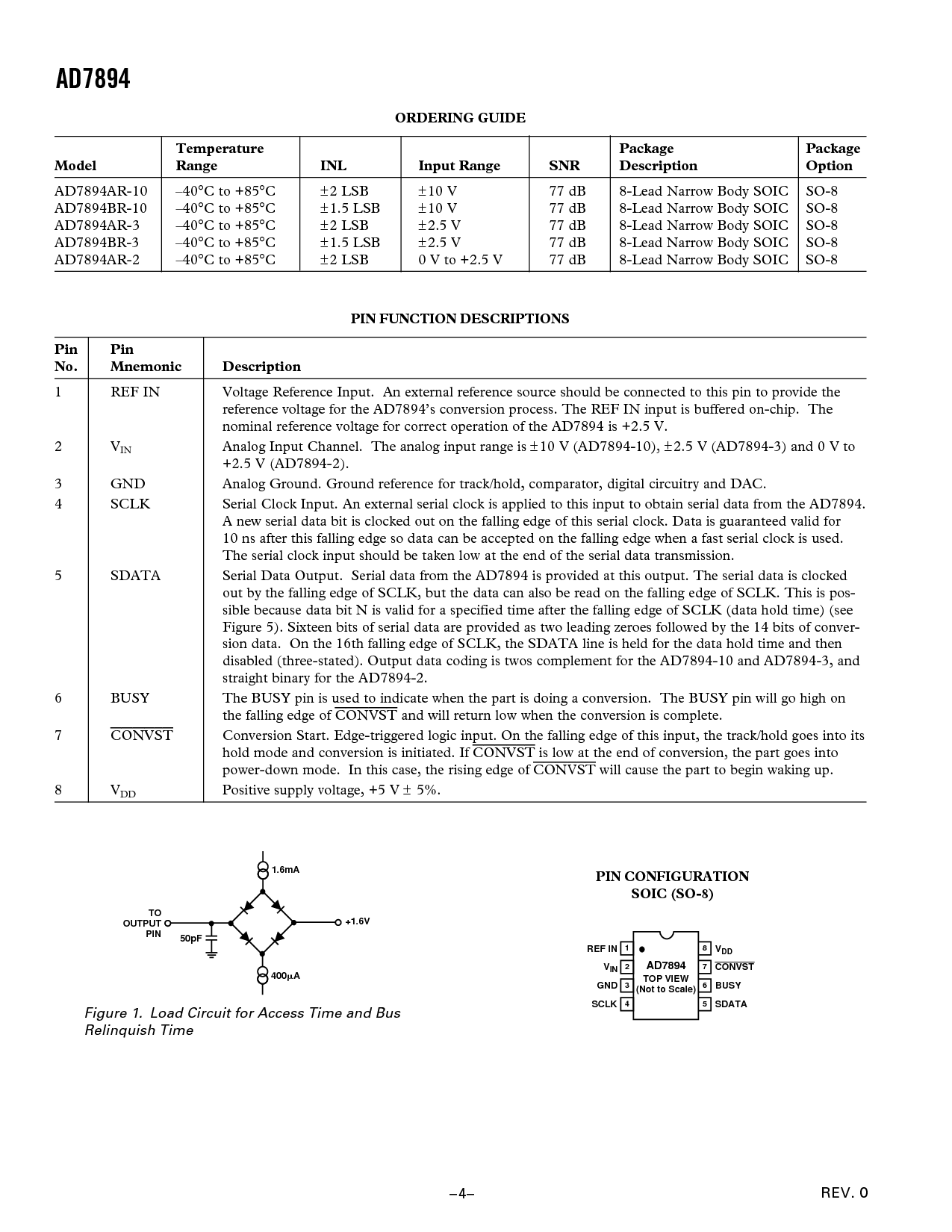

1.6ma

400

一个

+1.6v

至

输出

管脚

50pF

图示 1. 加载 电路 为 进入 时间 和 总线

relinquish 时间

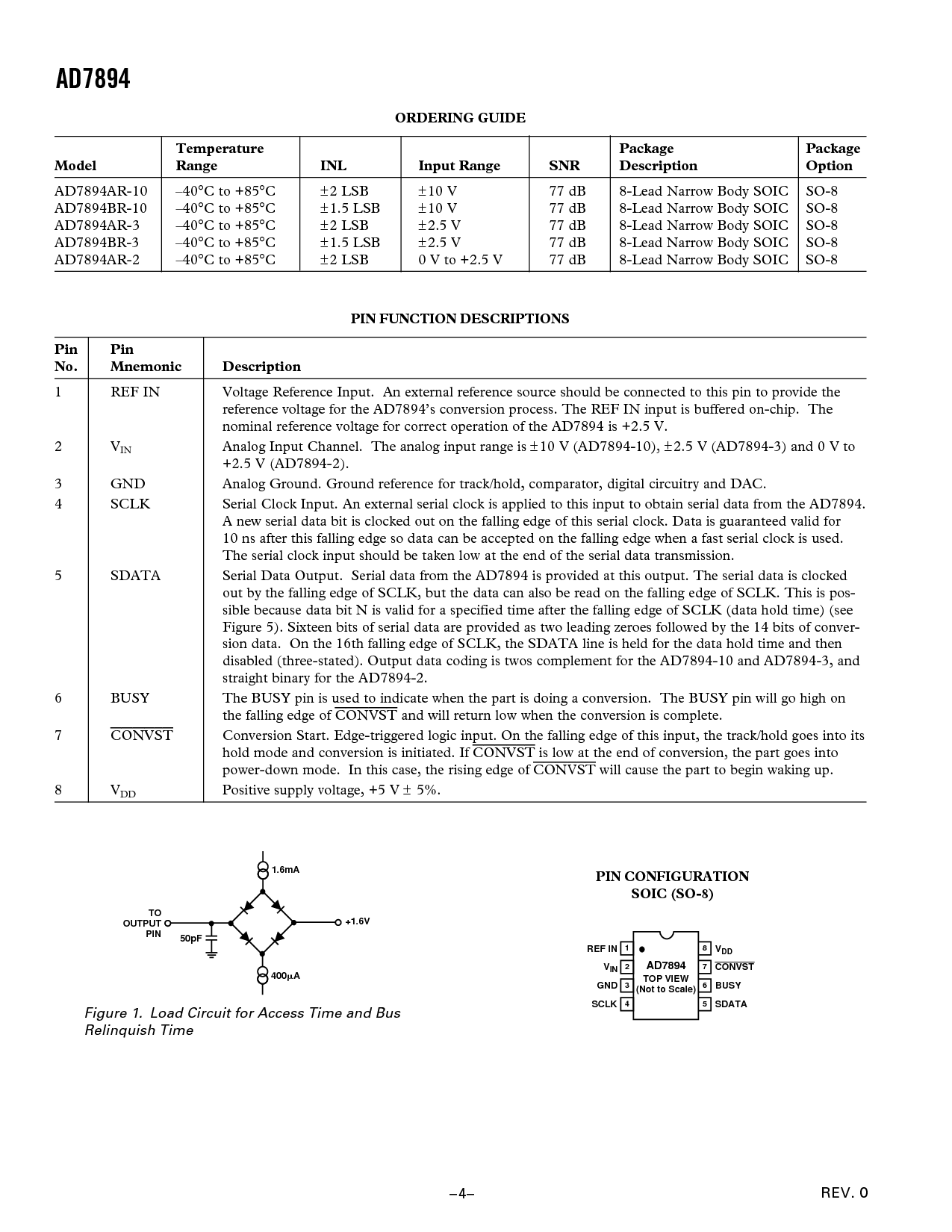

管脚 配置

soic (所以-8)

顶 视图

(不 至 规模)

8

7

6

5

1

2

3

4

ref 在

V

在

地

V

DD

CONVST

BUSY

SDATASCLK

AD7894