sbas323d −六月 2004 − 修订 九月 2005

www.德州仪器.com

9

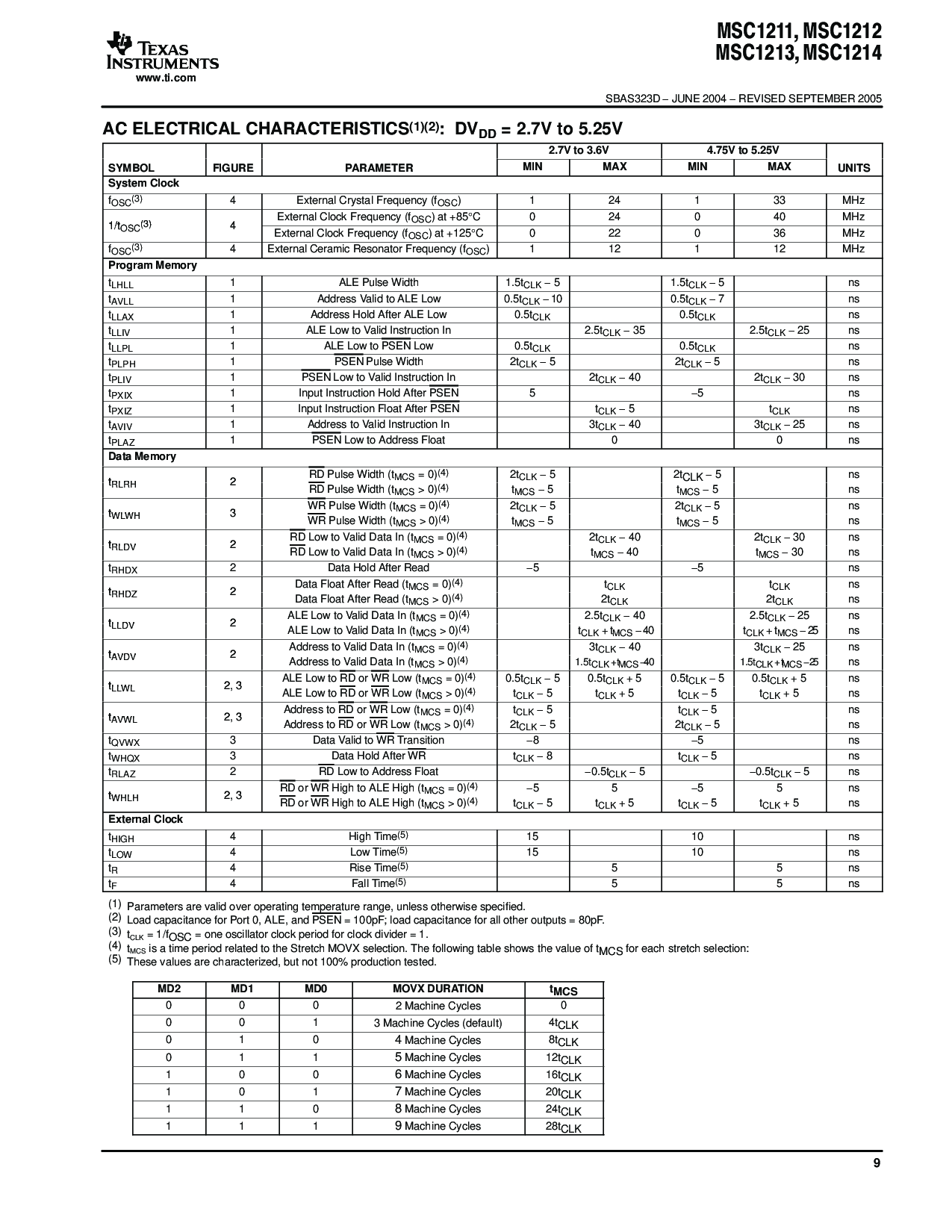

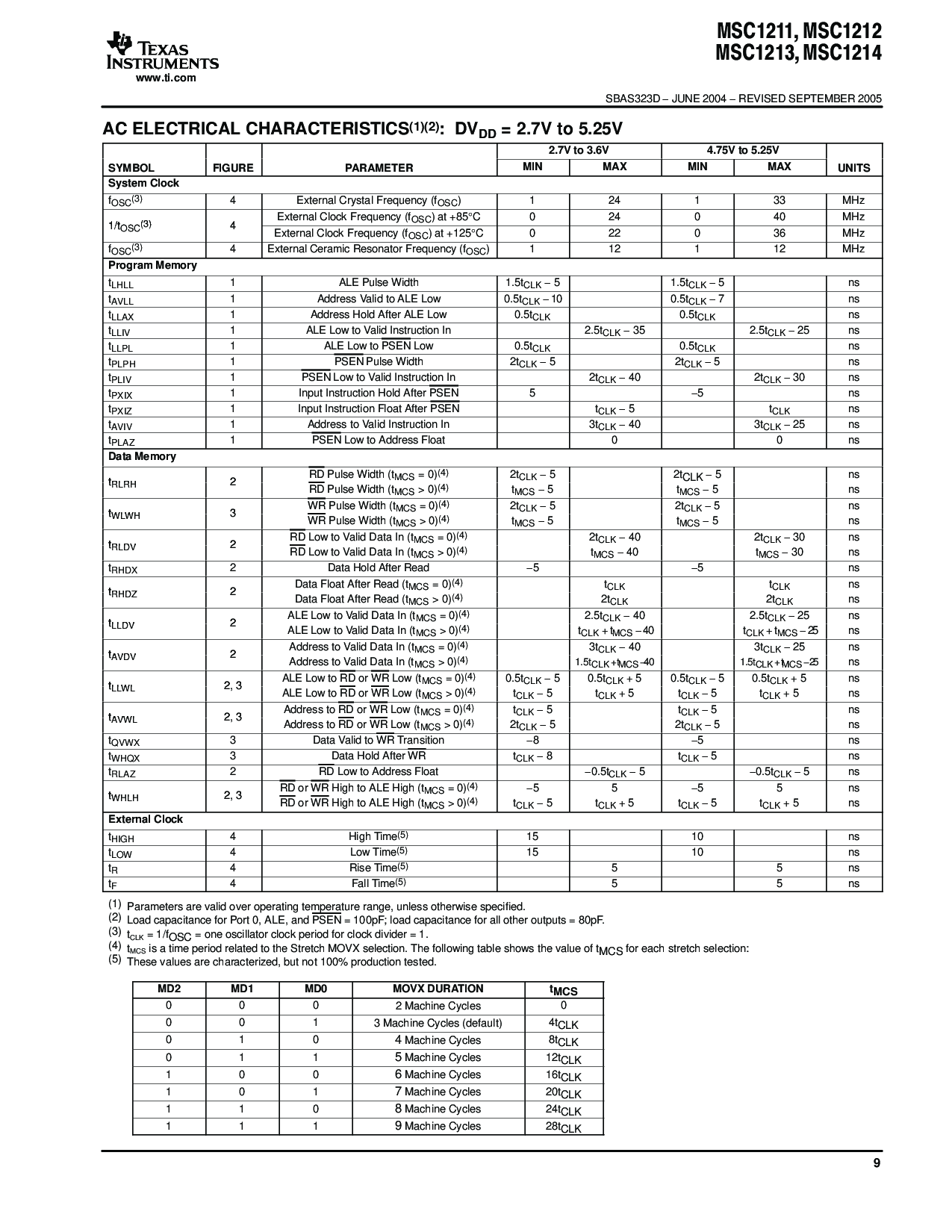

交流 电的 特性

(1)(2)

: dv

DD

= 2.7v 至 5.25v

2.7v 至 3.6v 4.75v 至 5.25v

标识 图示 参数

最小值

最大值 最小值 最大值

单位

系统 时钟

f

OSC

(3)

4 外部 结晶 频率 (f

OSC

) 1 24 1 33 MHz

1/t

OSC

(3)

4

外部 时钟 频率 (f

OSC

) 在 +85

°

C 0 24 0 40 MHz

1/t

OSC

(3)

4

外部 时钟 频率 (f

OSC

) 在 +125

°

C 0 22 0 36 MHz

f

OSC

(3)

4 外部陶瓷的 共振器 频率 (f

OSC

) 1 12 1 12 MHz

程序 记忆

t

LHLL

1 ale 脉冲波 宽度 1.5t

CLK

− 5 1.5t

CLK

− 5 ns

t

AVLL

1 地址 有效的至 ale 低 0.5t

CLK

− 10 0.5t

CLK

− 7 ns

t

LLAX

1 地址 支撑 之后 ale 低 0.5t

CLK

0.5t

CLK

ns

t

LLIV

1 ale 低 至 有效的 操作指南 在 2.5t

CLK

− 35 2.5t

CLK

− 25 ns

t

LLPL

1 ale 低 至 psen低 0.5t

CLK

0.5t

CLK

ns

t

PLPH

1 PSEN脉冲波 宽度 2t

CLK

− 5 2t

CLK

− 5 ns

t

PLIV

1 PSEN低 至 有效的 操作指南 在 2t

CLK

− 40 2t

CLK

− 30 ns

t

PXIX

1 输入 操作指南 支撑 之后 psen 5 −5 ns

t

PXIZ

1 输入 操作指南 float 之后 psen t

CLK

− 5 t

CLK

ns

t

AVIV

1 地址 至 有效的 操作指南 在 3t

CLK

− 40 3t

CLK

− 25 ns

t

PLAZ

1 PSEN低 至 地址 float 0 0 ns

数据 记忆

t

RLRH

2

RD脉冲波 宽度 (t

MCS

= 0)

(4)

2t

CLK

− 5 2t

CLK

− 5 ns

t

RLRH

2

RD脉冲波 宽度 (t

MCS

> 0)

(4)

t

MCS

− 5 t

MCS

− 5 ns

t

WLWH

3

WR脉冲波 宽度 (t

MCS

= 0)

(4)

2t

CLK

− 5 2t

CLK

− 5 ns

t

WLWH

3

WR脉冲波 宽度 (t

MCS

> 0)

(4)

t

MCS

− 5 t

MCS

− 5 ns

t

RLDV

2

RD低 至 有效的 数据 在 (t

MCS

= 0)

(4)

2t

CLK

− 40 2t

CLK

− 30 ns

t

RLDV

2

RD低 至 有效的 数据 在 (t

MCS

> 0)

(4)

t

MCS

− 40 t

MCS

− 30 ns

t

RHDX

2 数据 支撑 之后 读 −5 −5 ns

t

RHDZ

2

数据 float 之后 读 (t

MCS

= 0)

(4)

t

CLK

t

CLK

ns

t

RHDZ

2

数据 float 之后 读 (t

MCS

> 0)

(4)

2t

CLK

2t

CLK

ns

t

LLDV

2

ale 低 至 有效的 数据 在 (t

MCS

= 0)

(4)

2.5t

CLK

− 40 2.5t

CLK

− 25 ns

t

LLDV

2

ale 低 至 有效的 数据 在 (t

MCS

> 0)

(4)

t

CLK

+ t

MCS

− 40 t

CLK

+ t

MCS

− 25 ns

t

AVDV

2

地址 至 valid 数据 在 (t

MCS

= 0)

(4)

3t

CLK

− 40 3t

CLK

− 25 ns

t

AVDV

2

地址 至 有效的 数据 在 (t

MCS

> 0)

(4)

1.5t

CLK

+ t

MCS

−4 0 1.5t

CLK

+ t

MCS

− 25

ns

t

LLWL

2, 3

ale 低 至 rd或者 wr低 (t

MCS

= 0)

(4)

0.5t

CLK

− 5 0.5t

CLK

+ 5 0.5t

CLK

− 5 0.5t

CLK

+ 5 ns

t

LLWL

2, 3

ale 低 至 rd或者 wr低 (t

MCS

> 0)

(4)

t

CLK

− 5 t

CLK

+ 5 t

CLK

− 5 t

CLK

+ 5 ns

t

AVWL

2, 3

地址 至 rd或者 wr低 (t

MCS

= 0)

(4)

t

CLK

− 5 t

CLK

− 5 ns

t

AVWL

2, 3

地址 至 rd或者 wr低 (t

MCS

> 0)

(4)

2t

CLK

− 5 2t

CLK

− 5 ns

t

QVWX

3 数据 有效的 至 wr转变 −8 −5 ns

t

WHQX

3 数据 支撑 之后 wr t

CLK

− 8 t

CLK

− 5 ns

t

RLAZ

2 RD低 至 地址 float −0.5t

CLK

− 5 −0.5t

CLK

− 5 ns

t

WHLH

2, 3

RD或者 wr高 至 ale 高 (t

MCS

= 0)

(4)

−5 5 −5 5 ns

t

WHLH

2, 3

RD或者 wr高 至 ale 高 (t

MCS

> 0)

(4)

t

CLK

− 5 t

CLK

+ 5 t

CLK

− 5 t

CLK

+ 5 ns

外部 时钟

t

高

4 高 时间

(5)

15 10 ns

t

低

4 低 时间

(5)

15 10 ns

t

R

4 上升 时间

(5)

5 5 ns

t

F

4 下降 时间

(5)

5 5 ns

(1)

参数 是 有效的 在 运行 温度 范围, 除非 否则 指定.

(2)

加载 电容 为 端口 0, ale, 和 psen

= 100pf; 加载 电容 为 所有 其它 输出 = 80pf.

(3)

t

CLK

= 1/f

OSC

= 一个 振荡器 时钟 时期 为 时钟 分隔物 = 1.

(4)

t

MCS

是 一个 时间 时期 related 至 这 stretch movx 选择. 这 下列的 表格 显示 这 值 的 t

MCS

为 各自 stretch 选择:

(5)

这些 值 是 典型, 但是 不 100% 生产 测试.

MD2

MD1 MD0 movx 持续时间 t

MCS

0 0 0

2 机器 循环

0

0 0 1

3 机器 循环 (default)

4t

CLK

0 1 0

4

机器 循环

8t

CLK

0 1 1

5

机器 循环

12t

CLK

1 0 0

6

机器 循环

16t

CLK

1 0 1

7

机器 循环

20t

CLK

1 1 0

8

机器 循环

24t

CLK

1 1 1

9

机器 循环

28t

CLK