cy7c09449pv-交流

文档 #: 38-06061 rev. *a 页 5 的 50

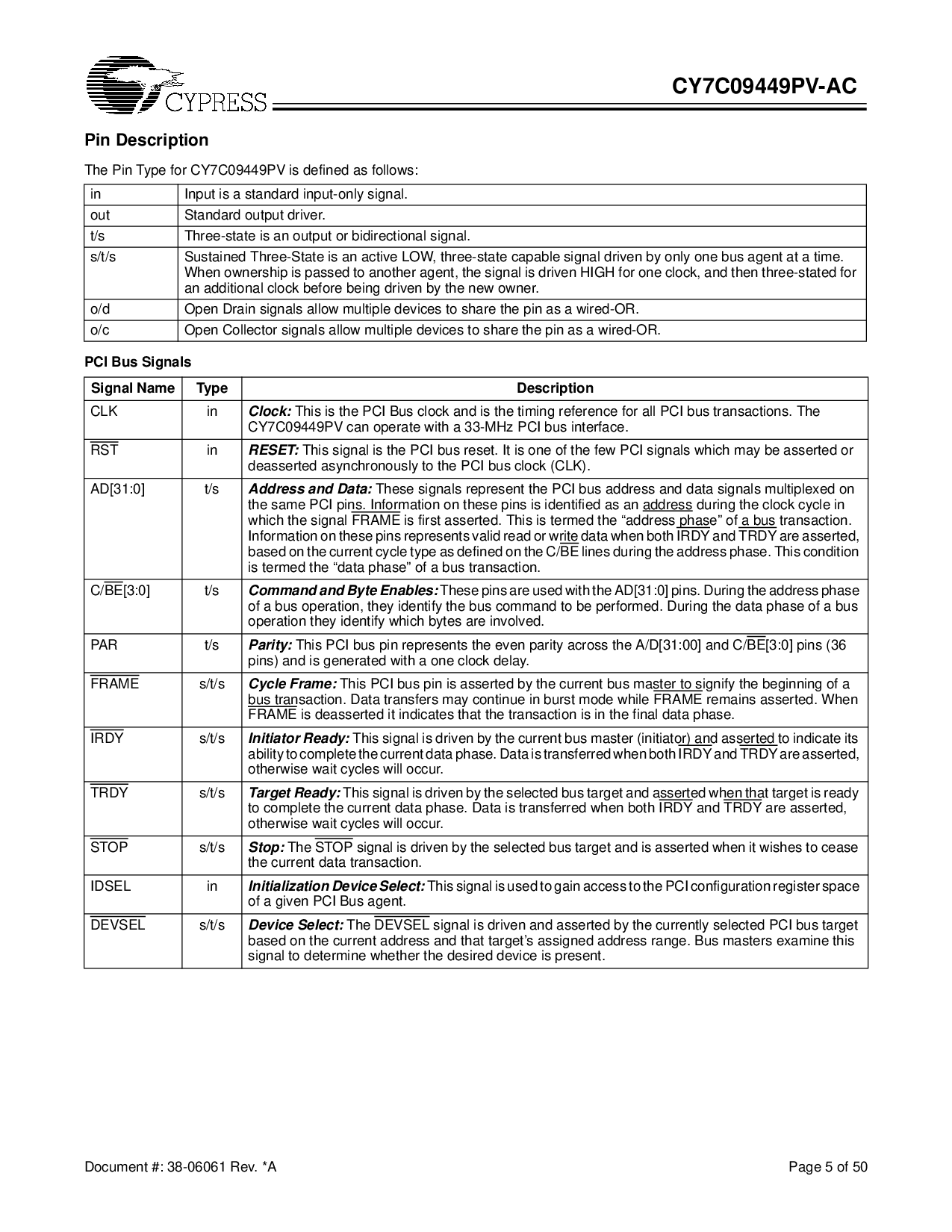

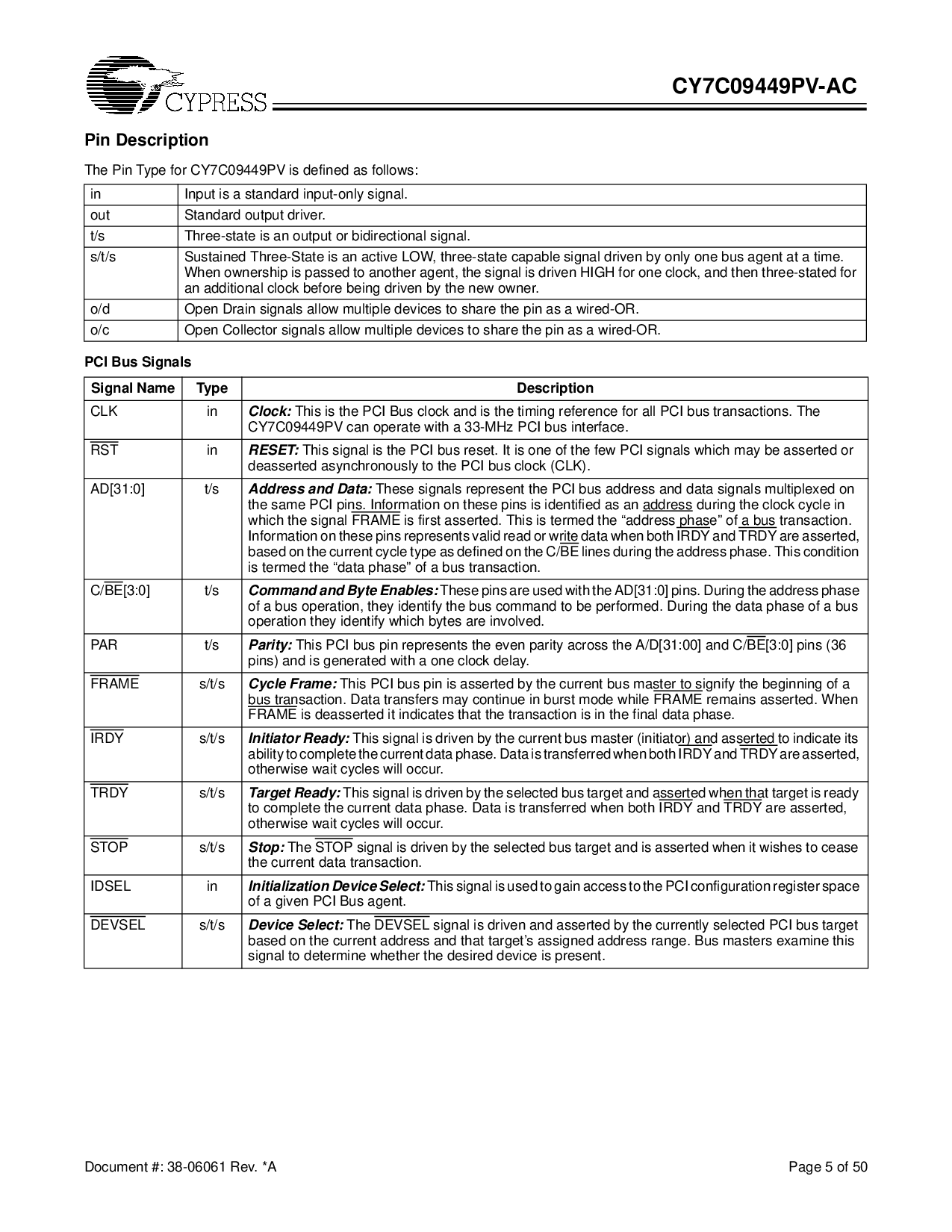

管脚 描述

这 管脚 类型 为 cy7c09449pv 是 定义 作 跟随:

在 输入 是 一个 标准 输入-仅有的 信号.

输出 标准 输出 驱动器.

t/s 三-状态 是 一个 输出 或者 双向的 信号.

s/t/s sustained 三-状态 是 一个 起作用的 低, 三-状态 有能力 信号 驱动 用 仅有的 一个 总线 代理 在 一个 时间.

当 ownership 是 passed 至 另一 代理, 这 信号 是 驱动 高 为 一个 时钟, 和 然后 三-陈述 为

一个 额外的 时钟 在之前 正在 驱动 用 这 新 所有权人.

o/d 打开 流 信号 准许 多样的 设备 至 share 这 管脚 作 一个 连线的-或者.

o/c 打开 集电级 信号 准许 多样的 设备 至 share 这 管脚 作 一个 连线的-或者.

pci 总线 信号

信号 名字 类型 描述

CLK 在

时钟:

这个 是 这 pci 总线 时钟 和 是 这 定时 涉及 为 所有 pci 总线 transactions. 这

cy7c09449pv 能 运作 和 一个 33-mhz pci 总线 接口.

RST

在

重置:

这个 信号 是 这 pci 总线 重置. 它 是 一个 的 这 few pci 信号 这个 将 是 asserted 或者

deasserted asynchronously 至 这 pci 总线 时钟 (clk).

ad[31:0] t/s

地址 和 数据:

这些 信号 代表 这 pci 总线 地址 和 数据 信号 多路复用 在

这 一样 pci 管脚. 信息 在 这些 管脚 是 identified 作 一个 地址

在 这 时钟 循环 在

这个 这 信号 框架

是 第一 asserted. 这个 是 termed 这

“

地址 阶段

”

的 一个 总线 transaction.

信息 在 这些 管脚 代表 有效的 读 或者 写 数据 当 两个都 irdy

和 trdy是 asserted,

为基础 在 这 电流 循环 类型 作 定义 在 这 c/是

线条 在 这 地址 阶段. 这个 情况

是 termed 这

“

数据 阶段

”

的 一个 总线 transaction.

c/是

[3:0] t/s

command 和 字节 使能:

这些 管脚 是 使用 和 这 ad[31:0] 管脚. 在 这 地址 阶段

的 一个 总线 运作, 它们 identify 这 总线 command 至 是 执行. 在 这 数据 阶段 的 一个 总线

运作 它们 identify 这个 字节 是 involved.

PAR t/s

parity:

这个 pci 总线 管脚 代表 这 甚至 parity 横过 这 一个/d[31:00] 和 c/是

[3:0] 管脚 (36

管脚) 和 是 发生 和 一个 一个 时钟 延迟.

框架

s/t/s

循环 框架:

这个 pci 总线 管脚 是 asserted 用 这 电流 总线 主控 至 signify 这 beginning 的 一个

总线 transaction. 数据 transfers 将 continue 在 burst 模式 当 框架

仍然是 asserted. 当

框架

是 deasserted 它 indicates 那 这 transaction 是 在 这 最终 数据 阶段.

IRDY

s/t/s

Initiator

准备好:

这个 信号 是 驱动 用 这 电流 总线 主控 (initiator) 和 asserted 至 表明 它的

能力 至 完全 这 电流 数据 阶段. 数据 是 transferred 当 两个都 irdy

和 trdy是 asserted,

否则 wait 循环 将 出现.

TRDY

s/t/s

目标 准备好:

这个 信号 是 驱动 用 这 选择 总线 目标 和 asserted 当 那 目标 是 准备好

至 完全 这 电流 数据 阶段. 数据 是 transferred 当 两个都 irdy

和 trdy是 asserted,

否则 wait 循环 将 出现.

停止

s/t/s

停止:

这 停止信号 是 驱动 用 这 选择 总线 目标 和 是 asserted 当 它 wishes 至 cease

这 电流 数据 transaction.

IDSEL 在

initialization 设备 选择:

这个 信号 是 使用 至 增益 进入 至 这 pci 配置 寄存器 空间

的 一个 给 pci 总线 代理.

DEVSEL

s/t/s

设备 选择:

这 devsel信号 是 驱动 和 asserted 用 这 目前 选择 pci 总线 目标

为基础 在 这 电流 地址 和 那 目标

’

s assigned 地址 范围. 总线 masters examine 这个

信号 至 决定 whether 这 desired 设备 是 呈现.