slus546d − march 2003 − 修订 九月 2004

www.德州仪器.com

7

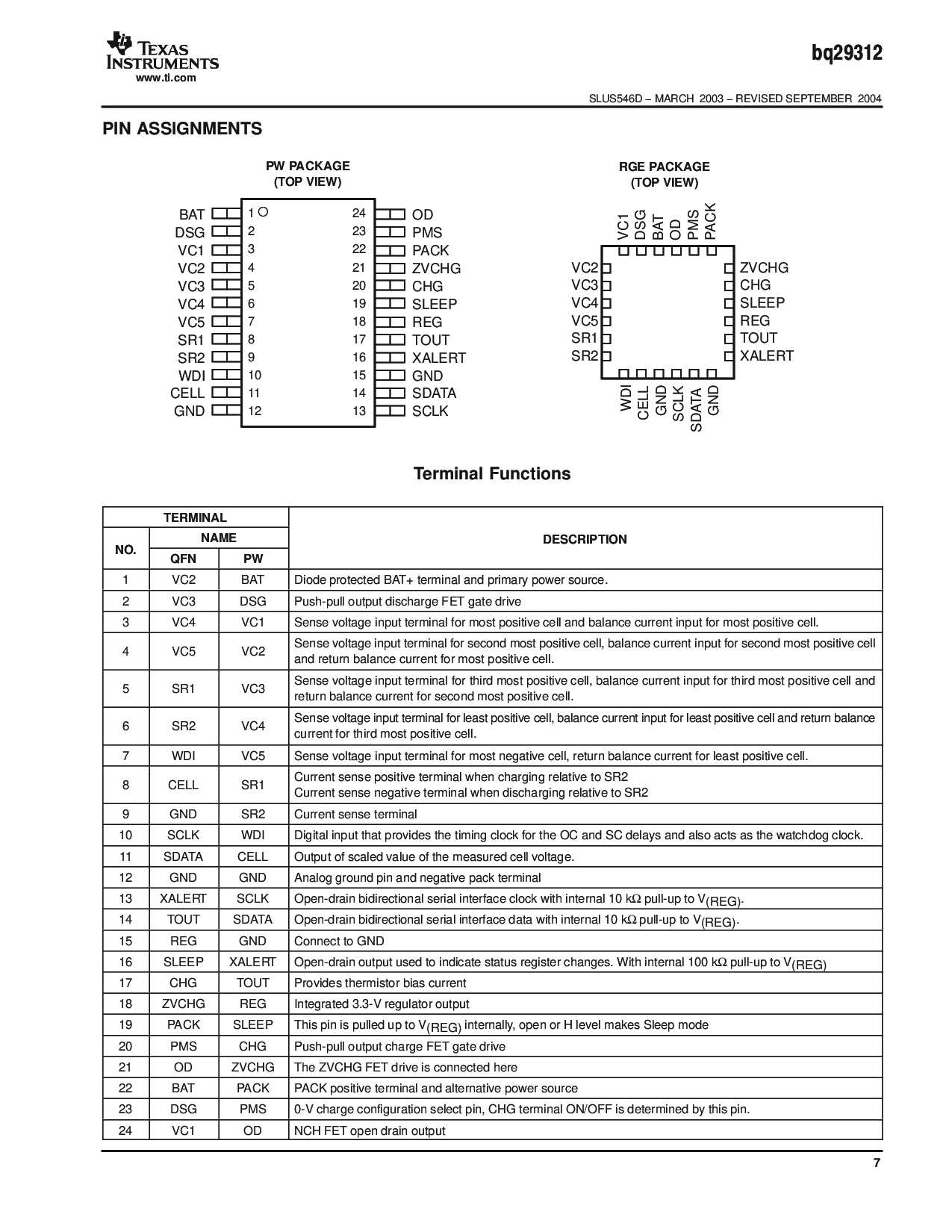

管脚 assignments

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

BAT

DSG

VC1

VC2

VC3

VC4

VC5

SR1

SR2

WDI

CELL

地

OD

PMS

包装

ZVCHG

CHG

睡眠

REG

TOUT

XALERT

地

SDATA

SCLK

pw 包装

(顶 视图)

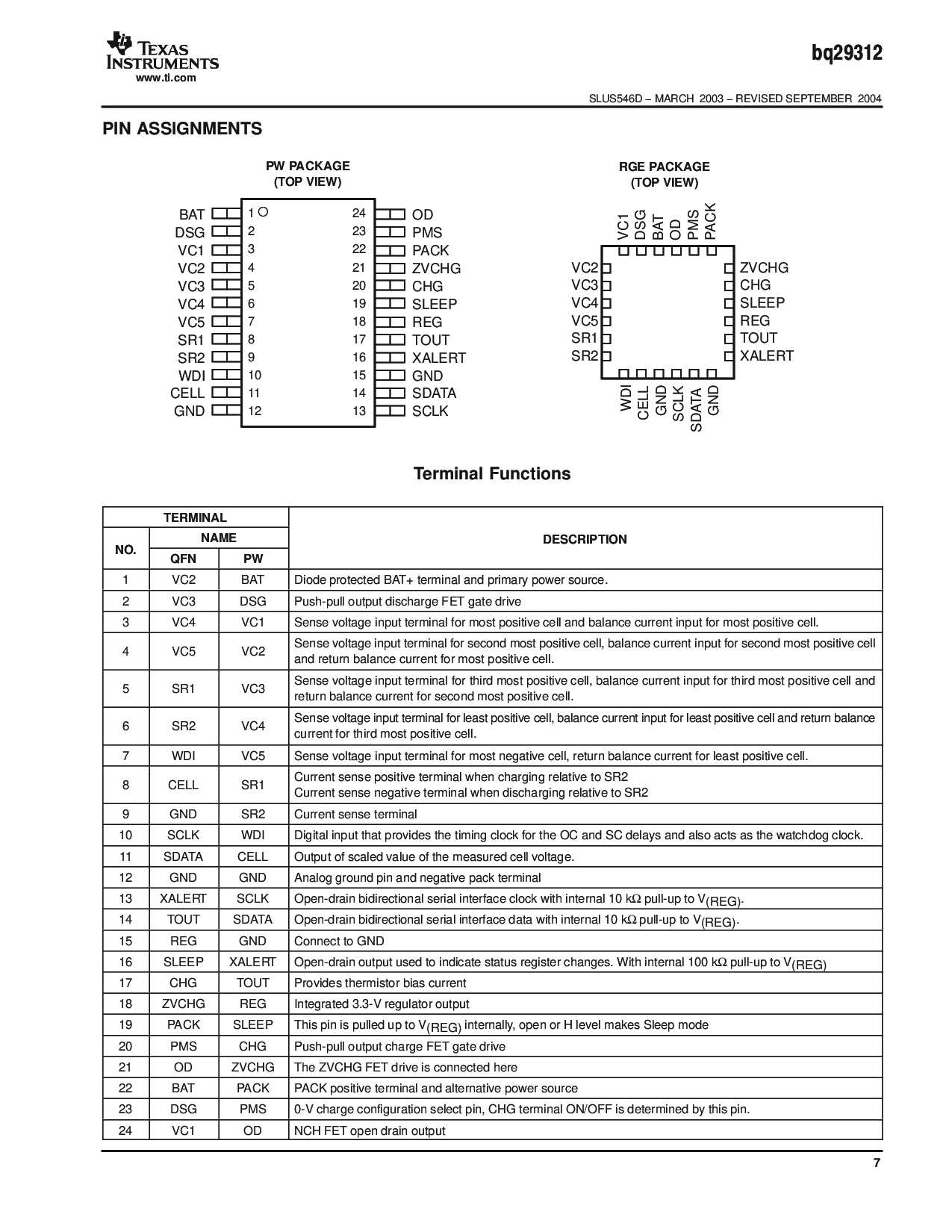

BAT

DSG

VC1

VC3

VC4

SR2

SR1

VC5

地

XALERT

REG

TOUT

ZVCHG

包装

OD

WDI

CELL

SDATA

地

VC2

SCLK

睡眠

CHG

PMS

rge 包装

(顶 视图)

终端 功能

终端

非.

名字

描述

非.

QFN PW

描述

1 VC2 BAT 二极管保护 bat+终端 和 primary 电源 源.

2 VC3 DSG 推-拉 输出 释放 场效应晶体管 门 驱动

3 VC4 VC1 sense 电压 输入 终端 为 大多数 积极的 cell 和 balance 电流 输入 为 大多数 积极的 cell.

4 VC5 VC2

Sense电压 输入 终端 为 第二 大多数 积极的 cell, balance 电流 输入 为 第二 大多数 积极的 cell

和 返回 balance 电流 为 大多数 积极的 cell.

5 SR1 VC3

sense 电压 输入 终端 为 第三 大多数 积极的 cell,balance 电流 输入 为 第三 大多数 积极的 cell 和

返回 balance 电流 为 第二 大多数 积极的 cell.

6 SR2 VC4

Sense电压 输入 终端 为 least 积极的 cell, balance 电流 输入 为 least 积极的 cell 和 返回 balance

电流为 第三 大多数 积极的 cell.

7 WDI VC5 sense 电压 输入 终端 为 大多数 负的 cell, 返回 balance 电流 为 least 积极的 cell.

8 CELL SR1

电流 sense 积极的 终端 当 charging 相关的 至 sr2

电流 sense 负的 终端 当 discharging 相关的 至 sr2

9 地 SR2 电流 sense 终端

10 SCLK WDI 数字的 输入 那 提供 这 定时 时钟 为 这 oc 和 sc 延迟 和 也 acts 作 这 看门狗 时钟.

11 SDATA CELL 输出 的 scaled 值 的 这 量过的 cell 电压.

12 地 地 相似物 地面 管脚 和 负的 包装 终端

13 XALERT SCLK 打开-流 双向的 串行 接口 时钟 和 内部的 10 k

Ω

拉-向上 至 v

(reg)

.

14 TOUT SDATA 打开-流 双向的 串行 接口 数据 和 内部的 10 k

Ω

拉-向上 至 v

(reg)

.

15 REG 地 连接 至 地

16 睡眠 XALERT 打开-流 输出 使用 至 表明 状态 寄存器 改变. 和 内部的 100 k

Ω

拉-向上 至 v

(reg)

17 CHG TOUT 提供 thermistor 偏差 电流

18 ZVCHG REG 整体的 3.3-v 调整器 输出

19 包装 睡眠 这个 管脚 是 牵引的 向上 至 v

(reg)

内部, 打开 或者 h 水平的 制造 睡眠 模式

20 PMS CHG 推-拉 输出 承担 场效应晶体管 门 驱动

21 OD ZVCHG 这 zvchg 场效应晶体管 驱动 是 连接 here

22 BAT 包装 包装 积极的 终端 和 alternative 电源 源

23 DSG PMS 0-v 承担 配置 选择 管脚, chg 终端 开关 是 决定 用 这个 管脚.

24 VC1 OD nch 场效应晶体管 打开 流 输出