硅 image, 公司

sii 161

一个

SiI

-DS-0009-D

硅 image, 公司

6 主题 至 改变 没有 注意

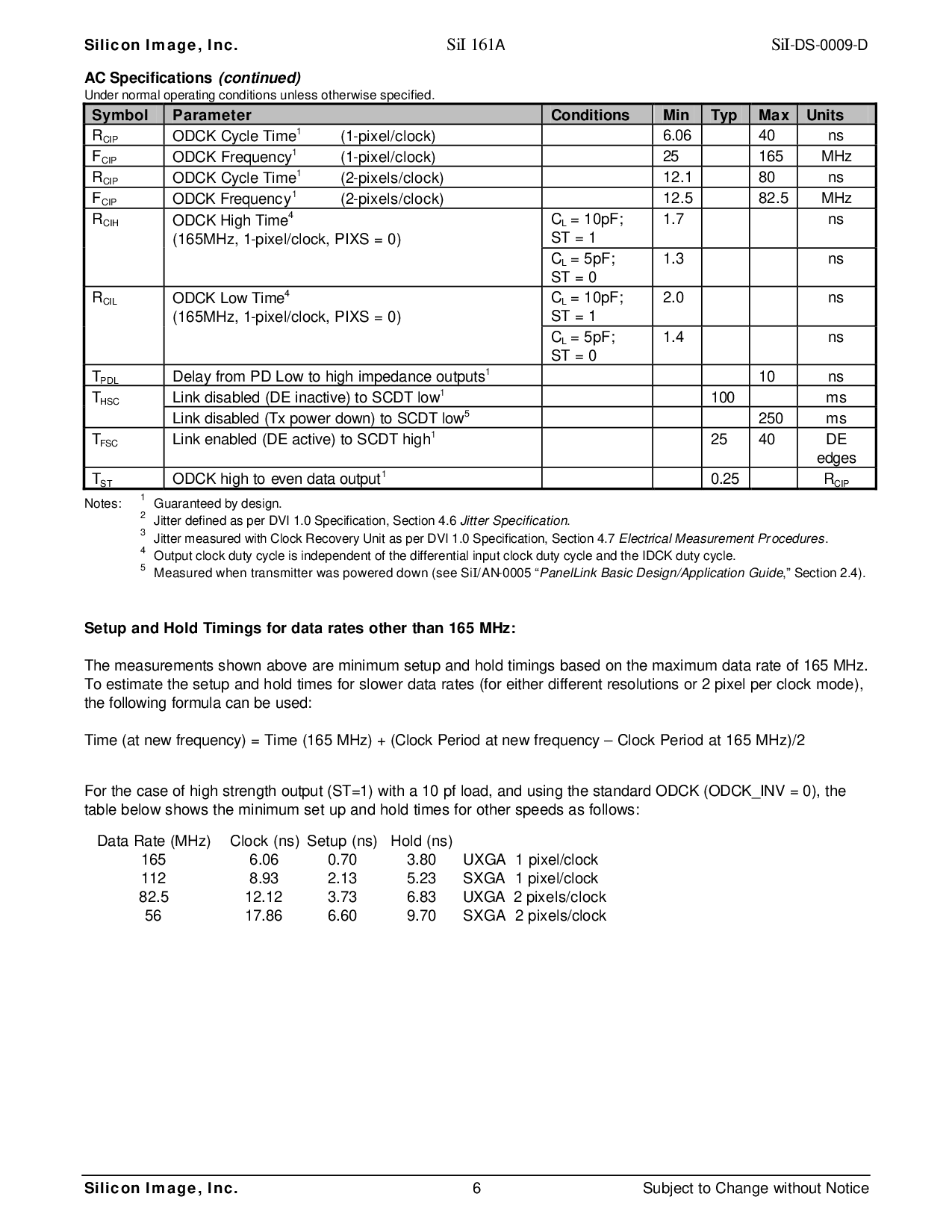

交流 规格

(持续)

下面 正常的 运行 conditions 除非 否则 指定.

标识 参数 情况 最小值 典型值 最大值 单位

R

CIP

odck 循环 时间

1

(1-pixel/时钟)

6.06 40 ns

F

CIP

odck 频率

1

(1-pixel/时钟)

25 165 MHz

R

CIP

odck 循环 时间

1

(2-pixels/时钟)

12.1 80 ns

F

CIP

odck frequency

1

(2-pixels/时钟)

12.5 82.5 MHz

R

CIH

odck 高 时间

4

(165mhz, 1-pixel/时钟, pixs = 0)

C

L

= 10pf;

st = 1

1.7 ns

C

L

= 5pf;

st = 0

1.3 ns

R

CIL

odck 低 时间

4

(165mhz, 1-pixel/时钟, pixs = 0)

C

L

= 10pf;

st = 1

2.0 ns

C

L

= 5pf;

st = 0

1.4 ns

T

PDL

延迟 从 pd 低 至 高 阻抗 输出

1

10 ns

T

HSC

link 无能 (de inactive) 至 scdt 低

1

100 ms

link 无能 (tx 电源 向下) 至 scdt 低

5

250 ms

T

FSC

link 使能 (de 起作用的) 至 scdt 高

1

25 40 DE

edges

T

ST

odck 高 至甚至 数据 输出

1

0.25 R

CIP

注释:

1

有保证的 用 设计.

2

jitter 定义 作 每 dvi 1.0 规格, 部分 4.6

jitter 规格

.

3

jitter 量过的 和 时钟 恢复 单位 作 每 dvi 1.0 规格, 部分 4.7

电的 度量 procedures

.

4

输出 时钟 职责 循环 是 独立 的 这 差别的 输入 时钟 职责 循环 和 这 idck 职责 循环.

5

量过的 当 传输者 是 powered 向下 (看 si

I

/一个-0005 “

panellink 基本 设计/应用 手册

,” 部分 2.4).

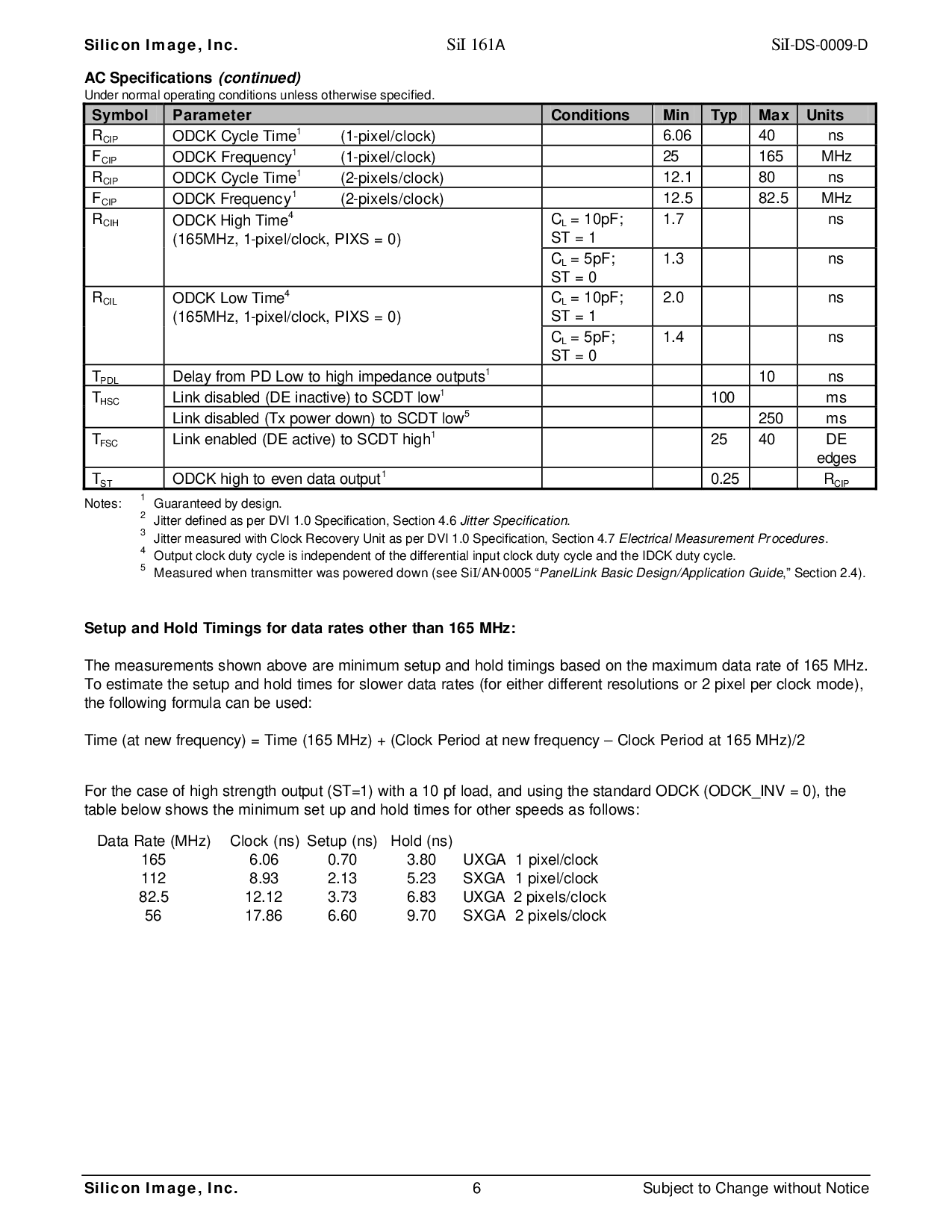

建制 和 支撑timings 为 数据 比率 其它 比 165 mhz:

这 度量 显示 在之上 是 最小 建制 和 支撑 timings 为基础 在 这 最大 数据 比率 的 165 mhz.

至 估计 这 建制 和 支撑 时间 为 slower 数据 比率 (为 也 不同的 resolutions 或者 2 pixel每 时钟 模式),

这 下列的 formula 能 是 使用:

时间 (在 新 频率) = 时间 (165 mhz) + (clock 时期 在 新 频率–时钟 时期 在 165 mhz)/2

为 这 情况 的 高 力量 输出 (st=1) 和 一个 10 pf 加载, 和 使用 这 标准 odck (odck_inv = 0), 这

表格 在下 显示 这 最小 设置 向上 和 支撑 时间 为 其它 speeds 作 跟随:

数据 比率 (mhz) 时钟 (ns) 建制 (ns) 支撑 (ns)

165 6.06 0.70 3.80 uxga 1 pixel/时钟

112 8.93 2.13 5.23 sxga 1 pixel/时钟

82.5 12.12 3.73 6.83 uxga 2 pixels/时钟

56 17.86 6.60 9.70 sxga 2 pixels/时钟