函数的 描述

(持续)

这 TP11362A 是 有能力 的 处理 第八 独立

途径 (half duplex) 或者 四 全部-duplex PCM 途径

在里面 125 µs (8 khz).

这 逻辑 状态 的 TRB 在 这 下落 边缘 的 CE 确定

这个 输入 寄存器 是 起作用的 在 那 CE 时期 和 这个

输出 寄存器 将 是 起作用的 在 这 下列的 第三 CE 时期.

这 输入 数据 是 processed (pcm 数据 encoded 或者 ADPCM

数据 解码) 在 这 第二 循环 和 shifted 输出 在 这

第三 循环 的 CE 当 CE 是 高.

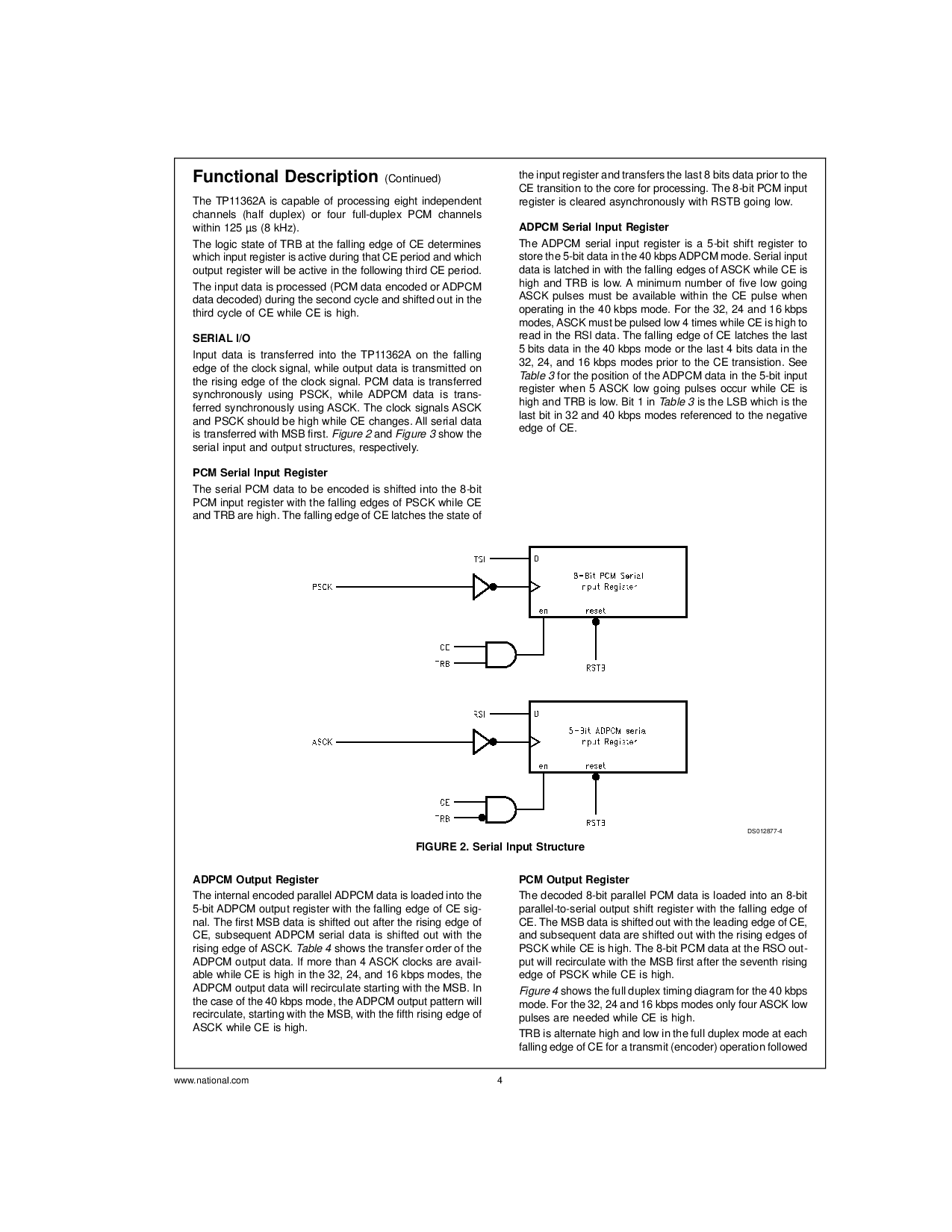

串行 i/o

输入 数据 是 transferred 在 这 TP11362A 在 这 下落

边缘 的 这 时钟 信号, 当 输出 数据 是 transmitted 在

这 rising 边缘 的 这 时钟 信号. PCM 数据 是 transferred

synchronously 使用 psck, 当 ADPCM 数据 是 trans-

ferred synchronously 使用 asck. 这 时钟 信号 ASCK

和 PSCK 应当 是 高 当 CE 改变. 所有 串行 数据

是 transferred 和 MSB 第一.

图示 2

和

图示 3

显示 这

串行 输入 和 输出 结构, 各自.

PCM 串行 输入 寄存器

这 串行 PCM 数据 至 是 encoded 是 shifted 在 这 8-位

PCM 输入 寄存器 和 这 下落 edges 的 PSCK 当 CE

和 TRB 是 高. 这 下落 边缘 的 CE latches 这 状态 的

这 输入 寄存器 和 transfers 这 last 8 位 数据 较早的 至 这

CE 转变 至 这 核心 为 处理. 这 8-位 PCM 输入

寄存器 是 cleared asynchronously 和 RSTB going 低.

ADPCM 串行 输入 寄存器

这 ADPCM 串行 输入 寄存器 是 一个 5-位 变换 寄存器 至

store 这 5-位 数据 在 这 40 kbps ADPCM 模式. 串行 输入

数据 是 latched 在 和 这 下落 edges 的 ASCK 当 CE 是

高 和 TRB 是 低. 一个 最小 号码 的 five 低 going

ASCK 脉冲 必须 是 有 在里面 这 CE 脉冲波 当

运行 在 这 40 kbps 模式. 为 这 32, 24 和 16 kbps

模式, ASCK 必须 是 搏动 低 4 时间 当 CE 是 高 至

读 在 这 RSI 数据. 这 下落 边缘 的 CE latches 这 last

5 位 数据 在 这 40 kbps 模式 或者 这 last 4 位 数据 在 这

32, 24, 和 16 kbps 模式 较早的 至 这 CE transistion. 看

表格 3

为 这 位置 的 这 ADPCM 数据 在 这 5-位 输入

寄存器 当 5 ASCK 低 going 脉冲 出现 当 CE 是

高 和 TRB 是 低. 位 1 在

表格 3

是 这 LSB 这个 是 这

last 位 在 32 和 40 kbps 模式 关联 至 这 负的

边缘 的 ce.

ADPCM 输出 寄存器

这 内部的 encoded 并行的 ADPCM 数据 是 承载 在 这

5-位 ADPCM 输出 寄存器 和 这 下落 边缘 的 CE sig-

nal. 这 第一 MSB 数据 是 shifted 输出 之后 这 rising 边缘 的

ce, subsequent ADPCM 串行 数据 是 shifted 输出 和 这

rising 边缘 的 asck.

表格 4

显示 这 转移 顺序 的 这

ADPCM 输出 数据. 如果 更多 比 4 ASCK clocks 是 avail-

能 当 CE 是 高 在 这 32, 24, 和 16 kbps 模式, 这

ADPCM 输出 数据 将 recirculate 开始 和 这 msb. 在

这 情况 的 这 40 kbps 模式, 这 ADPCM 输出 模式 将

recirculate, 开始 和 这 msb, 和 这 fifth rising 边缘 的

ASCK 当 CE 是 高.

PCM 输出 寄存器

这 解码 8-位 并行的 PCM 数据 是 承载 在 一个 8-位

并行的-至-串行 输出 变换 寄存器 和 这 下落 边缘 的

ce. 这 MSB 数据 是 shifted 输出 和 这 leading 边缘 的 ce,

和 subsequent 数据 是 shifted 输出 和 这 rising edges 的

PSCK 当 CE 是 高. 这 8-位 PCM 数据 在 这 RSO 输出-

放 将 recirculate 和 这 MSB 第一 之后 这 seventh rising

边缘 的 PSCK 当 CE 是 高.

图示 4

显示 这 全部 duplex 定时 图解 为 这 40 kbps

模式. 为 这 32, 24 和 16 kbps 模式 仅有的 四 ASCK 低

脉冲 是 需要 当 CE 是 高.

TRB 是 alternate 高 和 低 在 这 全部 duplex 模式 在 各自

下落 边缘 的 CE 为 一个 transmit (encoder) 运作 followed

ds012877-4

图示 2. 串行 输入 结构

www.国家的.com 4