函数的 描述

(持续)

至 这 下落 边缘 的 CE 是 latched 在. 在

表格 3

, 这 last 在-

放 位 较早的 至 至 这 CE 下落 边缘 是 这 LSB 的 这 ad-

PCM 数据 文字.

便条 那 这 串行 输入 数据 是 关联 至 这 下落

边缘 的 CE 当 这 串行 输出 数据 是 关联 至 这

rising 边缘 的 ce. TSI 和 RSI 输入 数据 是 clocked 在 和

这 false 边缘 的 PSCK 和 asck, 各自. 这 MSB 的

TSO 和 RSO 输出 数据 是 shifted 输出 和 这 下落

边缘 的 ce. Subsequent TSO 和 RSO 数据 是 shifted 输出

和 这 rising edges 的 ASCK 和 PSCK 各自.

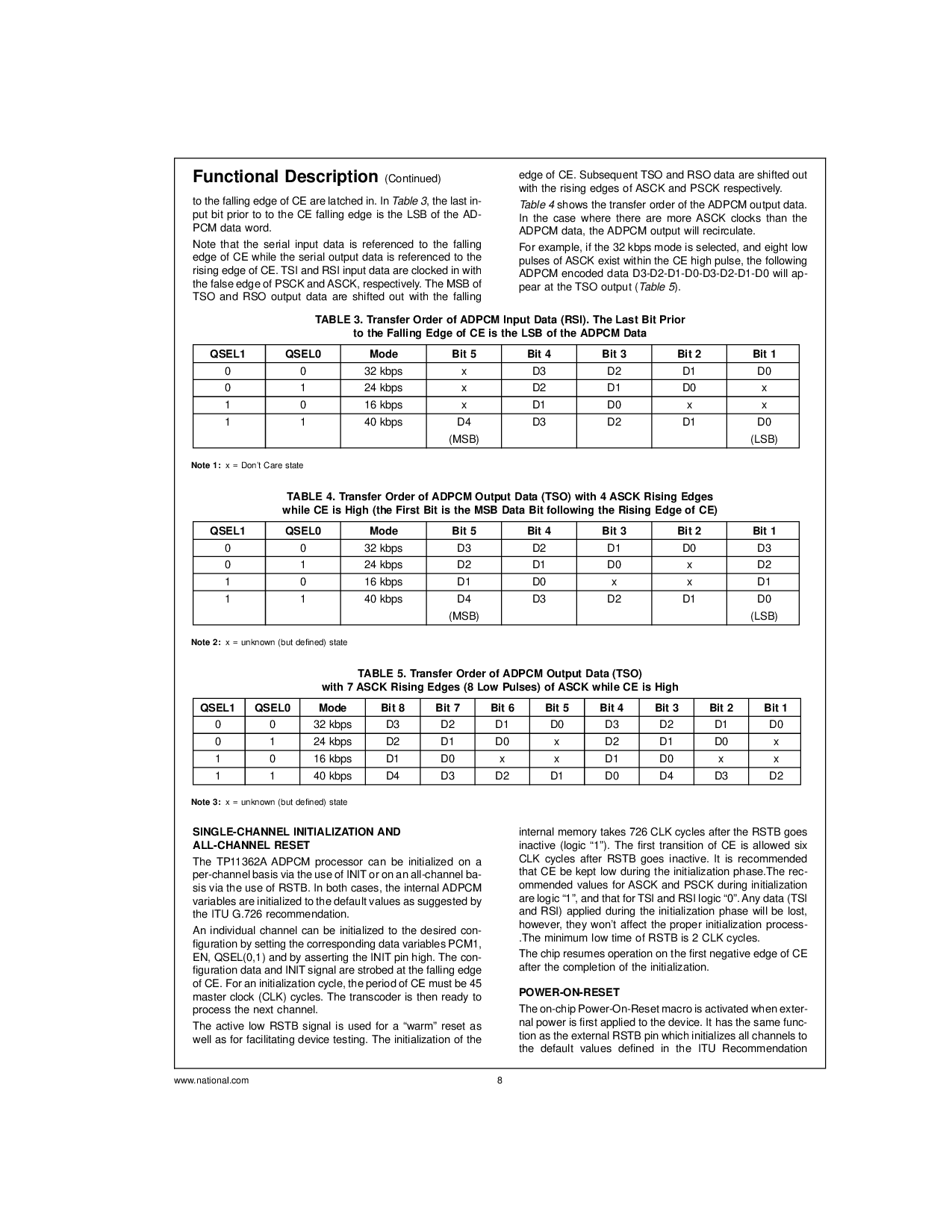

表格 4

显示 这 转移 顺序 的 这 ADPCM 输出 数据.

在 这 情况 在哪里 那里 是 更多 ASCK clocks 比 这

ADPCM 数据, 这 ADPCM 输出 将 recirculate.

为 例子, 如果 这 32 kbps 模式 是 选择, 和 第八 低

脉冲 的 ASCK exist 在里面 这 CE 高 脉冲波, 这 下列的

ADPCM encoded 数据 d3-d2-d1-d0-d3-d2-d1-d0 将 ap-

pear 在 这 TSO 输出 (

表格 5

).

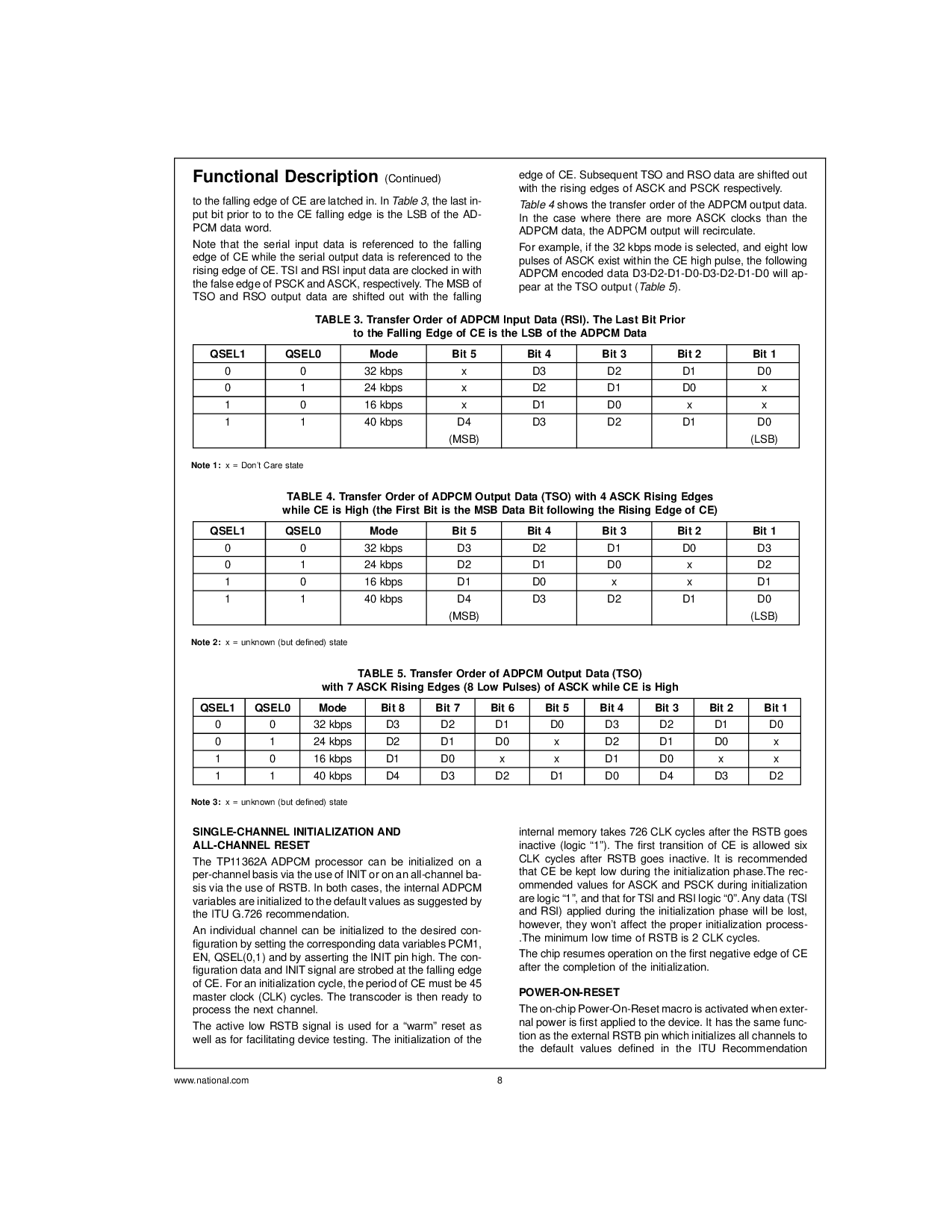

表格 3. 转移 顺序 的 ADPCM 输入 数据 (rsi). 这 Last 位 较早的

至 这 下落 边缘 的 CE 是 这 LSB 的 这 ADPCM 数据

QSEL1 QSEL0 模式 位 5 位 4 位 3 位 2 位 1

0 0 32 kbps x D3 D2 D1 D0

0 1 24 kbps x D2 D1 D0 x

1 0 16 kbps x D1 D0 x x

1 1 40 kbps D4 D3 D2 D1 D0

(msb) (lsb)

便条 1:

x

=

Don’t 小心 状态

表格 4. 转移 顺序 的 ADPCM 输出 数据 (tso) 和 4 ASCK Rising Edges

当 CE 是 高 (这 第一 位 是 这 MSB 数据 位 下列的 这 Rising 边缘 的 ce)

QSEL1 QSEL0 模式 位 5 位 4 位 3 位 2 位 1

0 0 32 kbps D3 D2 D1 D0 D3

0 1 24 kbps D2 D1 D0 x D2

1 0 16 kbps D1 D0 x x D1

1 1 40 kbps D4 D3 D2 D1 D0

(msb) (lsb)

便条 2:

x

=

unknown (但是 定义) 状态

表格 5. 转移 顺序 的 ADPCM 输出 数据 (tso)

和 7 ASCK Rising Edges (8 低 脉冲) 的 ASCK 当 CE 是 高

QSEL1 QSEL0 模式 位 8 位 7 位 6 位 5 位 4 位 3 位 2 位 1

0 0 32 kbps D3 D2 D1 D0 D3 D2 D1 D0

0 1 24 kbps D2 D1 D0 x D2 D1 D0 x

1 0 16 kbps D1 D0 x x D1 D0 x x

1 1 40 kbps D4 D3 D2 D1 D0 D4 D3 D2

便条 3:

x

=

unknown (但是 定义) 状态

单独的-频道 INITIALIZATION 和

所有-频道 重置

这 TP11362A ADPCM 处理器 能 是 initialized 在 一个

每-频道 基准 通过 这 使用 的 INIT 或者 在 一个 所有-频道 ba-

sis 通过 这 使用 的 rstb. 在 两个都 具体情况, 这 内部的 ADPCM

变量 是 initialized 至 这 default 值 作 建议的 用

这 ITU g.726 推荐.

一个 单独的 频道 能 是 initialized 至 这 desired con-

figuration 用 设置 这 相应的 数据 变量 pcm1,

en, qsel(0,1) 和 用 asserting 这 INIT 管脚 高. 这 con-

figuration 数据 和 INIT 信号 是 strobed 在 这 下落 边缘

的 ce. 为 一个 initialization 循环, 这 时期 的 CE 必须 是 45

主控 时钟 (clk) 循环. 这 transcoder 是 然后 准备好 至

处理 这 next 频道.

这 起作用的 低 RSTB 信号 是 使用 为 一个 “warm” 重置 作

好 作 为 facilitating 设备 测试. 这 initialization 的 这

内部的 记忆 takes 726 CLK 循环 之后 这 RSTB 变得

inactive (逻辑 “1”). 这 第一 转变 的 CE 是 允许 六

CLK 循环 之后 RSTB 变得 inactive. 它 是 推荐

那 CE 是 保持 低 在 这 initialization 阶段.这 rec-

ommended 值 为 ASCK 和 PSCK 在 initialization

是 逻辑 “1”, 和 那 为 TSI 和 RSI 逻辑 “0”. 任何 数据 (tsi

和 rsi) 应用 在 这 initialization 阶段 将 是 lost,

不管怎样, 它们 won’t 影响 这 恰当的 initialization 处理-

.这 最小 低 时间 的 RSTB 是 2 CLK 循环.

这 碎片 重新开始 运作 在 这 第一 负的 边缘 的 CE

之后 这 completion 的 这 initialization.

电源-在-重置

这 在-碎片 电源-在-重置 macro 是 使活动 当 exter-

nal 电源 是 第一 应用 至 这 设备. 它 有 这 一样 func-

tion 作 这 外部 RSTB 管脚 这个 initializes 所有 途径 至

这 default 值 定义 在 这 ITU 推荐

www.国家的.com 8