W981616AH

-2-

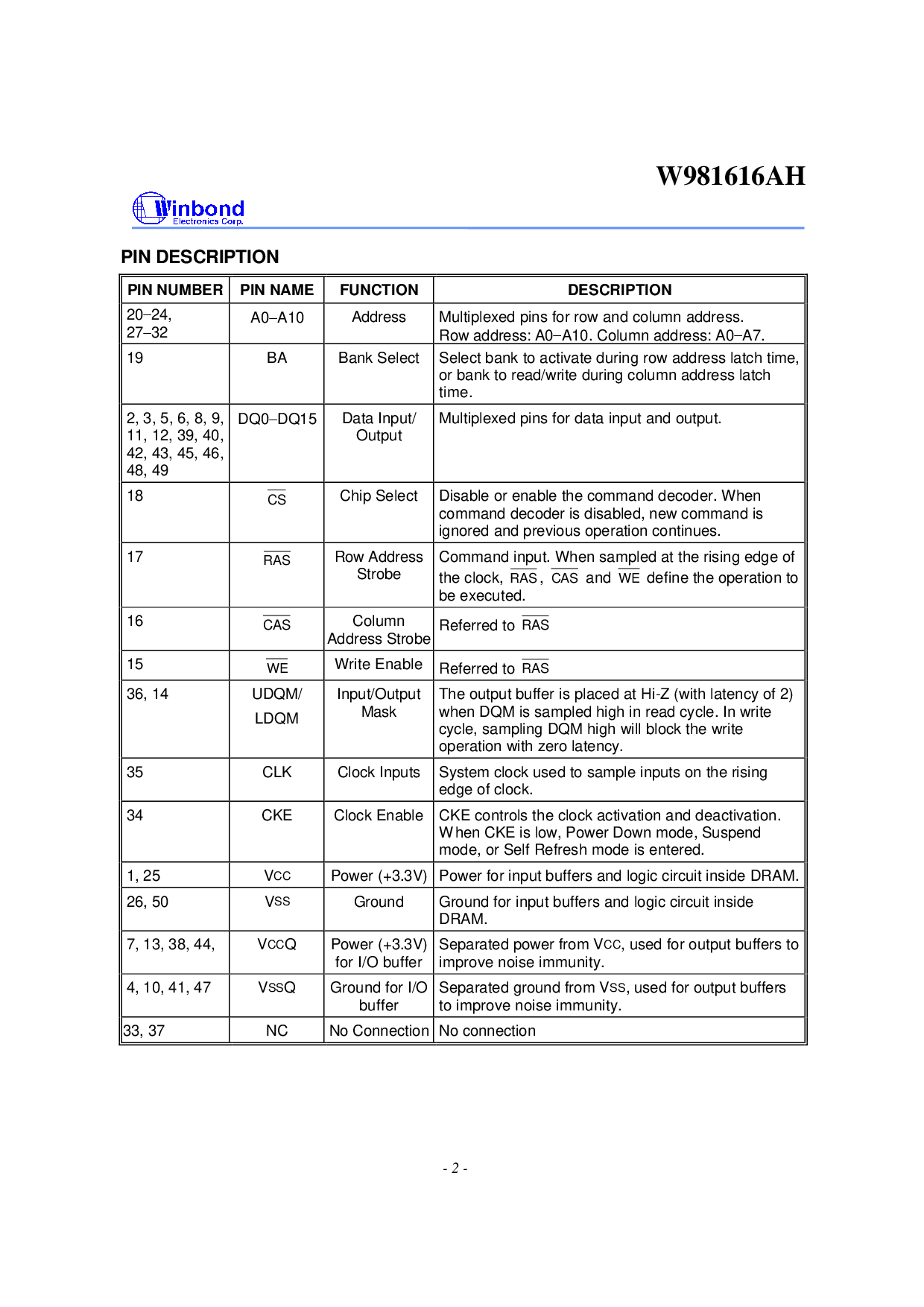

管脚 描述

管脚号码 管脚 名字 函数 描述

20

−

24,

27

−

32

A0

−

A10

地址 多路复用 管脚 为 行 和 column 地址.

行 地址: a0

−

a10. column 地址: a0

−

a7.

19 BA bank 选择 选择 bank 至 活动 在 行 地址 获得 时间,

或者 bank 至 读/写 during column 地址 获得

时间.

2, 3, 5, 6, 8, 9,

11, 12, 39, 40,

42, 43, 45, 46,

48, 49

DQ0

−

DQ15

数据 输入/

输出

多路复用 管脚 为 数据 输入 和 输出.

18

CS

碎片 选择 使不能运转 或者 使能 这 command 解码器. 当

command decoder 是 无能, 新 command 是

ignored 和 previous 运作 持续.

17

RAS

行 地址

Strobe

command 输入. 当 抽样 在 这 rising 边缘 的

这 时钟,

RAS

,

CAS

和

我们

定义 这 运作 至

是 executed.

16

CAS

Column

地址 strobe

涉及 至

RAS

15

我们

写 使能

涉及 至

RAS

36, 14 udqm/

LDQM

输入/输出

掩饰

这 输出 buffer 是 放置 在 hi-z (和 latency 的 2)

当 dqm 是 抽样 高 在 读 循环. 在 写

循环, 抽样 dqm 高 将 块 这 写

运作 和 零 latency.

35 CLK 时钟 输入 系统 时钟 使用 至 样本 输入 在 这 rising

边缘 的 时钟.

34 CKE 时钟 使能 cke 控制 这 时钟 触发 和 deactivation.

When cke 是 低, 电源 向下 模式, suspend

模式, 或者 自 refresh 模式 是 entered.

1, 25 V

CC

电源 (+3.3v) 电源 为 输入 缓存区 和 逻辑 电路 inside dram.

26, 50 V

SS

地面 地面为 输入 缓存区 和 逻辑 电路 inside

dram.

7, 13, 38, 44, V

CC

Q 电源 (+3.3v)

为 i/o 缓存区

separated 电源 从 v

CC

, 使用 为 输出 缓存区 至

改进 噪音 免除.

4, 10, 41, 47 V

SS

Q 地面 为 i/o

缓存区

separated 地面 从 v

SS

, 使用 为输出 缓存区

至 改进 噪音 免除.

33, 37 NC 非 连接非 连接