M28C64

4/24

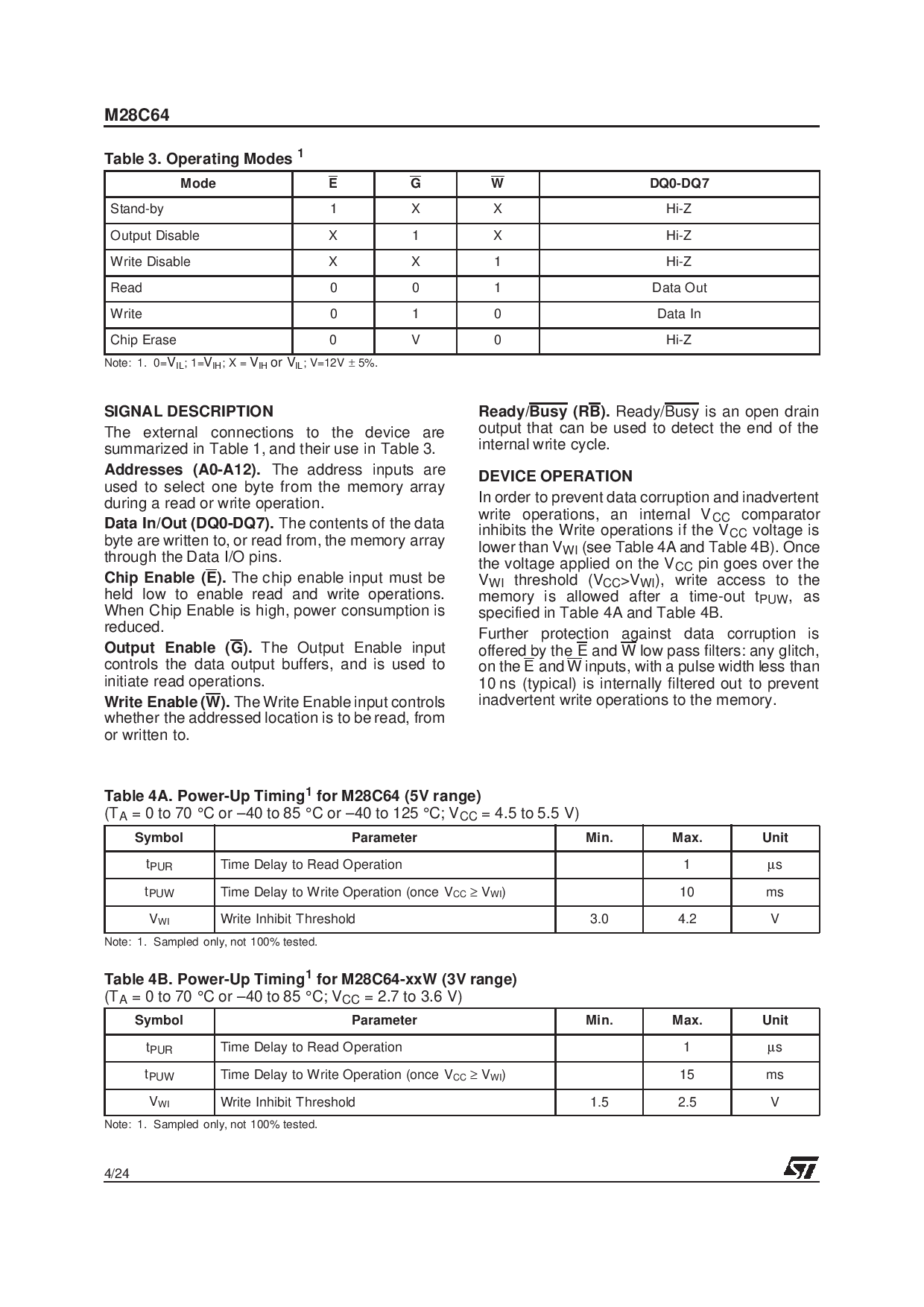

表格 3. 运行 模式

1

便条: 1. 0=

V

IL

;1=

V

IH

;x=

V

IH

或者 V

IL

; V=12V

±

5%.

模式 E G W dq0-dq7

保卫-用 1 X X hi-z

Output 使不能运转 X 1 X hi-z

Write 使不能运转 X X 1 hi-z

读 0 0 1 数据 Out

Write 0 1 0 数据 在

碎片 擦掉 0 V 0 hi-z

信号 描述

这 外部 连接 至 这 设备 是

summarized 在 表格 1, 和 their 使用 在 表格 3.

地址 (a0-a12).

这 地址 输入 是

使用 至 选择 一个 字节 从 这 记忆 排列

在 一个 读 或者 写 运作.

数据 在/输出 (dq0-dq7).

这 内容 的 这 数据

字节 是 写 至, 或者 读 从, 这 记忆 排列

通过 这 数据 i/o 管脚.

碎片 使能 (e).

这 碎片 使能 输入 必须 是

使保持 低 至 使能 读 和 写 行动.

当 碎片 使能 是 高, 电源 消耗量 是

减少.

输出 使能 (g).

这 输出 使能 输入

控制 这 数据 输出 缓存区, 和 是 使用 至

initiate 读 行动.

写 使能 (w).

这 写 使能 输入 控制

whether 这 addressed location 是 至 是 读, 从

或者 写 至.

准备好/busy (rb).

准备好/busy 是 一个 打开 流

输出 那 能 是 使用 至 发现 这 终止 的 这

内部的 写 循环.

设备 运作

在 顺序 至 阻止 数据 corruption 和 inadvertent

写 行动, 一个 内部的 V

CC

比较器

inhibits 这 写 行动 如果 这 V

CC

电压 是

更小的 比 V

WI

(看 表格 4A 和 表格 4b). Once

这 电压 应用 在 这 V

CC

管脚 变得 在 这

V

WI

门槛 (v

CC

>v

WI

), 写 进入 至 这

记忆 是 允许 之后 一个 时间-输出 t

PUW

,作

指定 在 表格 4A 和 表格 4b.

更远 保护 相反 数据 corruption 是

offered 用 这 E 和 W 低 通过 过滤: 任何 glitch,

在 这 E 和 W 输入, 和 一个 脉冲波 宽度 较少 比

10 ns (典型) 是 内部 filtered 输出 至 阻止

inadvertent 写 行动 至 这 记忆.

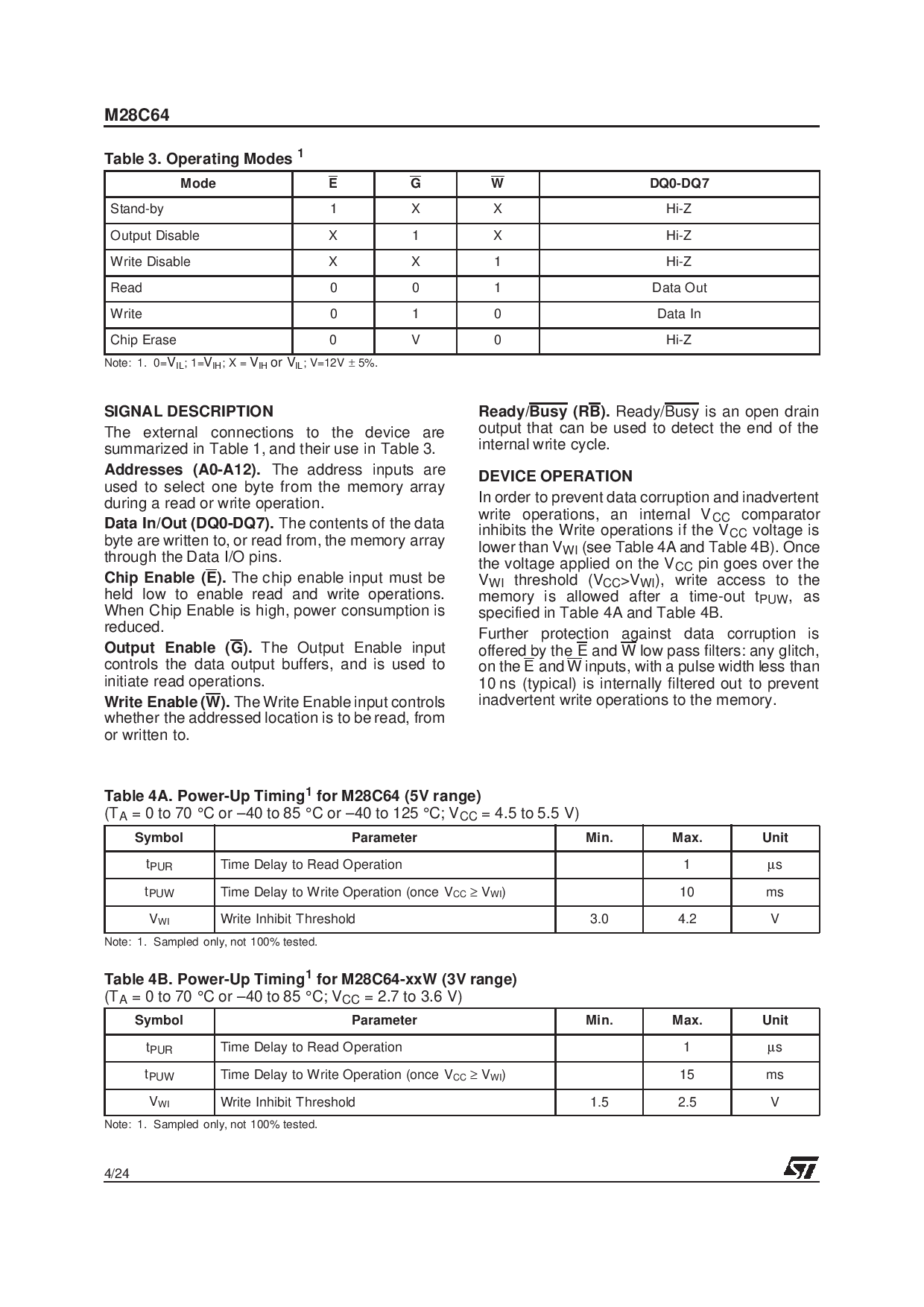

表格 4a. 电源-向上 定时

1

为 M28C64 (5v 范围)

(t

一个

= 0 至 70

°

C 或者 –40 至 85

°

C 或者 –40 至 125

°

c; V

CC

= 4.5 至 5.5 v)

便条: 1. 抽样 仅有的, 不 100% 测试.

表格 4b. 电源-向上 定时

1

为 m28c64-xxw (3v 范围)

(t

一个

= 0 至 70

°

C 或者 –40 至 85

°

c; V

CC

= 2.7 至 3.6 v)

便条: 1. 抽样 仅有的, 不 100% 测试.

标识 参数 Min. 最大值 单位

t

PUR

时间 延迟 至 读 Operation 1

µ

s

t

PUW

时间 延迟 至 Write 运作 (once V

CC

≥

V

WI

)10ms

V

WI

写 Inhibit Threshold 3.0 4.2 V

标识 参数 Min. 最大值 单位

t

PUR

时间 延迟 至 读 Operation 1

µ

s

t

PUW

时间 延迟 至 Write 运作 (once V

CC

≥

V

WI

)15ms

V

WI

写 Inhibit Threshold 1.5 2.5 V