M28C64

6/24

易变的 获得, 和 是 remembered 横过 时期

的 这 电源 正在 止.

这 软件 数据 保护 使能 command

组成 的 这 writing 的 三 明确的 数据 字节

至 三 明确的 记忆 locations (各自 location

正在 在 一个 不同的 页), 作 显示 在 图示 4.

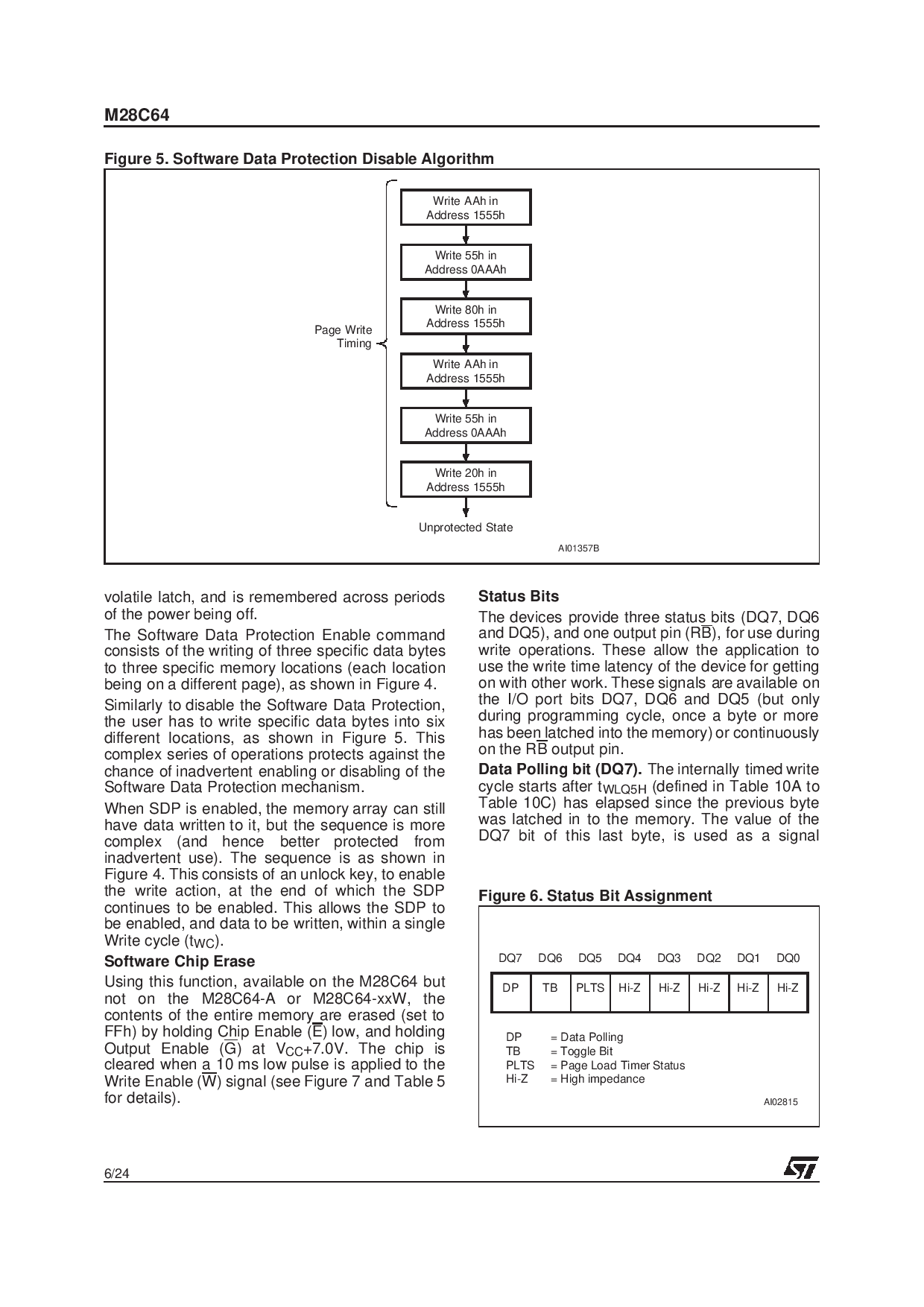

Similarly 至 使不能运转 这 软件 数据 保护,

这 用户 有 至 写 明确的 数据 字节 在 六

不同的 locations, 作 显示 在 图示 5. 这个

complex 序列 的 行动 保护 相反 the

chance 的 inadvertent enabling 或者 disabling 的 这

软件 数据 保护 mechanism.

当 SDP 是 使能, 这 记忆 排列 能 安静的

有 数据 写 至 它, 但是 这 sequence 是 更多

complex (和 hence 更好的 保护 从

inadvertent 使用). 这 sequence 是 作 显示 在

图示 4. 这个 组成 的 一个 unlock 关键, 至 使能

这 写 action, 在 这 终止 的 这个 这 SDP

持续 至 是 使能. 这个 准许 这 SDP 至

是 使能, 和 数据 至 是 写, 在里面 一个 单独的

写 循环 (t

WC

).

软件 碎片 擦掉

使用 这个 函数, 有 在 这 M28C64 但是

不 在 这 m28c64-一个 或者 m28c64-xxw, 这

内容 的 这 全部 记忆 是 erased (设置 至

ffh) 用 支持 碎片 使能 (e) 低, 和 支持

输出 使能 (g) 在 V

CC

+7.0v. 这 碎片 是

cleared 当 一个 10 ms 低 脉冲波 是 应用 至 这

写 使能 (w) 信号 (看 图示 7 和 表格 5

为 详细信息).

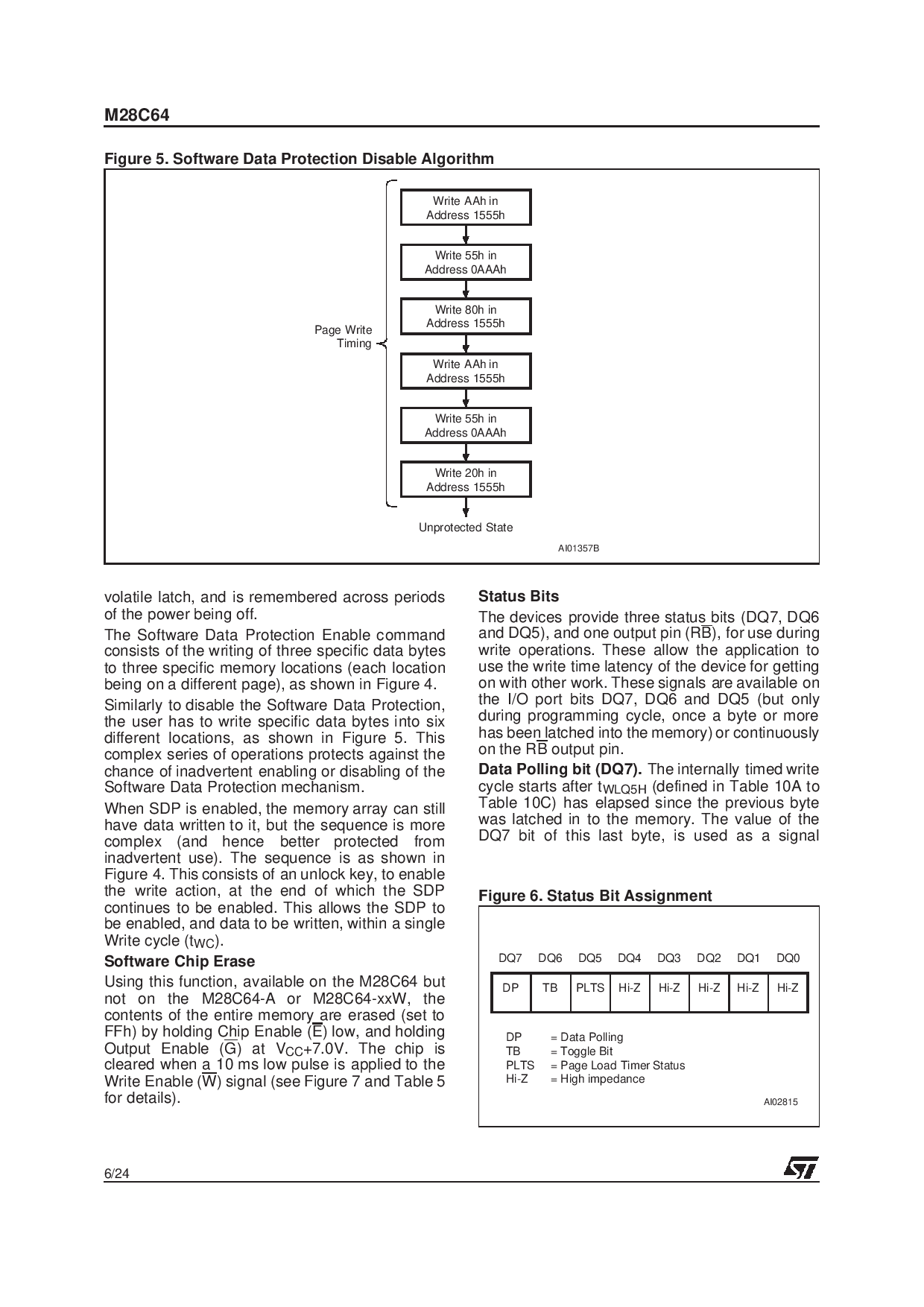

状态 位

这 设备 提供 三 状态 位 (dq7, DQ6

和 dq5), 和 一个 输出 管脚 (rb), 为 使用 在

写 行动. 这些 准许 这 应用 至

使用 这 写 时间 latency 的 这 设备 为 getting

在 和 其它 工作. 这些 信号 是 有 在

这 i/o 端口 位 dq7, DQ6 和 DQ5 (但是 仅有的

在 程序编制 循环, once 一个 字节 或者 更多

有 被 latched 在 这 记忆) 或者 continuously

在 这 RB 输出 管脚.

数据 Polling 位 (dq7).

这 内部 安排时间 写

循环 开始 之后 t

WLQ5H

(定义 在 表格 10A to

表格 10c) 有 消逝 自从 这 previous 字节

是 latched 在 至 这 记忆. 这 值 的 这

DQ7 位 的 this last 字节, 是 使用 作 一个 信号

图示 5. 软件 数据 保护 使不能运转 Algorithm

AI01357B

写 AAh 在

地址 1555h

写 55h 在

地址 0AAAh

写 80h 在

地址 1555h

Unprotected 状态

写 AAh 在

地址 1555h

写 55h 在

地址 0AAAh

写 20h 在

地址 1555h

页 写

定时

图示 6. 状态 位 分派

AI02815

DP TB PLTS hi-z hi-z hi-z hi-z hi-z

DP

TB

PLTS

hi-z

DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0

= 数据

Polling

= Toggle 位

= 页 加载 计时器

状态

= 高 阻抗