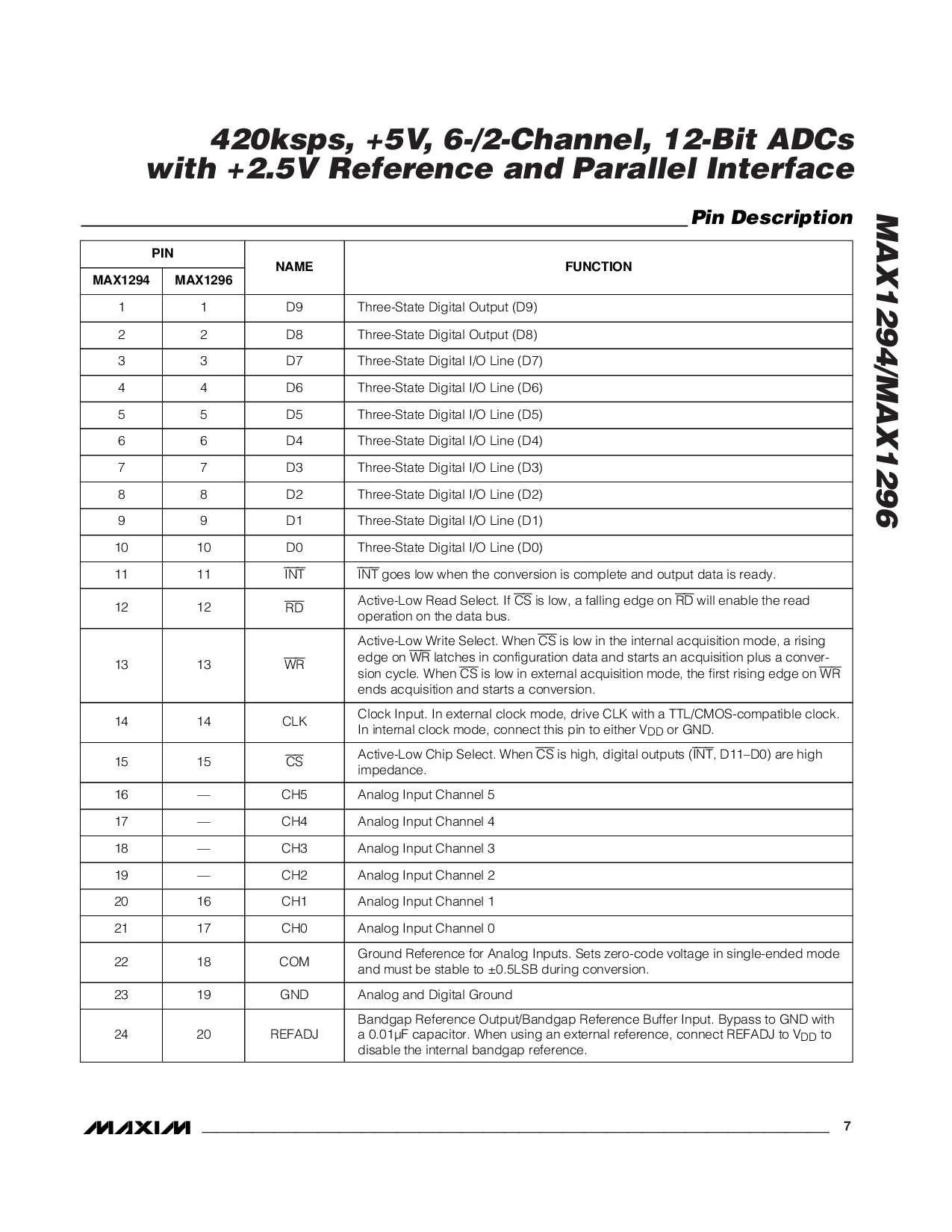

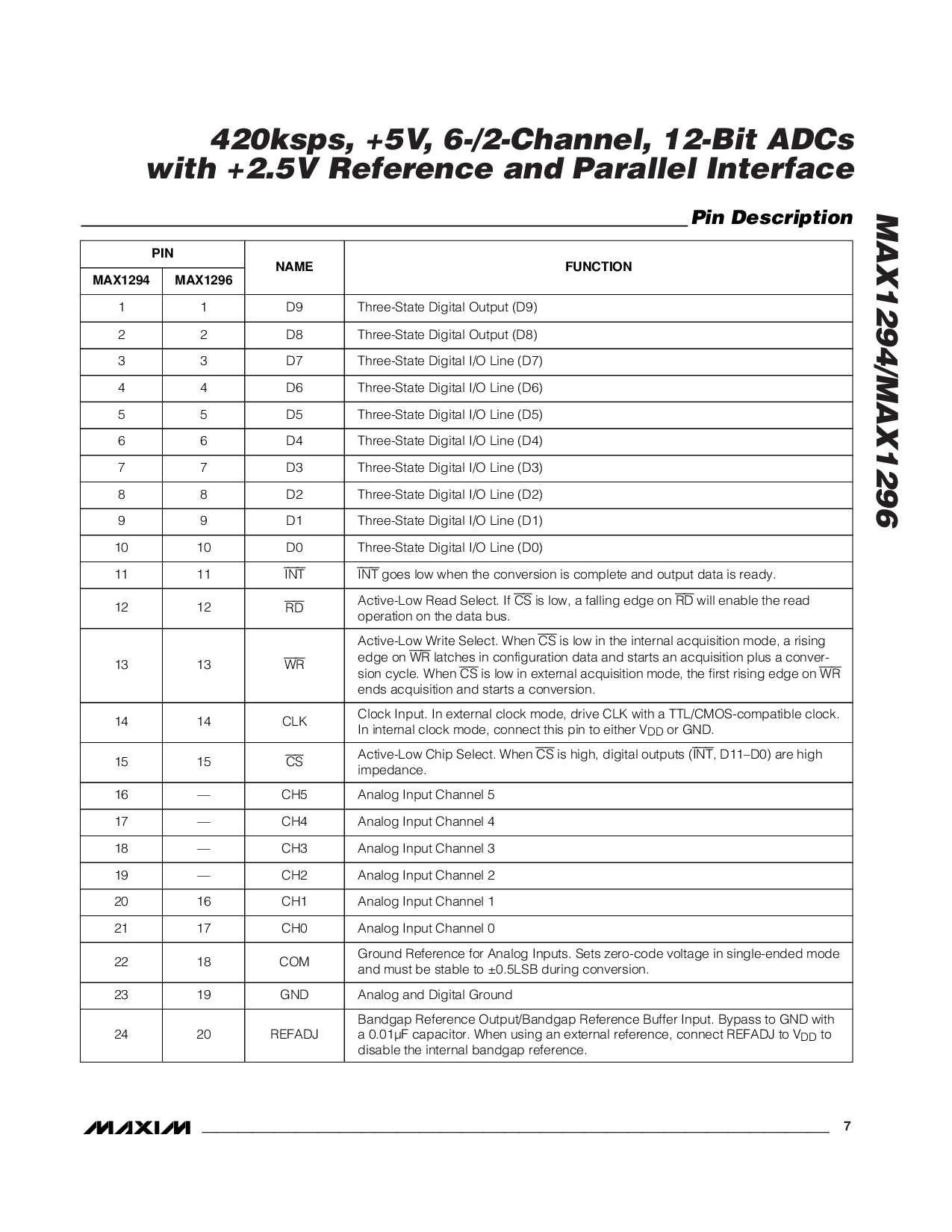

max1294/max1296

420ksps, +5v, 6-/2-频道, 12-位 adcs

和 +2.5v 涉及 和 并行的 接口

_______________________________________________________________________________________ 7

管脚 描述

D01010

INT

1111

RD

1212

WR

1313

CLK1414

D466

D377

D288

D199

D555

D644

1

D733

D822

D9

1

三-状态 数字的 i/o 线条 (d0)

INT

变得 低 当 这 转换 是 完全 和 输出 数据 是 准备好.

起作用的-低 读 选择. 如果

CS

是 低, 一个 下落 边缘 在

RD

将 使能 这 读

运作 在 这 数据 总线.

起作用的-低 写 选择. 当

CS

是 低 在 这 内部的 acquisition 模式, 一个 rising

边缘 在

WR

latches 在 配置 数据 和 开始 一个 acquisition 加 一个 变换器-

sion 循环. 当

CS

是 低 在 外部 acquisition 模式, 这 第一 rising 边缘 在

WR

ends acquisition 和 开始 一个 转换.

时钟 输入. 在 外部 时钟 模式, 驱动 clk 和 一个 ttl/cmos-兼容 时钟.

在 内部的 时钟 模式, 连接 这个 管脚 至 也 v

DD

或者 地.

三-状态 数字的 i/o 线条 (d4)

三-状态 数字的 i/o 线条 (d3)

三-状态 数字的 i/o 线条 (d2)

三-状态 数字的 i/o 线条 (d1)

三-状态 数字的 i/o 线条 (d5)

三-状态 数字的 i/o 线条 (d6)

三-状态 数字的 i/o 线条 (d7)

三-状态 数字的 输出 (d8)

三-状态 数字的 输出 (d9)

GND1923

REFADJ2024

CH2—19

CH11620

CH01721

COM1822

CH3—18

CH4—17

CH5—16

CS

1515

相似物 和 数字的 地面

bandgap 涉及 输出/bandgap 涉及 缓存区 输入. 绕过 至 地 和

一个 0.01µf 电容. 当 使用 一个 外部 涉及, 连接 refadj 至 v

DD

至

使不能运转 这 内部的 bandgap 涉及.

相似物 输入 频道 2

相似物 输入 频道 1

相似物 输入 频道 0

地面 涉及 为 相似物 输入. sets 零-代号 电压 在 单独的-结束 模式

和 必须 是 稳固的 至 ±0.5lsb 在 转换.

相似物 输入 频道 3

相似物 输入 频道 4

相似物 输入 频道 5

起作用的-低 碎片 选择. 当

CS

是 高, 数字的 输出 (

INT

, d11–d0) 是 高

阻抗.

管脚

MAX1296MAX1294

名字 函数