cy7c4425/4205/4215

cy7c4225/4235/4245

3

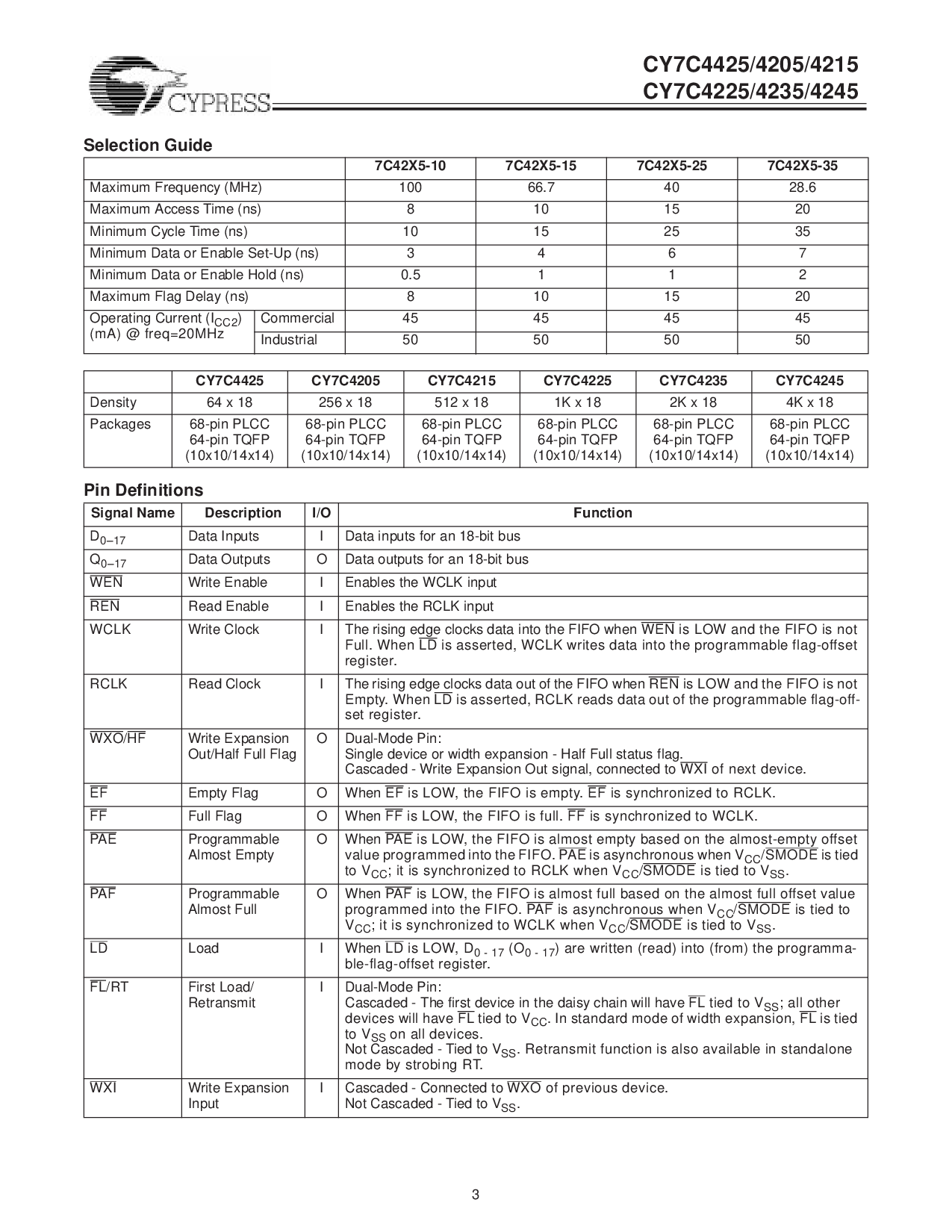

选择 手册

7c42x5-10 7c42x5-15 7c42x5-25 7c42x5-35

最大 频率 (mhz) 100 66.7 40 28.6

最大 进入 时间 (ns) 8 10 15 20

最小 循环 时间 (ns) 10 15 25 35

最小 数据 或者 使能 设置-向上 (ns) 3 4 6 7

最小 数据 或者 使能 支撑 (ns) 0.5 1 1 2

最大 标记 延迟 (ns) 8 10 15 20

运行 电流 (i

CC2

)

(毫安) @ freq=20mhz

商业的 45 45 45 45

工业的 50 50 50 50

CY7C4425 CY7C4205 CY7C4215 CY7C4225 CY7C4235 CY7C4245

密度 64 x 18 256 x 18 512 x 18 1k x 18 2k x 18 4k x 18

包装 68-管脚 plcc

64-管脚 tqfp

(10x10/14x14)

68-管脚 plcc

64-管脚 tqfp

(10x10/14x14)

68-管脚 plcc

64-管脚 tqfp

(10x10/14x14)

68-管脚 plcc

64-管脚 tqfp

(10x10/14x14)

68-管脚 plcc

64-管脚 tqfp

(10x10/14x14)

68-管脚 plcc

64-管脚 tqfp

(10x10/14x14)

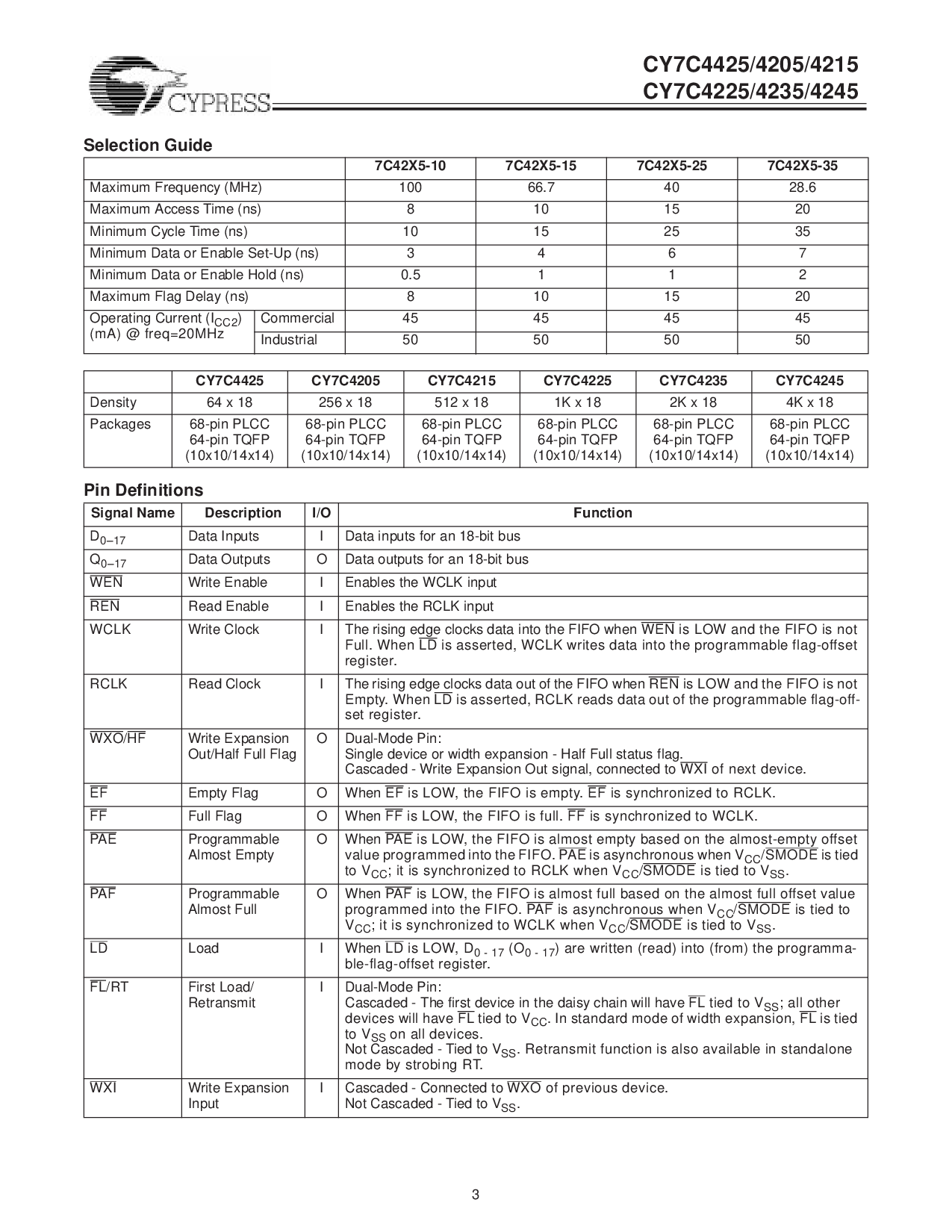

管脚 定义

信号 名字 描述 i/o 函数

D

0–17

数据 输入 I 数据 输入 为 一个 18-位 总线

Q

0–17

数据 输出 O 数据 输出 为 一个 18-位 总线

WEN 写 使能 I 使能 这 wclk 输入

REN 读 使能 I 使能这 rclk 输入

WCLK 写 时钟 I 这 rising 边缘 clocks 数据 在 这 先进先出 当 wen是 低 和 这 先进先出 是 不

全部. 当 ld

是 asserted, wclk 写 数据 在 这 可编程序的 标记-补偿

寄存器.

RCLK 读 时钟 I 这 rising 边缘 clocks 数据 输出 的 这 先进先出 当 ren是 低 和 这 先进先出 是 不

empty. 当 ld

是 asserted, rclk 读 数据 输出 的 这 可编程序的 标记-止-

设置 寄存器.

WXO/hf 写 expansion

输出/half 全部 标记

O 双-模式 管脚:

单独的 设备 或者 宽度 expansion - half 全部状态 标记.

倾泻 - 写 expansion 输出 信号, 连接 至 wXI

的 next 设备.

EF empty 标记 O 当 ef是 低, 这 先进先出 是 empty. ef是 同步 至 rclk.

FF 全部 标记 O 当 ff是 低, 这 先进先出 是 全部. ff是 同步 至 wclk.

PAE 可编程序的

almost empty

O 当 pae是 低, 这 先进先出 是 almost empty 为基础 在 这 almost-empty 补偿

值 编写程序 在 这 先进先出. pae

是 异步的 当 v

CC

/smode是 系

至 v

CC

; 它 是 同步 至 rclk 当 v

CC

/smode是 系 至 v

SS

.

PAF 可编程序的

almost 全部

O 当 paf是 低, 这 先进先出 是 almost 全部 为基础 在 这 almost 全部 补偿 值

编写程序 在 这 先进先出. paf

是 异步的 当 v

CC

/smode是 系 至

V

CC

; 它 是 同步 至 wclk 当 v

CC

/smode是 系 至 v

SS

.

LD 加载 I 当 ld是 低, d

0 - 17

(o

0 - 17

) 是 写 (读) 在 (从) 这 programma-

ble-标记-补偿 寄存器.

FL/rt 第一 加载/

Retransmit

I 双-模式 管脚:

倾泻 - 这 第一设备 在 这 daisy chain 将 有 fl

系 至 v

SS

; 所有 其它

设备 将 有 fl

系 至 v

CC

. 在 标准 模式 的 宽度 expansion, fl是 系

至 v

SS

在 所有 设备.

不 cascaded - tied 至 v

SS

. retransmit 函数 是 也 有 在 standalone

模式 用 strobing rt.

WXI 写 expansion

输入

I 倾泻 - 连接 至 wxo的 previous 设备.

不 cascaded - tied 至 v

SS

.