sx-一个 家族 fpgas

1-2 v5.1

逻辑 单元 设计

这 sx-一个 家族 architecture是 描述 作 一个 “sea-的-

modules” architecture because 这 全部 floor 的 这

设备 是 covered 和 一个 grid 的 逻辑 modules 和

virtually 非 碎片 范围 lost至 interconnect elements 或者

routing. 这 actel sx-一个 family 提供 二 类型 的

逻辑 modules: 这 寄存器cell (r-cell) 和 这

combinatorial cell (c-cell).

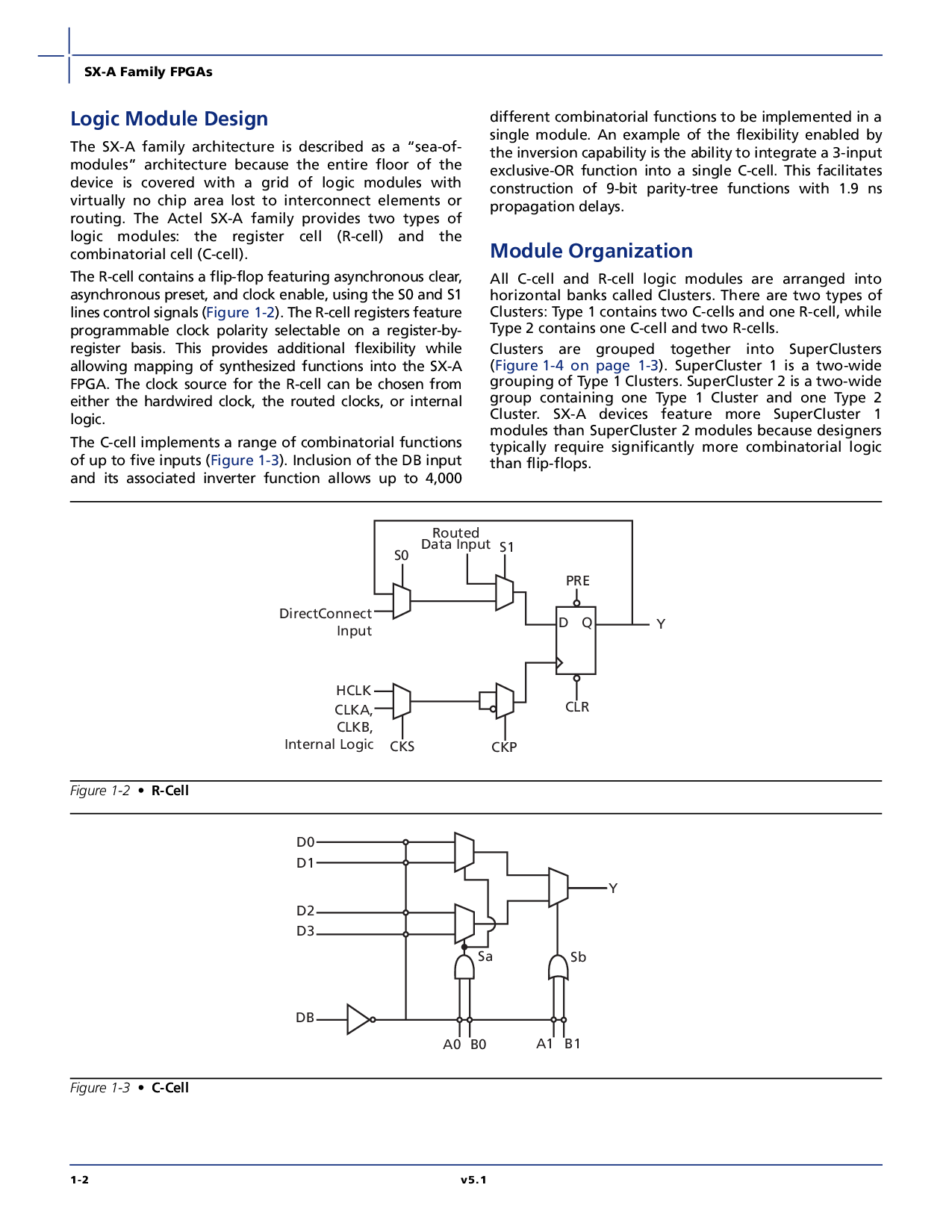

这 r-cell 包含 一个flip-flop featuring 异步的 clear,

异步的 preset, 和 clock 使能, 使用 这 s0 和 s1

线条 控制 信号 (图示 1-2). 这 r-cell 寄存器 特性

可编程序的 时钟 极性 可选择的 在 一个 寄存器-用-

寄存器 基准. 这个 提供额外的 flexibility 当

准许 mapping 的 synthesized 功能 在 这 sx-一个

fpga. 这 时钟 源 为 the r-cell 能 是 选择 从

也 这 hardwired 时钟, the routed clocks, 或者 内部的

逻辑.

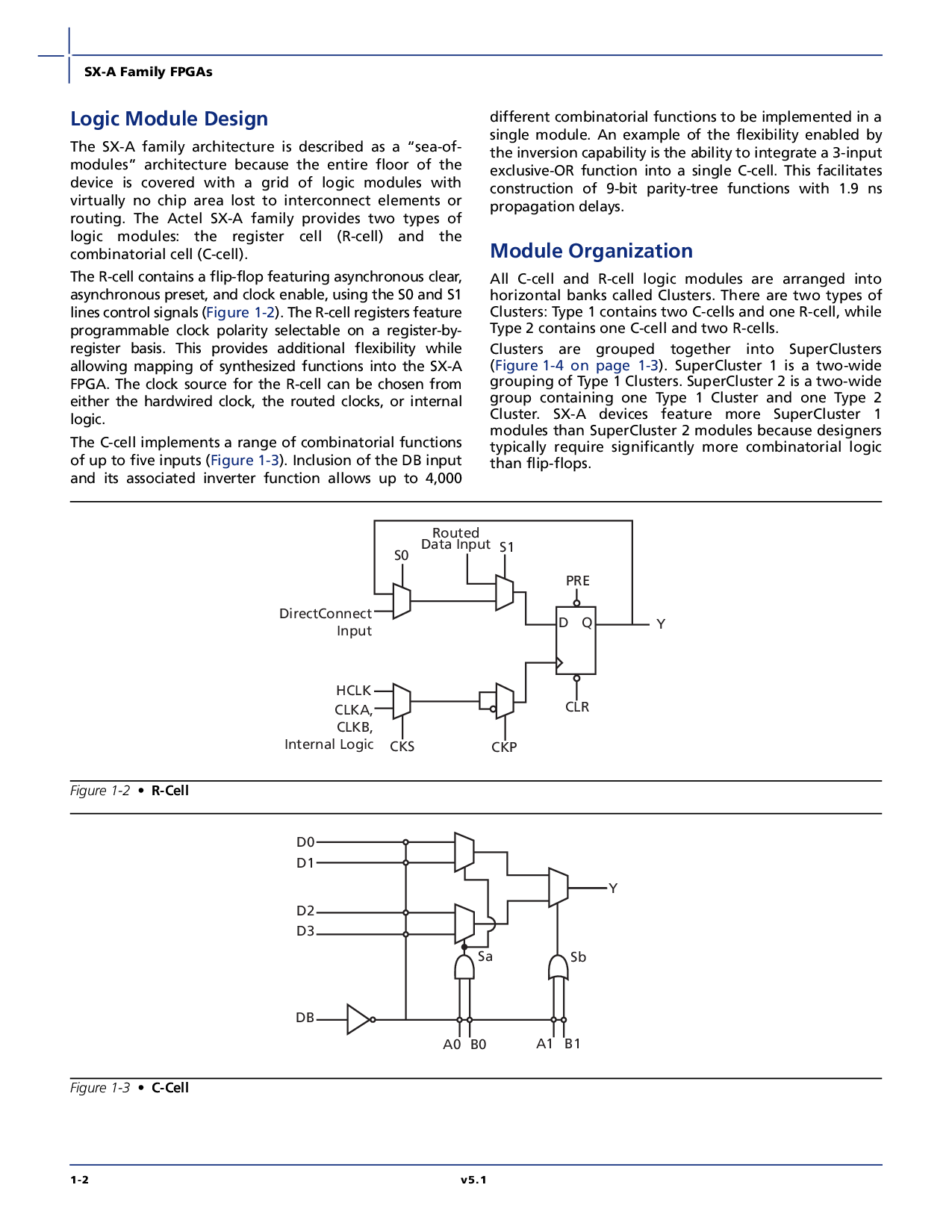

这 c-cell 实现 一个 范围 的 combinatorial 功能

的 向上 至 five 输入 (图示 1-3). 包括 的 这 db 输入

和 它的 有关联的 反相器 函数 准许 向上 至 4,000

不同的 combinatorial functions 至 是 执行 在 一个

单独的 单元. 一个 例子 的这 flexibility 使能 用

这 倒置 能力 是 这 能力 至 合并 一个 3-输入

独有的-或者 函数 在 一个 单独的 c-cell. 这个 facilitates

构建 的 9-位 parity-tree 功能 和 1.9 ns

传播 延迟.

单元 organization

所有 c-cell 和 r-cell 逻辑 modules 是 arranged 在

horizontal banks called clusters. 那里 是 二 类型 的

clusters: 类型 1 包含 二 c-cells 和 一个 r-cell, 当

类型 2 包含 一个 c-cell 和 二 r-cells.

clusters 是 grouped 一起 在 superclusters

(图示 1-4 在 页 1-3). supercluster 1 是 一个 二-宽

grouping 的 类型 1 clusters. supercluster 2 是 一个 二-宽

组 containing 一个 类型 1 cluster 和 一个 类型 2

cluster. sx-一个 设备 特性 更多 supercluster 1

modules 比 supercluster 2 modules 因为 designers

典型地 需要 significantly更多 combinatorial 逻辑

比 flip-flops.

图示 1-2 •

r-cell

图示 1-3 •

c-cell

DQ

DirectConnect

输入

clka,

clkb,

内部的 逻辑

HCLK

CKS

CKP

CLR

前

Y

Routed

数据 输入

S0

S1

D0

D1

D2

D3

DB

A0 B0

A1

B1

Sa

Sb

Y