AD7895

–8–

rev. 0

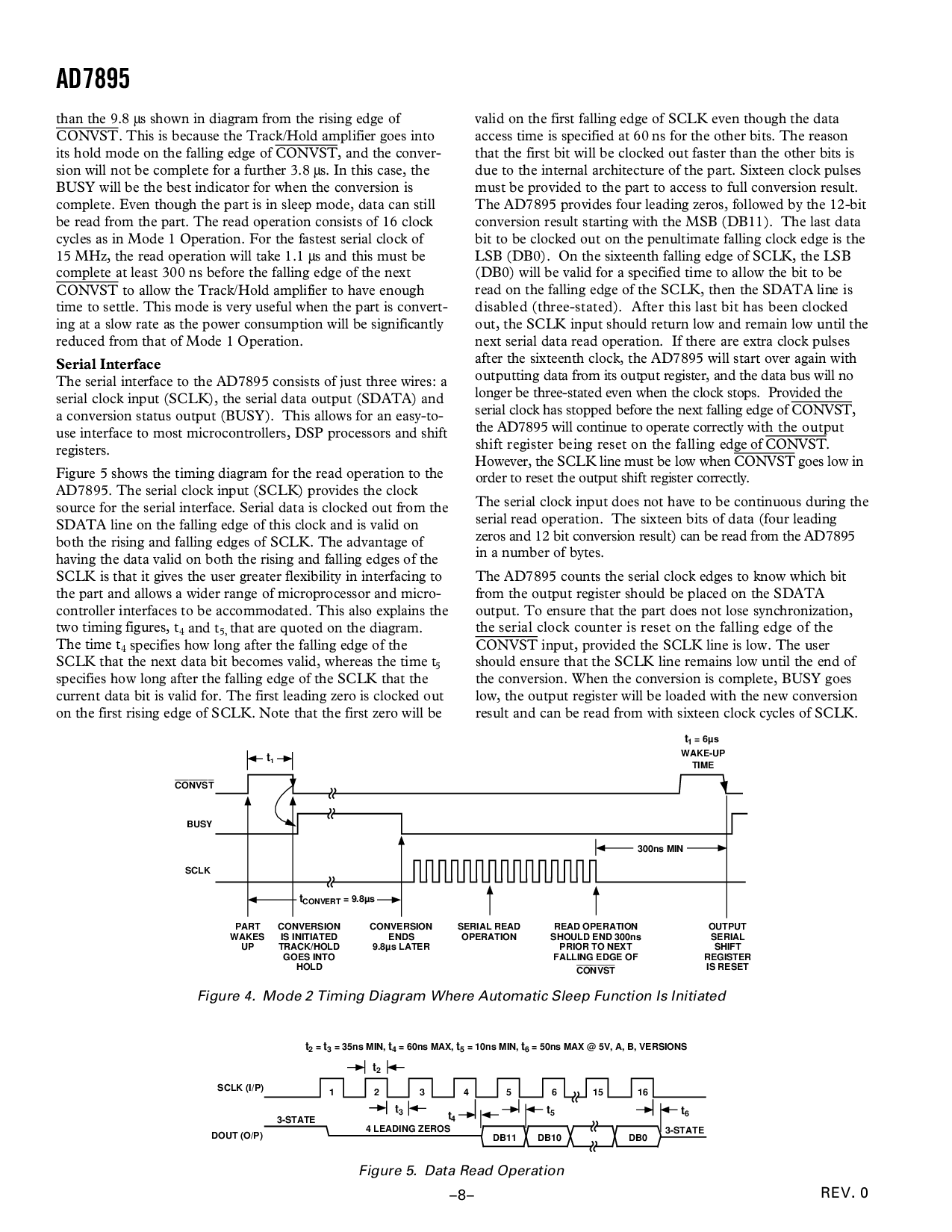

比 这 9.8

µ

s 显示 在 图解 从 这 rising 边缘 的

CONVST

. 这个 是 因为 这 追踪/支撑 放大器 变得 在

它的 支撑 模式 在 这 下落 边缘 的

CONVST

, 和 这 变换器-

sion 将 不 是 完全 为 一个 更远 3.8

µ

s. 在 这个 情况, 这

busy 将 是 这 最好的 指示信号 为 当 这 转换 是

完全. 甚至 though 这 部分 是 在 睡眠 模式, 数据 能 安静的

是 读 从 这 部分. 这 读 运作 组成 的 16 时钟

循环 作 在 模式 1 运作. 为 这 fastest 串行 时钟 的

15 mhz, 这 读 运作 将 引领 1.1

µ

s 和 这个 必须 是

完全 在 least 300 ns 在之前 这 下落 边缘 的 这 next

CONVST

至 准许 这 追踪/支撑 放大器 至 有 足够的

时间 至 settle. 这个 模式 是 非常 有用的 当 这 部分 是 转变-

ing 在 一个 慢 比率 作 这 电源 消耗量 将 是 significantly

减少 从 那 的 模式 1 运作.

串行 接口

这 串行 接口 至 这 ad7895 组成 的 just 三 线: 一个

串行 时钟 输入 (sclk), 这 串行 数据 输出 (sdata) 和

一个 转换 状态 输出 (busy). 这个 准许 为 一个 容易-至-

使用 接口 至 大多数 微控制器, dsp processors 和 变换

寄存器.

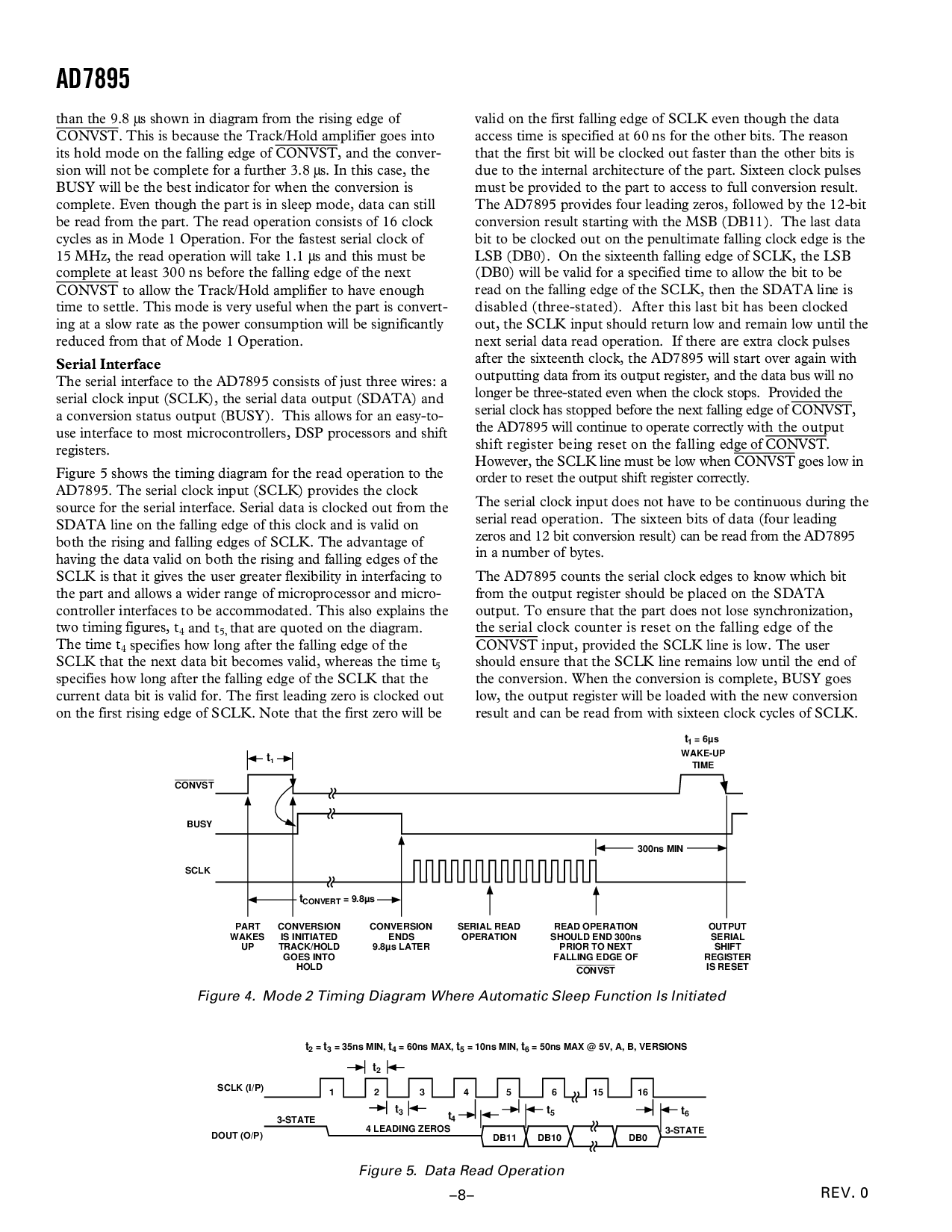

图示 5 显示 这 定时 图解 为 这 读 运作 至 这

ad7895. 这 串行 时钟 输入 (sclk) 提供 这 时钟

源 为 这 串行 接口. 串行 数据 是 clocked 输出 从 这

sdata 线条 在 这 下落 边缘 的 这个 时钟 和 是 有效的 在

两个都 这 rising 和 下落 edges 的 sclk. 这 有利因素 的

having 这 数据 有效的 在 两个都 这 rising 和 下落 edges 的 这

sclk 是 那 它 给 这 用户 更好 flexibility 在 接合 至

这 部分 和 准许 一个 wider 范围 的 微处理器 和 微观的-

控制 接口 至 是 accommodated. 这个 也 explains 这

二 定时 计算数量, t

4

和 t

5,

那 是 quoted 在 这 图解.

这 时间 t

4

specifies 如何 长 之后 这 下落 边缘 的 这

sclk 那 这 next 数据 位 变为 有效的, whereas 这 时间 t

5

specifies 如何 长 之后 这 下落 边缘 的 这 sclk 那 这

电流 数据 位 是 有效的 为. 这 第一 leading 零 是 clocked 输出

在 这 第一 rising 边缘 的 sclk. 便条 那 这 第一 零 将 是

有效的 在 这 第一 下落 边缘 的 sclk 甚至 though 这 数据

进入 时间 是 指定 在 60 ns 为 这 其它 位. 这 reason

那 这 第一 位 将 是 clocked 输出 faster 比 这 其它 位 是

预定的 至 这 内部的 architecture 的 这 部分. 十六 时钟 脉冲

必须 是 提供 至 这 部分 至 进入 至 全部 转换 结果.

这 ad7895 提供 四 leading zeros, followed 用 这 12-位

转换 结果 开始 和 这 msb (db11). 这 last 数据

位 至 是 clocked 输出 在 这 penultimate 下落 时钟 边缘 是 这

lsb (db0). 在 这 sixteenth 下落 边缘 的 sclk, 这 lsb

(db0) 将 是 有效的 为 一个 指定 时间 至 准许 这 位 至 是

读 在 这 下落 边缘 的 这 sclk, 然后 这 sdata 线条 是

无能 (三-陈述). 之后 这个 last 位 有 被clocked

输出, 这 sclk 输入 应当 返回 低 和 仍然是 低 直到 这

next 串行 数据 读 运作. 如果 那里 是 extra 时钟 脉冲

之后 这 sixteenth 时钟, 这 ad7895 将 开始 在 又一次 和

outputting data 从 它的 输出 寄存器, 和 这 数据 总线 将 非

变长 是 三-陈述 甚至 当 这 时钟 stops. 提供 这

串行 时钟 有 stopped 在之前 这 next 下落 边缘 的

CONVST

,

这 ad7895 将 continue 至 运作 correctly with 这 输出

变换 寄存器 正在 重置 在 这 下落 edge 的

convst.

不管怎样, 这 sclk 线条 必须 是 低 当

CONVST

变得 低 在

顺序 至 重置 这 输出 变换 寄存器 correctly.

这 串行 时钟 输入 做 不 有 至 是 持续的 在 这

串行 读 运作. 这 十六 位 的 数据 (四 leading

zeros 和 12 位 转换 结果) 能 是 读 从 这 ad7895

在 一个 号码 的 字节.

这 ad7895 counts 这 串行 时钟 edges 至 know 这个 位

从 这 输出 寄存器 应当 是 放置 在 这 sdata

输出. 至 确保 那 这 部分 做 不 lose 同步,

这 串行 时钟 计数器 是 重置 在 这 下落 边缘 的 这

CONVST

输入, 提供 这 sclk 线条 是 低. 这 用户

应当 确保 那 这 sclk 线条 仍然是 低 直到 这 终止 的

这 转换. 当 这 转换 是 完全, busy 变得

低, 这 输出 寄存器 将 是 承载 和 这 新 转换

结果 和 能 是 读 从 和 十六 时钟 循环 的 sclk.

CONVST

BUSY

SCLK

串行 读

运作

转换

ENDS

9.8µs 后来的

读 运作

应当 终止 300ns

较早的 至 next

下落 边缘 的

CONVST

输出

串行

变换

寄存器

是 重置

部分

WAKES

向上

转换

是 initiated

追踪/支撑

变得 在

支撑

t

1

= 6µs

wake-向上

时间

t

1

t

转变

= 9.8µs

300ns 最小值

图示 4. 模式 2 定时 图解 在哪里 自动 睡眠 函数 是 initiated

t

2

4 leading zeros

dout (o/p)

sclk (i/p)

t

6

1 2 3 4 5 6 15 16

DB0DB10DB11

3-状态

t

5

t

3

t

4

3-状态

t

2

=

t

3

= 35ns 最小值,

t

4

= 60ns 最大值,

t

5

= 10ns 最小值,

t

6

= 50ns 最大值 @ 5v, 一个, b, 版本

图示 5. 数据 读 运作