飞利浦 半导体 产品 规格

74LVC163

presettable 同步的 4-位 二进制的 计数器;

同步的 重置

1998 将 20

8

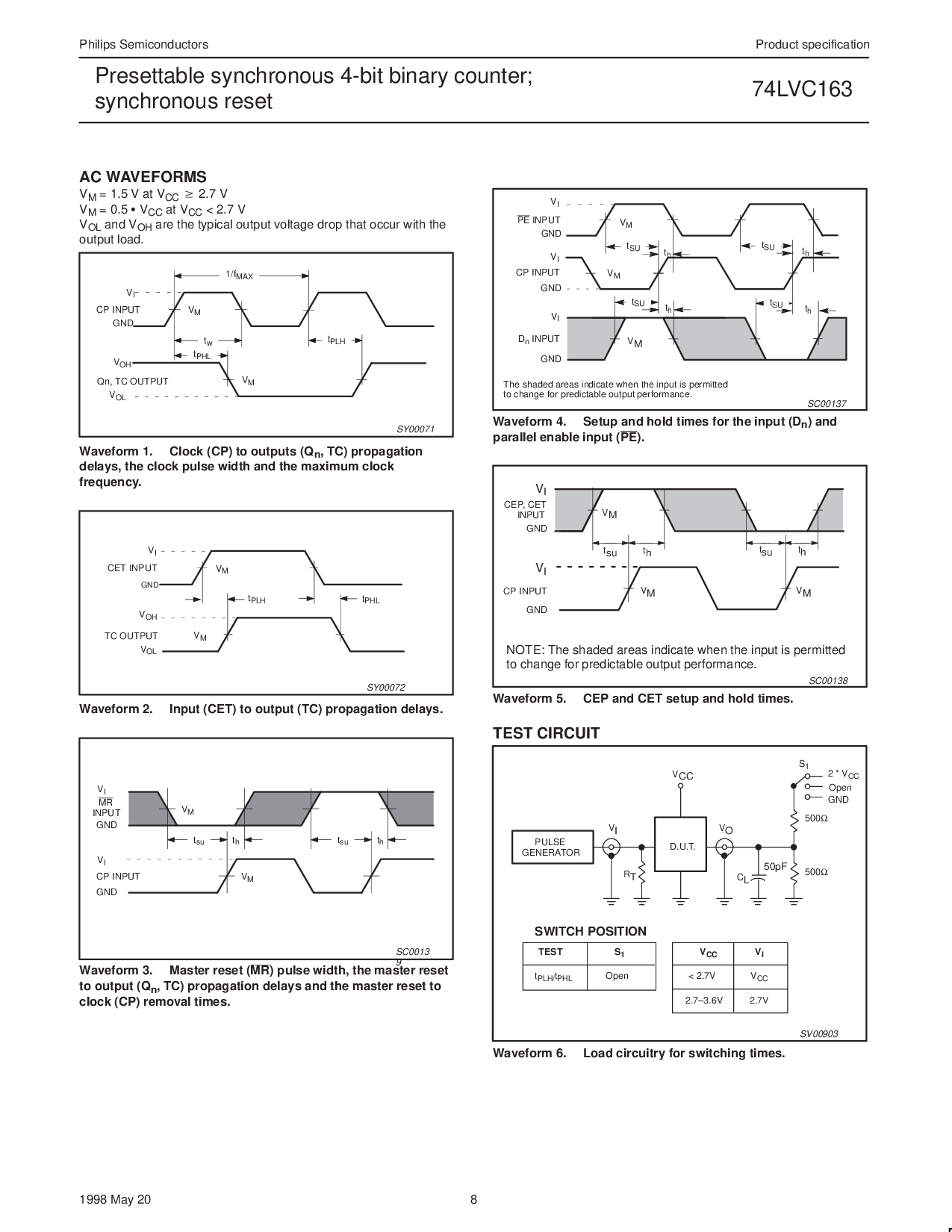

交流 波形

V

M

= 1.5 v 在 v

CC

2.7 v

V

M

= 0.5

V

CC

在 v

CC

< 2.7 v

V

OL

和 v

OH

是 这 典型 输出 电压 漏出 那 出现 和 这

输出 加载.

V

M

V

M

1/f

最大值

t

w

t

PLH

t

PHL

cp 输入

qn, tc 输出

SY00071

地

V

I

V

OH

V

OL

波形 1. 时钟 (cp) 至 输出 (q

n

, tc) 传播

延迟, 这 时钟 脉冲波 宽度 和 这 最大 时钟

频率.

V

M

t

PLH

t

PHL

cet 输入

tc 输出

V

M

V

I

地

V

OH

V

OL

SY00072

波形 2. 输入 (cet) 至 输出 (tc) 传播 延迟.

V

M

V

M

t

su

t

su

t

h

t

h

MR

输入

cp 输入

SC0013

9

V

I

地

V

I

地

波形 3. 主控 重置 (mr) 脉冲波 宽度, 这 主控 重置

至 输出 (q

n

, tc) 传播 延迟 和 这 主控 重置 至

时钟 (cp) 除去 时间.

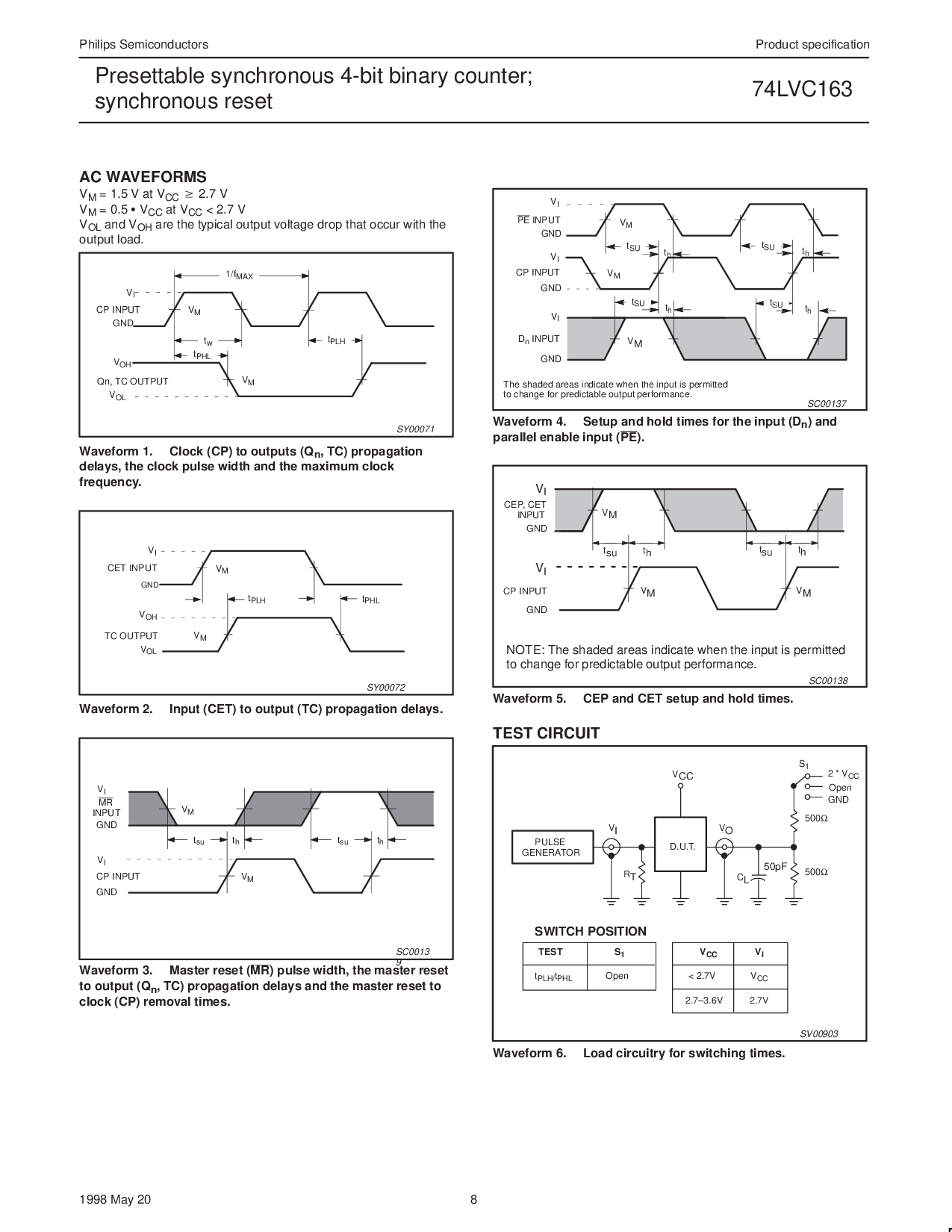

这 shaded areas 表明 当 这 输入 是 permitted

至 改变 为 predictable 输出 效能.

t

h

t

h

V

M

V

M

V

M

V

I

V

I

V

I

地

地

地

PE

输入

cp 输入

D

n

输入

t

SU

t

SU

t

h

t

SU

t

h

t

SU

SC00137

波形 4. 建制 和 支撑 时间 为 这 输入 (d

n

) 和

并行的 使能 输入 (pe

).

便条: 这 shaded areas 表明 当 这 输入 是 permitted

至 改变 为 predictable 输出 效能.

V

M

V

M

V

M

t

su

t

h

t

su

t

h

SC00138

V

I

V

I

地

地

cep, cet

输入

cp 输入

波形 5. cep 和 cet 建制 和 支撑 时间.

测试 电路

转变 位置

脉冲波

发生器

R

T

V

I

d.u.t.

V

O

C

L

V

CC

500

Ω

打开

地

S

1

V

CC

V

I

< 2.7v V

CC

测试 S

1

t

plh/

t

PHL

打开

2.7v2.7–3.6v

50pF

500

Ω

2 * v

CC

SV00903

波形 6. 加载 电路系统 为 切换 时间.