max536/max537

校准, 四方形, 12-位

电压-输出 dacs 和 串行 接口

4 _______________________________________________________________________________________

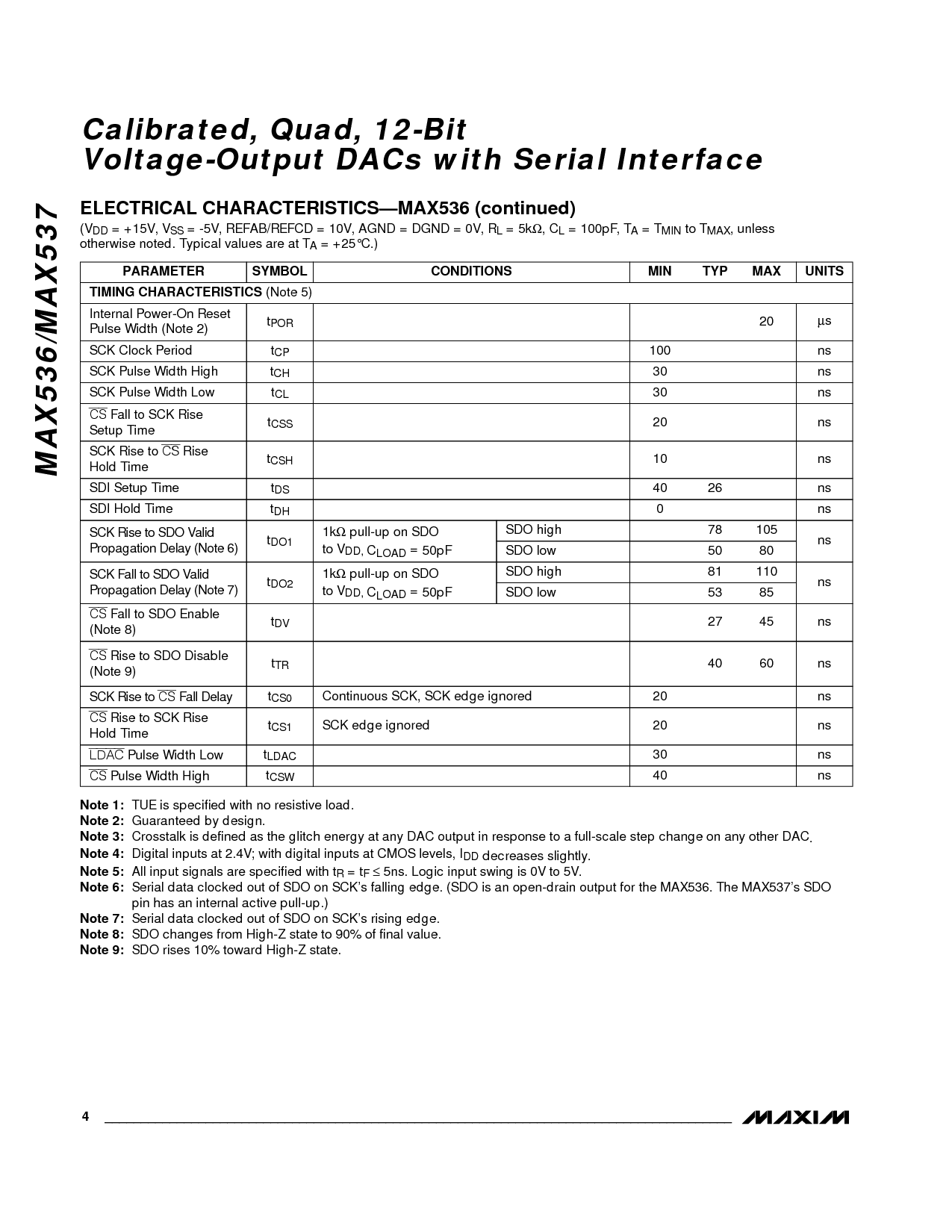

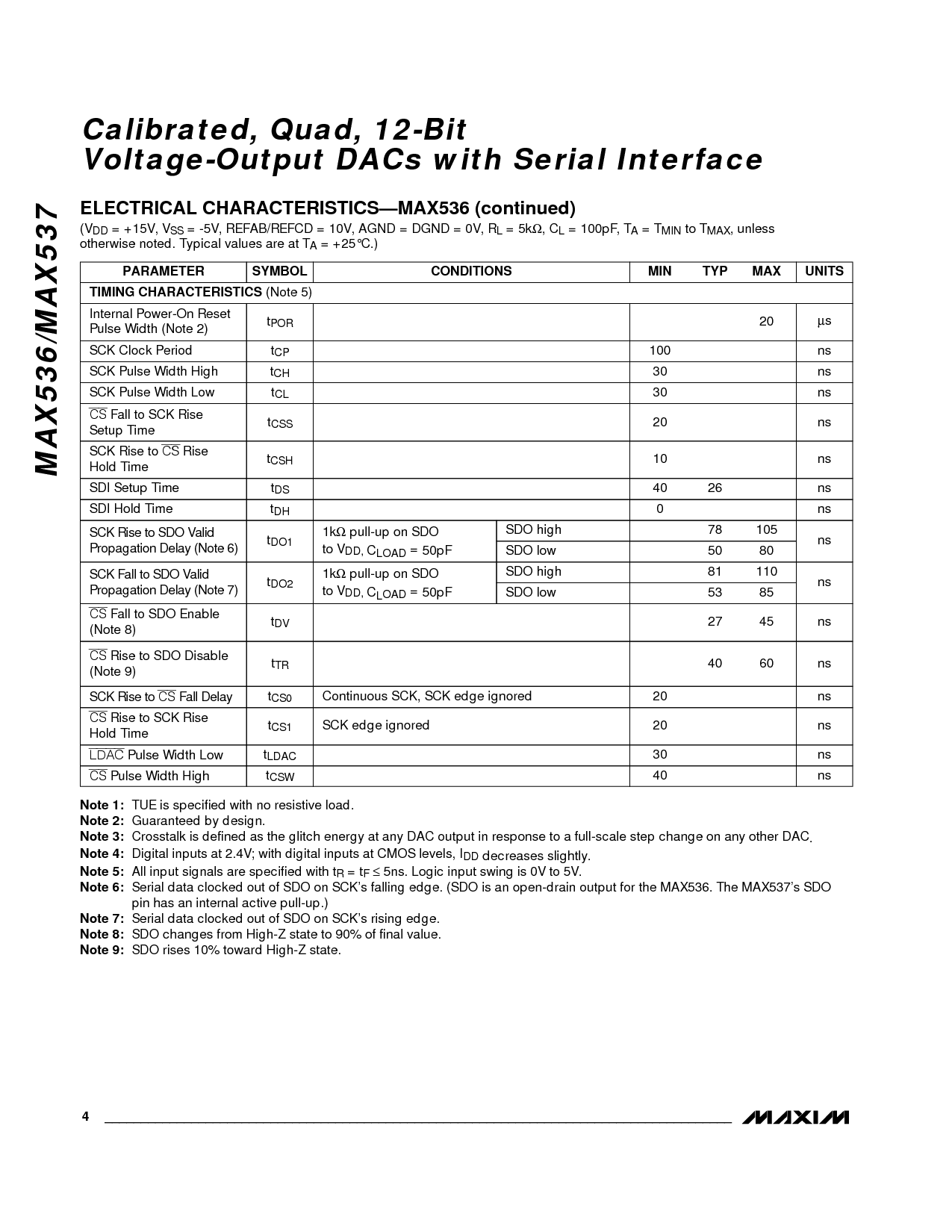

电的 characteristics—max536 (持续)

(v

DD

= +15v, v

SS

= -5v, refab/refcd = 10v, agnd = dgnd = 0v, r

L

= 5k

Ω

, c

L

= 100pf, t

一个

= t

最小值

至 t

最大值

, 除非

否则 指出. 典型 值 是 在 t

一个

= +25°c.)

参数

标识 情况 最小值 典型值 最大值 单位

t

POR

20

µ

s

sck 时钟 时期 t

CP

100 ns

sck 脉冲波 宽度 高 t

CH

30 ns

sck 脉冲波 宽度 低 t

CL

30 ns

t

CSS

20 ns

t

CSH

10 ns

sdi 建制 时间 t

DS

40 26 ns

sdi 支撑 时间 t

DH

0 ns

t

DO1

1k

Ω

拉-向上 在 sdo

至 v

dd,

C

加载

=

50pF

sdo 高 78 105

ns

sdo 低 50 80

sck 下降 至 sdo 有效的

传播 延迟 (便条 7)

t

DO2

1k

Ω

拉-向上 在 sdo

至 v

dd,

C

L

OAD

=

50pF

sdo 高 81 110

ns

sdo 低 53 85

t

DV

27 45 ns

t

TR

40 60 ns

sck 上升 至

CS

下降 延迟

t

CS0

持续的 sck, sck 边缘 ignored 20 ns

t

CS1

sck 边缘 ignored 20 ns

LDAC

脉冲波 宽度 低

t

LDAC

30 ns

CS

脉冲波 宽度 高

t

CSW

40 ns

内部的 电源-在 重置

脉冲波 宽度 (便条 2)

CS

下降 至 sck 上升

建制 时间

sck 上升 至

CS

上升

支撑 时间

sck 上升 至 sdo 有效的

传播 延迟 (便条 6)

CS

下降 至 sdo 使能

(便条 8)

CS

上升 至 sdo 使不能运转

(便条 9)

CS

上升 至 sck 上升

支撑 时间

便条 1:

tue 是 指定 和 非 resistive 加载.

便条 2:

有保证的 用 设计.

便条 3:

串扰 是 定义 作 这 glitch 活力 在 任何 dac 输出 在 回馈 至 一个 全部-规模 步伐 改变 在 任何 其它 dac

.

便条 4:

数字的 输入 在 2.4v; 和 数字的 输入 在 cmos 水平, i

DD

减少 slightly.

便条 5:

所有 输入 信号 是 指定 和 t

R

= t

F

≤

5ns. 逻辑 输入 摆动 是 0v 至 5v.

便条 6:

串行 数据 clocked 输出 的 sdo 在 sck’s 下落 边缘. (sdo 是 一个 打开-流 输出 为 这 max536. 这 max537’s sdo

管脚 有 一个 内部的 起作用的 拉-向上.)

便条 7:

串行 数据 clocked 输出 的 sdo 在 sck’s rising 边缘.

便条 8:

sdo 改变 从 高-z 状态 至 90% 的 最终 值.

便条 9:

sdo rises 10% 对着 高-z 状态.

定时 特性

(便条 5)