8

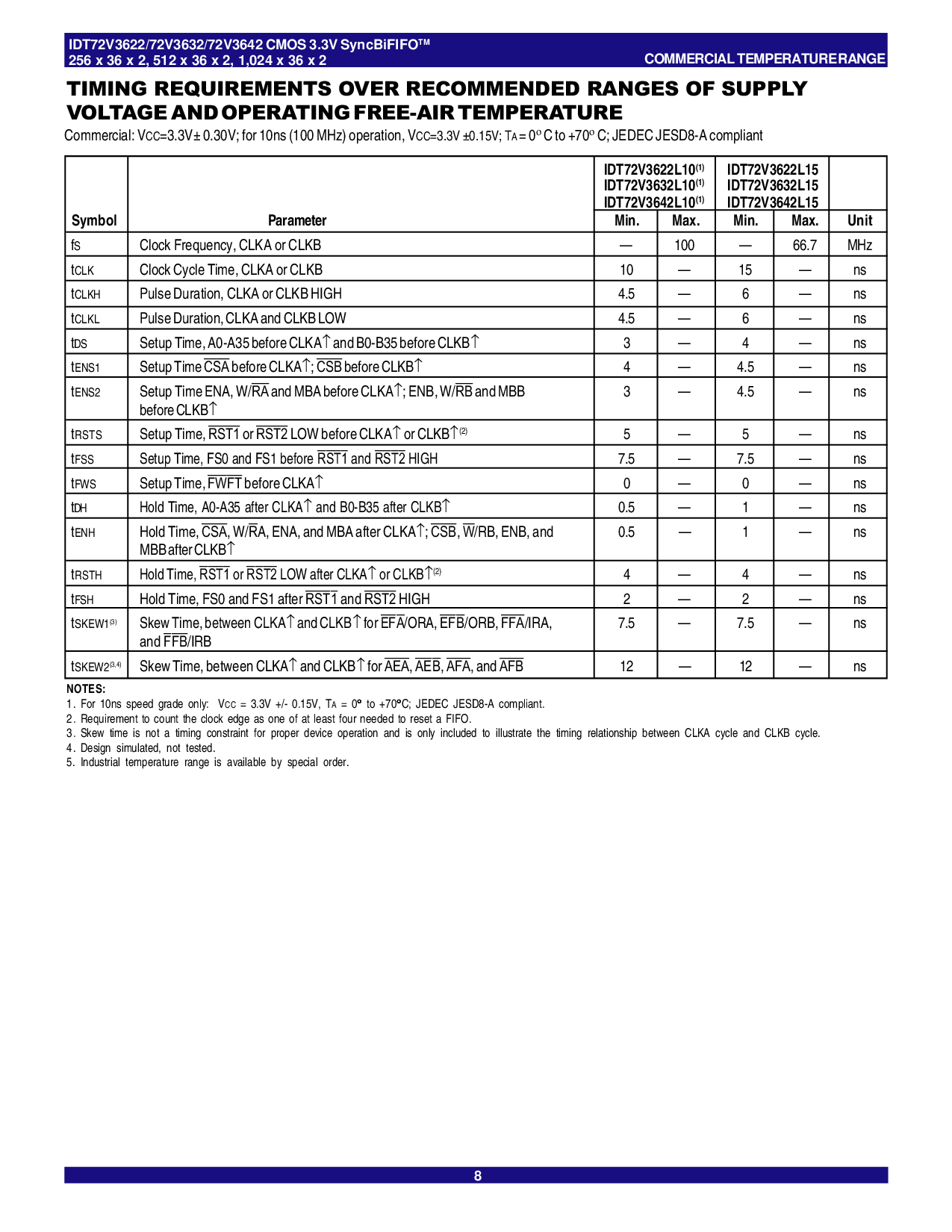

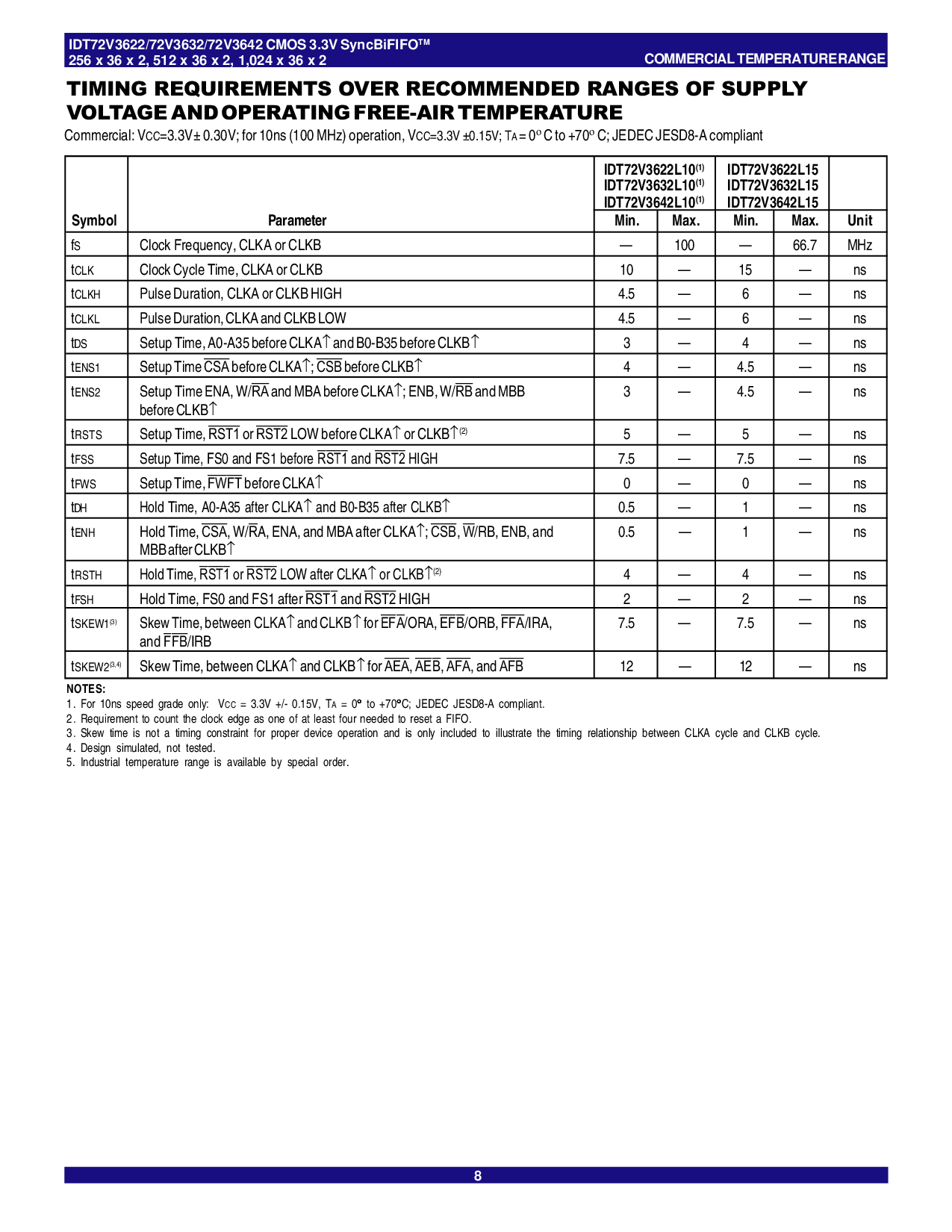

idt72v3622/72v3632/72v3642 cmos 3.3v syncbififo

TM

256 x 36 x 2, 512 x 36 x 2, 1,024 x 36 x 2

商业的 温度 范围

IDT72V3622L10

(1)

IDT72V3622L15

IDT72V3632L10

(1)

IDT72V3632L15

IDT72V3642L10

(1)

IDT72V3642L15

标识 参数 最小值 最大值 最小值 最大值 单位

f

S

时钟 频率, clka 或者 clkb — 100 — 66.7 MHz

t

CLK

时钟 循环 时间, clka 或者 clkb 10 — 15 — ns

t

CLKH

脉冲波 持续时间, clka 或者 clkb 高 4.5 — 6 — ns

t

CLKL

脉冲波 持续时间, clka 和 clkb 低 4.5 — 6 — ns

t

DS

建制 时间, a0-a35 在之前 clka

↑

和 b0-b35 在之前 clkb

↑

3— 4—ns

t

ENS1

建制 时间

CSA

在之前 clka

↑

;

CSB

在之前 clkb

↑

4 — 4.5 — ns

t

ENS2

建制 时间 ena, w/

RA

和 mba 在之前 clka

↑

; enb, w/

RB

和 mbb 3 — 4.5 — ns

在之前 clkb

↑

t

RSTS

建制 时间,

RST1

或者

RST2

低 在之前 clka

↑

或者 clkb

↑

(2)

5— 5—ns

t

FSS

建制 时间, fs0 和 fs1 在之前

RST1

和

RST2

高

7.5 — 7.5 — ns

t

FWS

建制 时间,

FWFT

在之前 clka

↑

0— 0—ns

t

DH

支撑 时间, a0-a35 之后 clka

↑

和 b0-b35 之后 clkb

↑

0.5 — 1 — ns

t

ENH

支撑 时间,

CSA

, w/

R

一个, ena, 和 mba 之后 clka

↑

;

CSB

,

W

/rb, enb, 和 0.5 — 1 — ns

mbb 之后 clkb

↑

t

RSTH

支撑 时间,

RST1

或者

RST2

低 之后 clka

↑

或者 clkb

↑

(2)

4— 4—ns

t

FSH

支撑 时间, fs0 和 fs1 之后

RST1

和

RST2

高 2 — 2 — ns

t

SKEW1

(3)

skew 时间, 在 clka

↑

和 clkb

↑

为

EFA

/ora,

EFB

/orb,

FFA

/ira, 7.5 — 7.5 — ns

和

FFB

/irb

t

SKEW2

(3,4)

skew 时间, 在 clka

↑

和 clkb

↑

为

AEA

,

AEB

,

AFA

, 和

AFB

12 — 12 — ns

注释:

1.

为 10ns 速 等级 仅有的: v

CC

= 3.3v +/- 0.15v, t

一个

= 0

°°

°°

°

至 +70

°°

°°

°

c; 电子元件工业联合会 jesd8-一个 一致的.

2. 必要条件 至 计数 这 时钟 边缘 作 一个 的 在 least 四 需要 至 重置 一个 先进先出.

3.

skew 时间 是 不 一个 定时 constraint 为 恰当的 设备 运作 和 是 仅有的 包含 至 illustrate 这 定时 relationship 在 clka 循环 和 clkb 循环.

4. 设计 simulated, 不 测试.

5. 工业的 温度 范围 是 有 用 特定的 顺序.

商业的: v

CC

=3.3v± 0.30v; 为 10ns (100 mhz) operation, v

CC

=3.3v ±0.15v; t

一个

= 0

ο

c 至 +70

ο

c; 电子元件工业联合会 jesd8-一个 一致的