virtex-ii 1.5v 地方-可编程序的 门 arrays

R

ds031-1 (v1.7) october 2, 2001

www.xilinx.com

单元 1 的 4

进步 产品 规格

1-800-255-7778 3

Architecture

virtex-ii 排列 overview

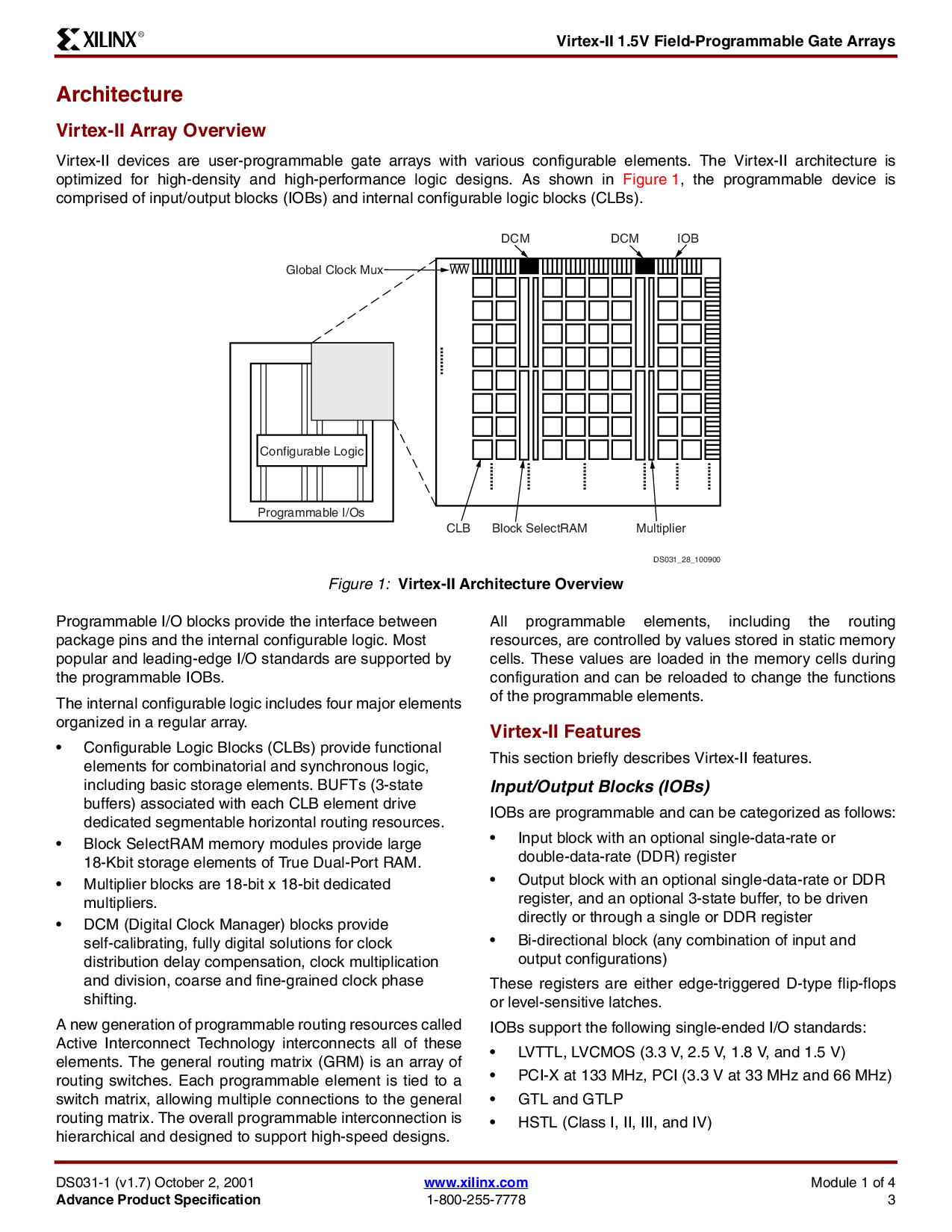

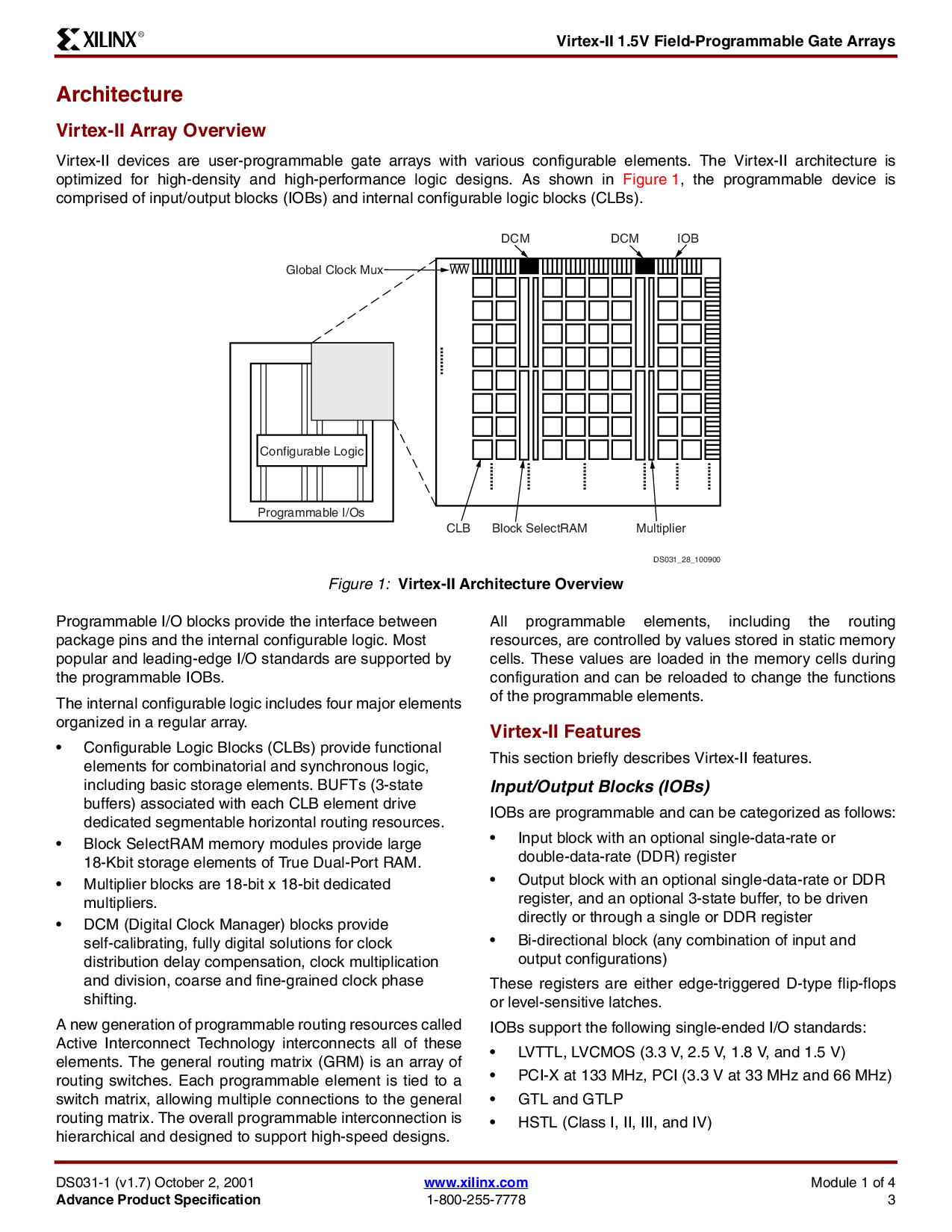

Virtex-ii 设备 是 用户-可编程序的 门 arrays 和 各种各样的 configurable elements. 这 virtex-ii architecture 是

优化 为 高-密度 和 高-效能 逻辑 设计. 作 显示 在图示 1, 这 可编程序的 设备 是

包括 的 输入/输出 blocks (iobs) 和 内部的 configurable 逻辑 blocks (clbs).

可编程序的 i/o blocks 提供 这 接口 在

包装 管脚 和 这 内部的 configurable 逻辑. 大多数

popular 和 leading-边缘 i/o standards 是 supported 用

这 可编程序的 iobs.

这 内部的 configurable 逻辑 包含 四 主要的 elements

有组织的 在 一个 regular 排列.

•

configurable 逻辑 blocks (clbs) 提供 函数的

elements 为 combinatorial 和 同步的 逻辑,

包含 基本 存储 elements. bufts (3-状态

缓存区) 有关联的 和 各自 clb 元素 驱动

专心致志的 segmentable horizontal routing resources.

•

块 selectram 记忆 modules 提供 大

18-kbit 存储 elements 的 真实 双-端口 内存.

•

乘法器 blocks 是 18-位 x 18-位 专心致志的

multipliers.

•

dcm (数字的 时钟 manager) blocks 提供

自-标定, 全部地 数字的 解决方案 为 时钟

分发 延迟 补偿, 时钟 multiplication

和 分隔, coarse 和 fine-grained 时钟 阶段

shifting.

一个 新 一代 的 可编程序的 routing resources called

起作用的 interconnect 技术 interconnects 所有 的 这些

elements. 这 一般 routing 矩阵变换 (grm) 是 一个 排列 的

routing switches. 各自 可编程序的 元素 是 系 至 一个

转变 矩阵变换, 准许 多样的 连接 至 这 一般

routing 矩阵变换. 这 整体的 可编程序的 interconnection 是

hierarchical 和 设计 至 支持 高-速 设计.

所有 可编程序的 elements, 包含 这 routing

resources, 是 控制 用 值 贮存 在 静态的 记忆

cells. 这些 值 是 承载 在 这 记忆 cells 在

配置 和 能 是 reloaded 至 改变 这 功能

的 这 可编程序的 elements.

virtex-ii 特性

这个 部分 briefly describes virtex-ii 特性.

输入/输出 blocks (iobs)

iobs 是 可编程序的 和 能 是 分类 作 跟随:

•

输入 块 和 一个 optional 单独的-数据-比率 或者

翻倍-数据-比率 (ddr) 寄存器

•

输出 块 和 一个 optional 单独的-数据-比率 或者 ddr

寄存器, 和 一个 optional 3-状态 缓存区, 至 是 驱动

直接地 或者 通过 一个 单独的 或者 ddr 寄存器

•

bi-directional 块 (任何 结合体 的 输入 和

输出 配置)

这些 寄存器 是 也 边缘-triggered d-类型 flip-flops

或者 水平的-敏感的 latches.

iobs 支持 这 下列的 单独的-结束 i/o standards:

•

lvttl, lvcmos (3.3 v, 2.5 v, 1.8 v, 和 1.5 v)

•

pci-x 在 133 mhz, pci (3.3 v 在 33 mhz 和 66 mhz)

•

gtl 和 gtlp

•

hstl (类 i, ii, iii, 和 iv)

图示 1:

virtex-ii

architecture overview

global 时钟 mux

DCM DCM IOB

CLB

可编程序的 i/os

块 selectram 乘法器

configurable 逻辑

ds031_28_100900