7

fn9091.5

january 4, 2005

应用 信息

故障 模式 在 repetitive startups

在 一个 低 vcc (<2v), 这 thevenin 相等的 的 这 20k

分隔物 在 这 pwm 管脚, 作 显示 在 这 块 图解 在

页 2, 是 非 变长 真实; 非常 高 阻抗 将 是 seen

从 这 pwm 管脚 至 地. 接合面 泄漏 电流 从

这 vcc 至 这 电阻 tub 将 tend 至 拉 向上 这 pwm 输入

和 falsely 触发 这 ugate. 如果 这 活力 贮存 在 这

自举 电容 是 不 完全地 释放 在 这

previous 电源-向下 时期,然后 这 upper 场效应晶体管 可以

是 转变 在 和 发生 一个 尖刺 在 这 输出 当 vcc

ramps 向上. 一个 499k

Ω

电阻 在 这 pwm 至 地, 作 显示 在

图示 3, helps bleed 这 泄漏 电流, 因此 eliminating

这 startup 尖刺.

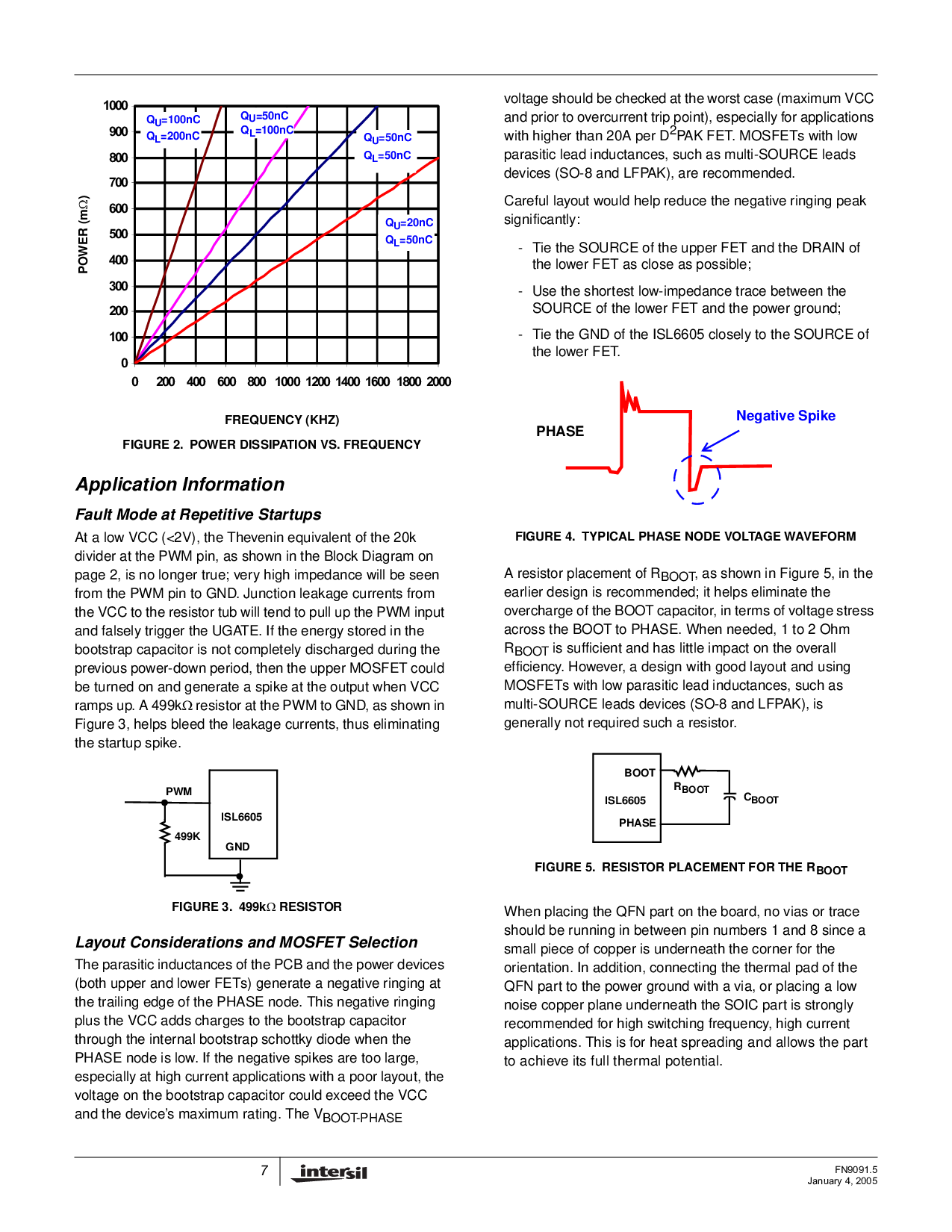

布局 仔细考虑 和 场效应晶体管 选择

这 parasitic inductances 的这 pcb 和 这 电源 设备

(两个都 upper 和 更小的 fets) generate 一个 负的 ringing 在

这 trailing 边缘 的 这 阶段 node. 这个 负的 ringing

加 这 vcc adds charges 至 这 自举 电容

通过 这 内部的 自举 肖特基 二极管 当 这

阶段 node 是 低. 如果 这 负的 尖刺 是 too 大,

特别 在 高 电流 产品 和 一个 poor 布局, 这

电压 在 这 自举 电容 可以 超过 这 vcc

和 这 设备的 最大 比率. 这 v

激励-阶段

电压 应当 是 审查 在 这 worst 情况 (最大 vcc

和 较早的 至 overcurrent trip 要点), 特别 为 产品

和 高等级的 比 20a 每 d

2

pak 场效应晶体管. mosfets 和 低

parasitic 含铅的 inductances, 此类 作 multi-源 leads

设备 (所以-8 和 lfpak), 是 推荐.

细致的 布局 将 帮助 减少 这 负的 ringing 顶峰

significantly:

- 系 这 源 的 这 upper 场效应晶体管 和 这 流 的

这 更小的 场效应晶体管 作 关闭 作 可能;

- 使用 这 shortest 低-阻抗 查出 在 这

源 的 这 更小的 场效应晶体管 和 这 电源 地面;

- 系 这 地 的 这 isl6605 closely 至 这 源 的

这 更小的 场效应晶体管.

一个 电阻 placement 的 r

激励

, 作 显示 在 图示 5, 在 这

早期 设计 是 推荐; 它 helps eliminate 这

overcharge 的 这 激励 capacitor, 在 条款 的 电压 压力

横过 这 激励 至 阶段.当 需要ed, 1 至 2 ohm

R

激励

是 sufficient 和 有 little impact 在 这 整体的

效率. 不管怎样, 一个 设计 和 好的 布局 和 使用

mosfets 和 低 parasitic 含铅的 inductances, 此类 作

multi-源 leads 设备 (所以-8 和 lfpak), 是

一般地 不 必需的 此类 一个 电阻.

当 放置 这 qfn 部分 在 这 板, 非 vias 或者 查出

应当 是 运动 在 在 管脚 号码 1 和 8 自从 一个

小 片 的 铜 是 underneath 这 corner 为 这

方向. 在 增加, 连接 这 热的 垫子 的 这

qfn 部分 至 这 电源 地面 和 一个 通过, 或者 放置 一个 低

噪音 铜 平面 underneath 这 soic 部分 是 strongly

推荐 为 高 切换 频率, 高 电流

产品. 这个 是 为 热温 spreading 和 准许 这 部分

至 达到 它的 全部 热的 潜在的.

0

100

200

300

400

500

600

700

800

900

1000

0 200 400 600 800 1000 1200 1400 1600 1800 2000

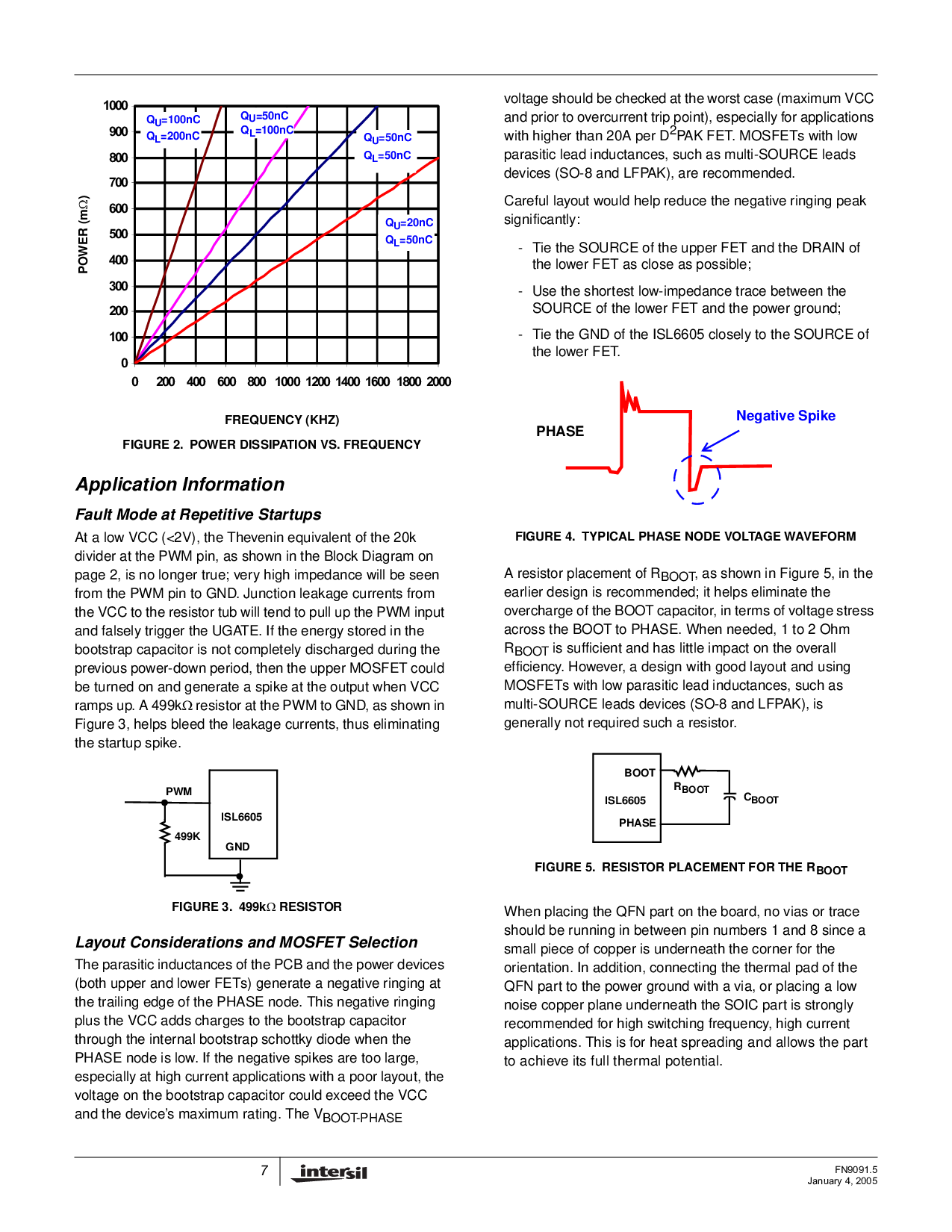

频率 (khz)

0

100

200

300

400

500

600

700

800

900

1000

0 200 400 600 800 1000 1200 1400 1600 1800 2000

Q

U

=50nC

Q

L

=50nC

Q

U

=50nC

Q

L

=100nC

Q

U

=100nC

Q

L

=200nC

Q

U

=20nC

Q

L

=50nC

电源 (m

Ω

)

图示 2. 电源 消耗 vs. 频率

PWM

ISL6605

499K

地

图示 3. 499k

Ω

电阻

阶段

负的 尖刺

图示 4. 典型 阶段 node 电压 波形

ISL6605

激励

阶段

C

激励

R

激励

图示 5. 电阻 placement 为 这 r

激励