rev. 0

AD1958

–6–

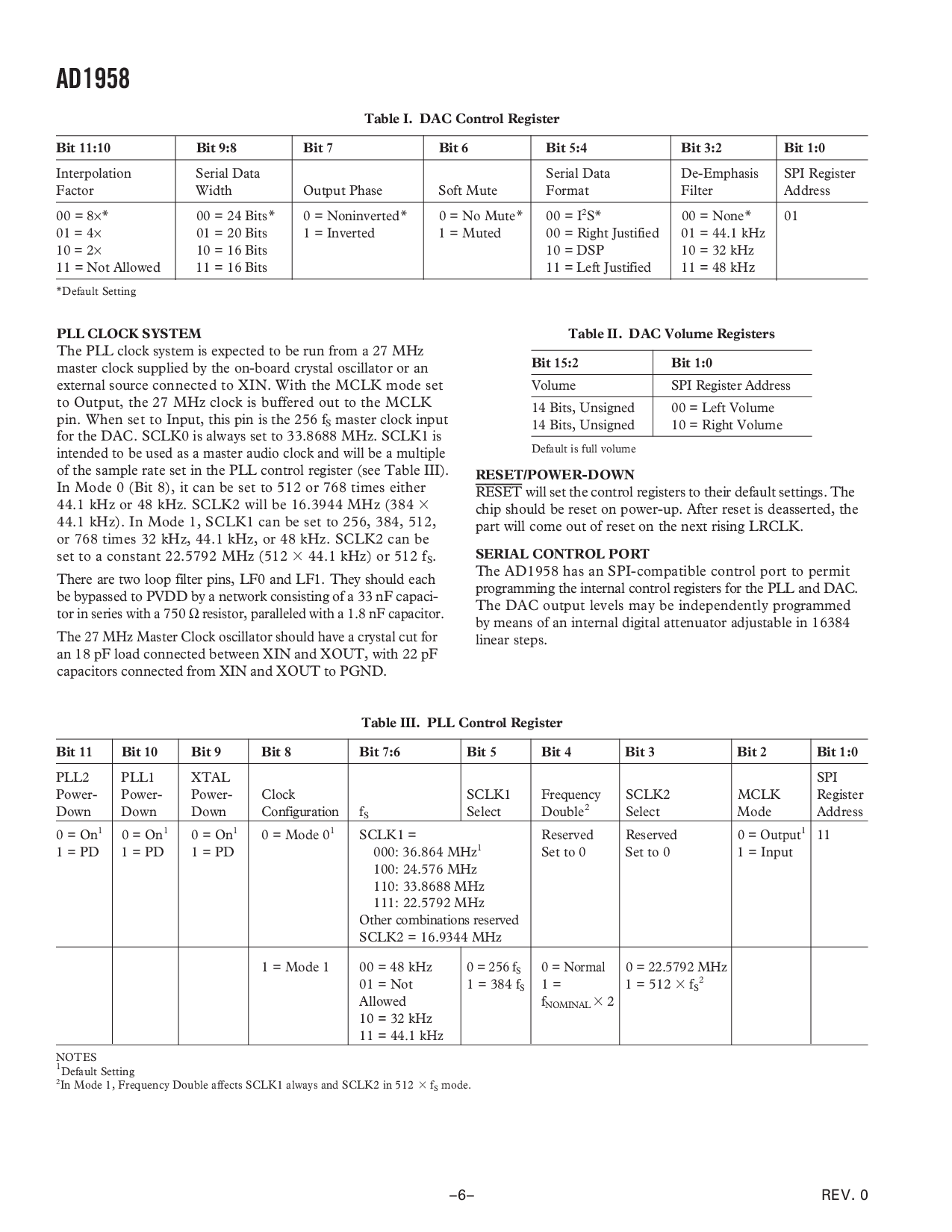

表格 i. dac 控制 寄存器

位 11:10 位 9:8 位 7 位 6 位 5:4 位 3:2 位 1:0

Interpolation 串行 数据 串行 数据 de-emphasis spi 寄存器

因素 宽度 输出 阶段 软 沉默的 Format 过滤 地址

00 = 8

×

*

00 = 24 位

*

0 = noninverted

*

0 = 非 沉默的

*

00 = i

2

S

*

00 = 毫无

*

01

01 = 4

×

01 = 20 位 1 = inverted 1 = muted 00 = 正确的 justified 01 = 44.1 khz

10 = 2

×

10 = 16 位 10 = dsp 10 = 32 khz

11 = 不 允许 11 = 16 位 11 = left justified 11 = 48 kh

z

*

default 设置

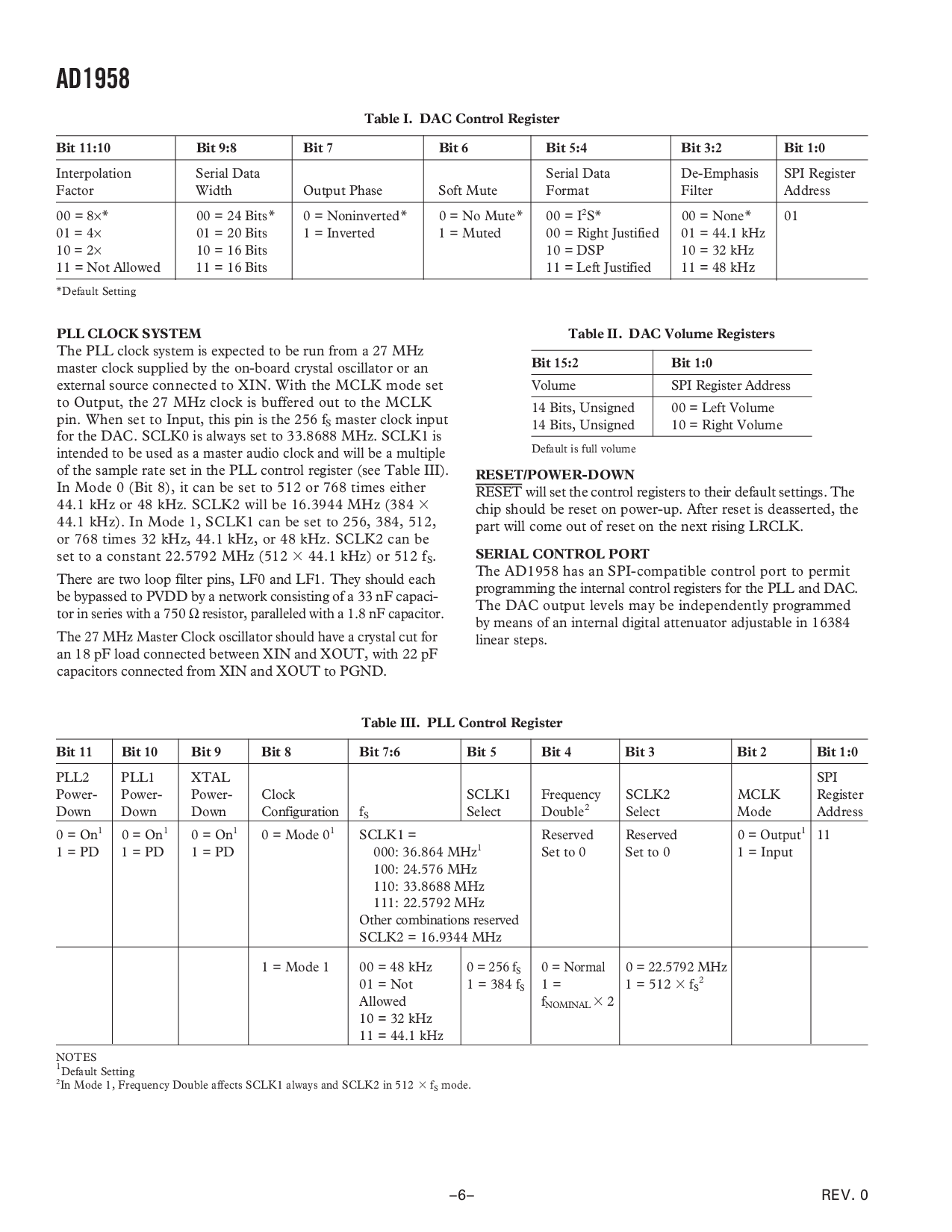

表格 iii. pll 控制 寄存器

位 11 位 10 位 9 位 8 位 7:6 位 5 位 4 位 3 位 2 位 1:0

PLL2 PLL1 XTAL SPI

电源- 电源- 电源- 时钟 SCLK1 频率 SCLK2 MCLK 寄存器

向下 向下 向下 配置 f

S

选择 翻倍

2

选择 模式 地址

0 = 在

1

0 = 在

1

0 = 在

1

0 = 模式 0

1

sclk1 = 保留 保留

0 = 输出

1

11

1 = pd 1 = pd 1 = pd 000: 36.864 mhz

1

设置 至 0 设置 至 0 1 = 输入

100: 24.576 mhz

110: 33.8688 mhz

111: 22.5792 mhz

其它 结合体 保留

sclk2 = 16.9344 mhz

1 = 模式 1 00 = 48 khz

0 = 256 f

S

0 = 正常的

0 = 22.5792 mhz

01 = 不 1 = 384

f

S

1 = 1 = 512

f

S

2

允许 f

名义上的

2

10 = 32 khz

11 = 44.1 khz

注释

1

default 设置

2

在 模式 1, 频率 翻倍 affects sclk1 总是 和 sclk2 在 512

f

S

模式.

pll 时钟 系统

这 pll 时钟 系统 是 预期的 至 是 run 从 一个 27 mhz

主控 时钟 有提供的 用 这 在-板 结晶 振荡器 或者 一个

外部 源 connected 至 xin. 和 这 mclk 模式 设置

至 输出, 这 27 mhz 时钟 是 缓冲 输出 至 这 mclk

管脚. 当 设置 至 在放, 这个 管脚 是 这 256 f

S

主控 时钟 输入

为 这 dac. sclk0 是 总是 设置 至 33.8688 mhz. sclk1 是

将 至 是 使用 作 一个 主控 音频的 时钟 和 将 是 一个 多样的

的 这 样本 比率 设置 在 这 pll 控制 寄存器 (看 表格 iii).

在 模式 0 (位 8), 它 能 是 设置 至 512 或者 768 时间 也

44.1 khz 或者 48 khz. sclk2 将 是 16.3944 mhz (384

44.1 khz). 在 模式 1, sclk1 能 是 设置 至 256, 384, 512,

或者 768 时间 32 khz, 44.1 khz, 或者 48 khz. sclk2 能 是

设置 至 一个 常量 22.5792 mhz (512

44.1 khz) 或者 512 f

S

.

那里 是 二 循环 过滤 管脚, lf0 和 lf1. 它们 应当 各自

是 绕过 至 pvdd 用 一个 网络 consisting 的 一个 33 nf capaci-

tor

在 序列 和 一个 750

Ω

电阻, paralleled 和 一个 1.8 nf 电容.

这 27 mhz 主控 时钟 振荡器 应当 有 一个 结晶 截 为

一个 18 pf 加载 连接 在 xin 和 xout, 和 22 pf

电容 连接 从 xin 和 xout 至 pgnd.

表格 ii. dac 容积 寄存器

位 15:2 位 1:0

容积 spi 寄存器 地址

14 位, unsigned 00 = left 容积

14 位, unsigned 10 = 正确的 容积

default 是 全部 容积

重置/电源-向下

重置

将 设置 这 控制 寄存器 至 它们的 default settings. 这

碎片 应当 是 重置 在 电源-向上. 之后 重置 是 deasserted, 这

部分 将 来到 输出 的 重置 在 这 next rising lrclk.

串行 控制 端口

这 ad1958 有 一个 spi-兼容 控制 端口 至 准许

程序编制 这 内部的 控制 寄存器 为 这 pll 和 dac.

这 dac 输出 水平 将 是 independently programmed

用 意思 的 一个 内部的 数字的 attenuator 可调整的 在 16384

直线的 步伐.