–4–

adsp-21061/adsp-21061l

rev. b

adsp-21000 家族 核心 architecture

这 adsp-21061 包含 这 下列的 architectural 特性

的 这 adsp-21000 家族 核心. 这 adsp-21061 是 代号 和

函数 兼容 和 这 adsp-21060/adsp-21062 和

这 adsp-21020.

独立, 并行的 computation 单位

这 arithmetic/逻辑 单位 (alu), 乘法器 和 shifter 所有 每-

表格 单独的-循环 说明. 这 三 单位 是 arranged 在

并行的, maximizing computational throughput. 单独的 multi-

函数 说明 execute 并行的 alu 和 乘法器 运算-

erations. 这些 computation 单位 支持 ieee 32-位 单独的-

精确 floating-要点, 扩展 精确 40-位 floating-

要点 和 32-位 fixed-要点 数据 formats.

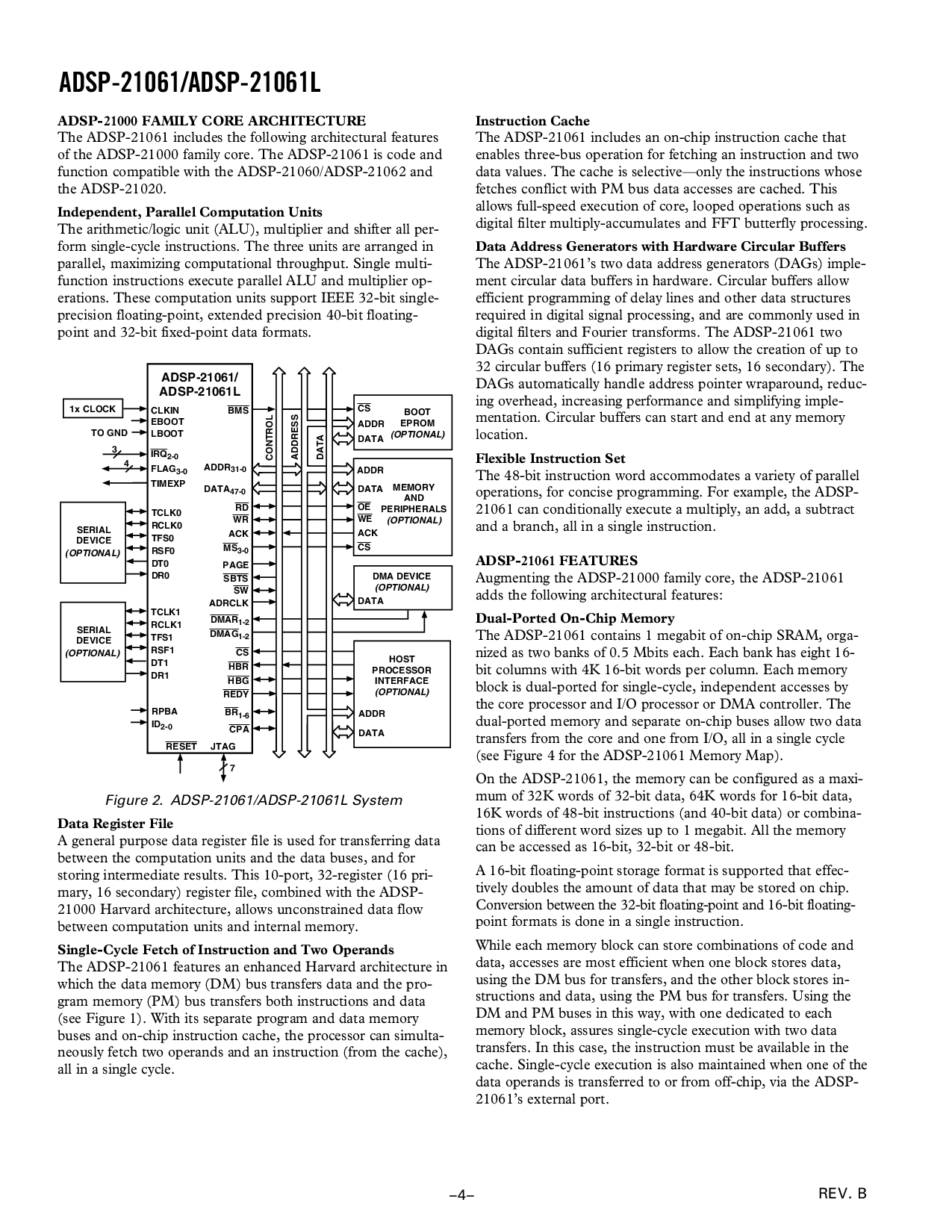

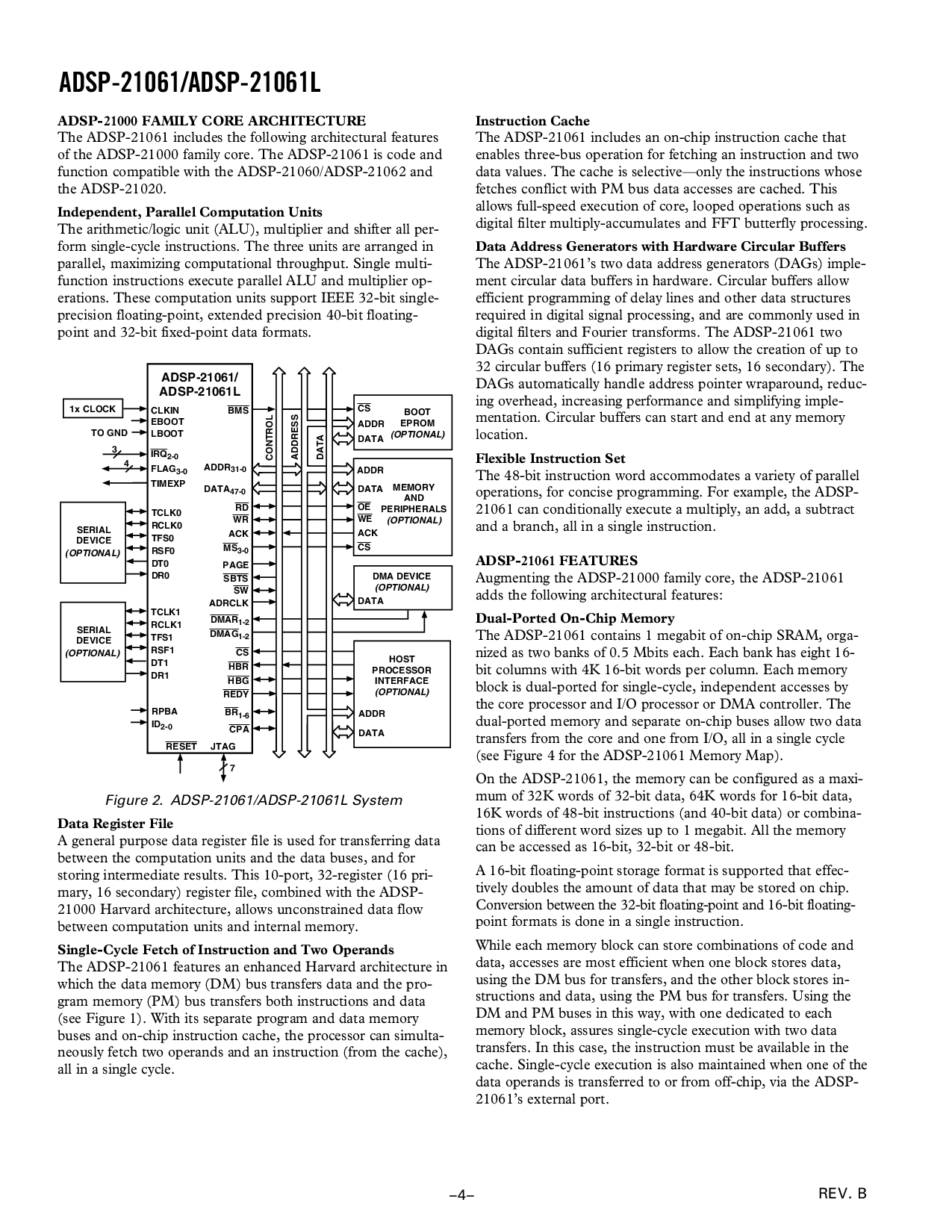

3

4

重置

JTAG

7

adsp-21061/

adsp-21061l

BMS

地址

31-0

数据

47-0

控制

地址

数据

串行

设备

(optional)

串行

设备

(optional)

CS

地址

数据

激励

非易失存储器

(optional)

地址

ACK

CS

记忆

和

PERIPHERALS

(optional)

OE

我们

数据

dma 设备

(optional)

数据

地址

数据

HOST

处理器

接口

(optional)

1x 时钟

CS

HBR

HBG

REDY

RD

WR

页

ADRCLK

ACK

MS

3-0

SBTS

SW

BR

1-6

CPA

DMAR

1-2

DMAG

1-2

CLKIN

EBOOT

LBOOT

IRQ

2-0

标记

3-0

TIMEXP

TCLK0

RCLK0

TFS0

RSF0

DT0

DR0

TCLK1

RCLK1

TFS1

RSF1

DT1

DR1

RPBA

ID

2-0

至 地

图示 2. adsp-21061/adsp-21061l 系统

数据 寄存器 文件

一个 一般 目的 数据 寄存器 文件 是 使用 为 transferring 数据

在 这 computation 单位 和 这 数据 buses, 和 为

storing intermediate 结果. 这个 10-端口, 32-寄存器 (16 pri-

mary, 16 secondary) 寄存器 文件, 联合的 和 这 adsp-

21000 harvard architecture, 准许 unconstrained 数据 流动

在 computation 单位 和 内部的 记忆.

单独的-循环 fetch 的 操作指南 和 二 operands

这 adsp-21061 特性 一个 增强 harvard architecture 在

这个 这 数据 记忆 (dm) 总线 transfers 数据 和 这 pro-

gram 记忆 (pm) 总线 transfers 两个都 说明 和 数据

(看 图示 1). 和 它的 独立的 程序 和 数据 记忆

buses 和 在-碎片 操作指南 cache, 这 处理器 能 simulta-

neously fetch 二 operands 和 一个 操作指南 (从 这 cache),

所有 在 一个 单独的 循环.

操作指南 cache

这 adsp-21061 包含 一个 在-碎片 操作指南 cache 那

使能 三-总线 运作 为 fetching 一个 操作指南 和 二

数据 值. 这 cache 是 selective—only 这 说明 谁的

fetches conflict 和 pm 总线 数据 accesses 是 cached. 这个

准许 全部-速 执行 的 核心, looped 行动 此类 作

数字的 过滤 乘以-accumulates 和 fft butterfly 处理.

数据 地址 发生器 和 硬件 圆形的 缓存区

这 adsp-21061’s 二 数据 地址 发生器 (dags) imple-

ment 圆形的 数据 缓存区 在 硬件. 圆形的 缓存区 准许

效率高的 程序编制 的 延迟 线条 和 其它 数据 结构

必需的 在 数字的 信号 处理, 和 是 commonly 使用 在

数字的 过滤 和 fourier transforms. 这 adsp-21061 二

dags 包含 sufficient 寄存器 至 准许 这 creation 的 向上 至

32 圆形的 缓存区 (16 primary 寄存器 sets, 16 secondary). 这

dags automatically handle 地址 pointer wraparound, reduc-

ing overhead, 增加 效能 和 simplifying imple-

mentation. 圆形的 缓存区 能 开始 和 终止 在 任何 记忆

location.

有伸缩性的 操作指南 设置

这 48-位 操作指南 文字 accommodates 一个 多样性 的 并行的

行动, 为 concise 程序编制. 为 例子, 这 adsp-

21061 能 conditionally execute 一个 乘以, 一个 增加, 一个 减去

和 一个 branch, 所有 在 一个 单独的 操作指南.

adsp-21061 特性

augmenting 这 adsp-21000 家族 核心, 这 adsp-21061

adds 这 下列的 architectural 特性:

双-ported 在-碎片 记忆

这 adsp-21061 包含 1 megabit 的 在-碎片 sram, orga-

nized 作 二 banks 的 0.5 mbits 各自. 各自 bank 有 第八 16-

位 columns 和 4k 16-位 words 每 column. 各自 记忆

块 是 双-ported 为 单独的-循环, 独立 accesses 用

这 核心 处理器 和 i/o 处理器 或者 dma 控制. 这

双-ported 记忆 和 独立的 在-碎片 buses 准许 二 数据

transfers 从 这 核心 和 一个 从 i/o, 所有 在 一个 单独的 循环

(看 图示 4 为 这 adsp-21061 记忆 编排).

在 这 adsp-21061, 这 记忆 能 是 配置 作 一个 maxi-

mum 的 32k words 的 32-位 数据, 64k words 为 16-位 数据,

16k words 的 48-位 说明 (和 40-位 数据) 或者 combina-

tions 的 不同的 文字 sizes 向上 至 1 megabit. 所有 这 记忆

能 是 accessed 作 16-位, 32-位 或者 48-位.

一个 16-位 floating-要点 存储 format 是 supported 那 effec-

tively doubles 这 数量 的 数据 那 将 是 贮存 在 碎片.

转换 在 这 32-位 floating-要点 和 16-位 floating-

要点 formats 是 完毕 在 一个 单独的 操作指南.

当 各自 记忆 块 能 store 结合体 的 代号 和

数据, accesses 是 大多数 效率高的 当 一个 块 stores 数据,

使用 这 dm 总线 为 transfers, 和 这 其它 块 stores 在-

structions 和 数据, 使用 这 pm 总线 为 transfers. 使用 这

dm 和 pm buses 在 这个 方法, 和 一个 专心致志的 至 各自

记忆 块, assures 单独的-循环 执行 和 二 数据

transfers. 在 这个 情况, 这 操作指南 必须 是 有 在 这

cache. 单独的-循环 执行 是 也 maintained 当 一个 的 这

数据 operands 是 transferred 至 或者 从 止-碎片, 通过 这 adsp-

21061’s 外部 端口.