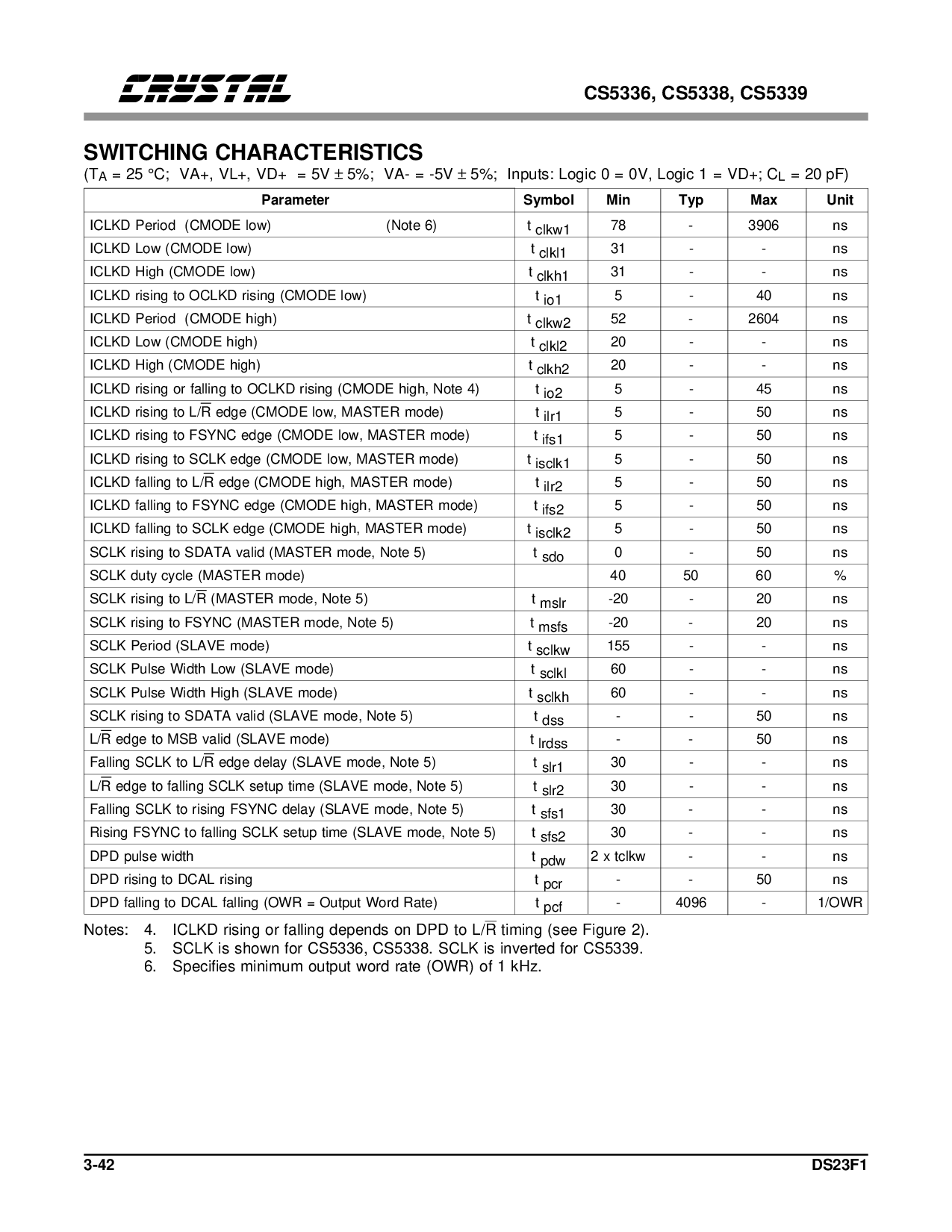

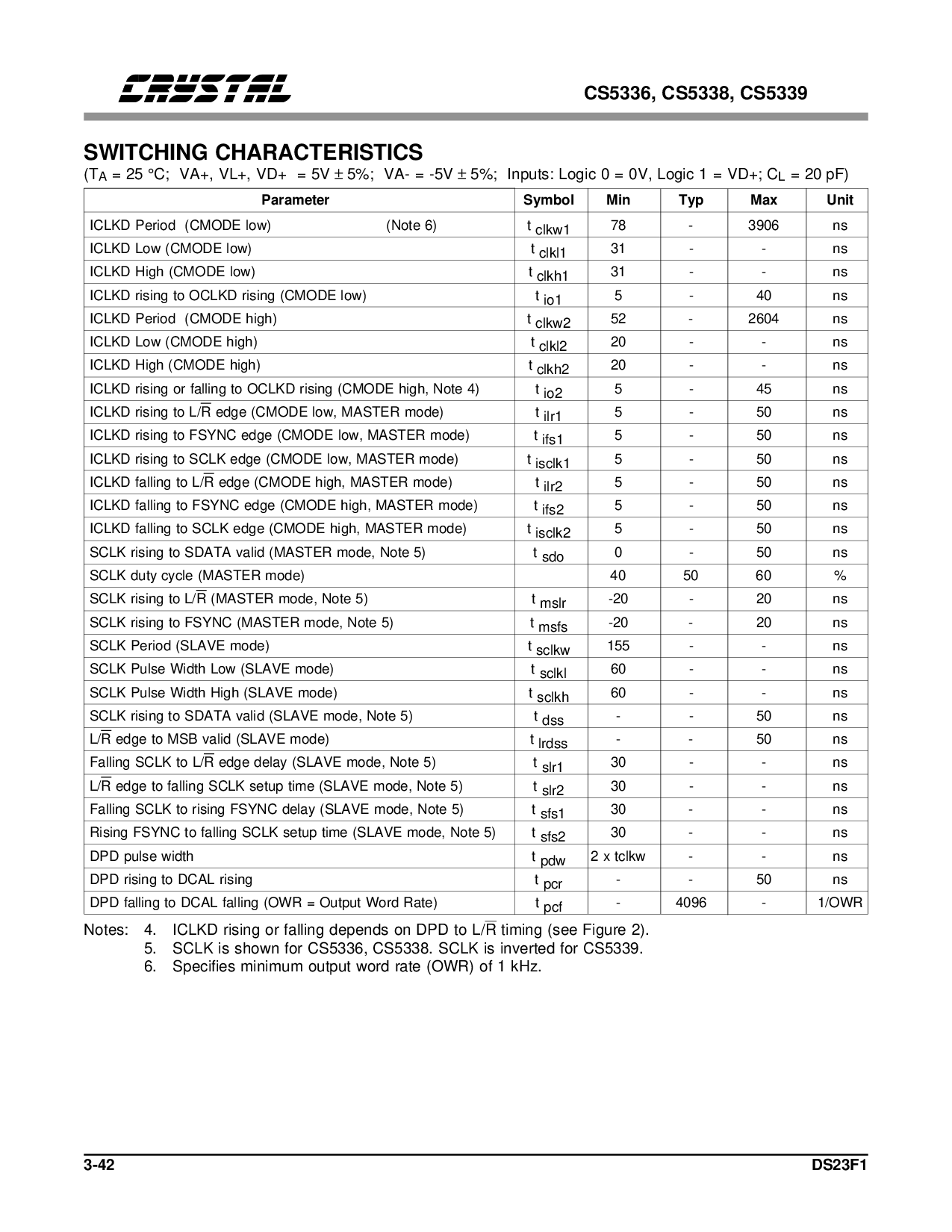

参数 标识 最小值 典型值 最大值 单位

iclkd 时期 (cmode 低) (便条 6) t

clkw1

78 - 3906 ns

iclkd 低 (cmode 低) t

clkl1

31 - - ns

iclkd 高 (cmode 低) t

clkh1

31 - - ns

iclkd rising 至 oclkd rising (cmode 低) t

io1

5 - 40 ns

iclkd 时期 (cmode 高) t

clkw2

52 - 2604 ns

iclkd 低 (cmode 高) t

clkl2

20 - - ns

iclkd 高 (cmode 高) t

clkh2

20 - - ns

iclkd rising 或者 下落 至 oclkd rising (cmode 高, 便条 4) t

io2

5 - 45 ns

iclkd rising 至 l/r 边缘 (cmode 低, 主控 模式) t

ilr1

5 - 50 ns

iclkd rising 至 fsync 边缘 (cmode 低, 主控 模式) t

ifs1

5 - 50 ns

iclkd rising 至 sclk 边缘 (cmode 低, 主控 模式) t

isclk1

5 - 50 ns

iclkd 下落 至 l/r 边缘 (cmode 高, 主控 模式) t

ilr2

5 - 50 ns

iclkd 下落 至 fsync 边缘 (cmode 高, 主控 模式) t

ifs2

5 - 50 ns

iclkd 下落 至 sclk 边缘 (cmode 高, 主控 模式) t

isclk2

5 - 50 ns

sclk rising 至 sdata 有效的 (主控 模式, 便条 5) t

sdo

0 - 50 ns

sclk 职责 循环 (主控 模式) 40 50 60 %

sclk rising 至 l/r (主控 模式, 便条 5) t

mslr

-20 - 20 ns

sclk rising 至 fsync (主控 模式, 便条 5) t

msfs

-20 - 20 ns

sclk 时期 (从动装置 模式) t

sclkw

155 - - ns

sclk 脉冲波 宽度 低 (从动装置 模式) t

sclkl

60 - - ns

sclk 脉冲波 宽度 高 (从动装置 模式) t

sclkh

60 - - ns

sclk rising 至 sdata 有效的 (从动装置 模式, 便条 5) t

dss

- - 50 ns

l/r 边缘 至 msb 有效的 (从动装置 模式) t

lrdss

- - 50 ns

下落 sclk 至 l/r 边缘 延迟 (从动装置 模式, 便条 5) t

slr1

30 - - ns

l/r 边缘 至 下落 sclk 建制 时间 (从动装置 模式, 便条 5) t

slr2

30 - - ns

下落 sclk 至 rising fsync 延迟 (从动装置 模式, 便条 5) t

sfs1

30 - - ns

rising fsync 至 下落 sclk 建制 时间 (从动装置 模式, 便条 5) t

sfs2

30 - - ns

dpd 脉冲波 宽度 t

pdw

2 x tclkw - - ns

dpd rising 至 dcal rising t

pcr

- - 50 ns

dpd 下落 至 dcal 下落 (owr = 输出 文字 比率) t

pcf

-4096-1/owr

切换 特性

(t

一个

= 25

°

c; va+, vl+, vd+ = 5v

±

5%;va- =-5v

±

5%; 输入: 逻辑 0 = 0v, 逻辑 1 = vd+; c

L

= 20 pf)

注释: 4. iclkd rising 或者 下落 取决于 在 dpd 至 l/

r 定时 (看 图示 2).

5. sclk 是 显示 为 cs5336, cs5338. sclk 是 inverted 为 cs5339.

6. specifies 最小 输出 文字 比率 (owr) 的 1 khz.

cs5336, cs5338, cs5339

3-42 DS23F1