8

应用 信息

bypassing 和 pc 板 布局

这 hcpl-0708 optocoupler 是

极其 容易 至 使用. 非

外部 接口 电路系统 是

必需的 因为 这 hcpl-0708

使用 高-速 cmos ic

技术 准许 cmos 逻辑

至 是 连接 直接地 至 这

输入 和 输出.

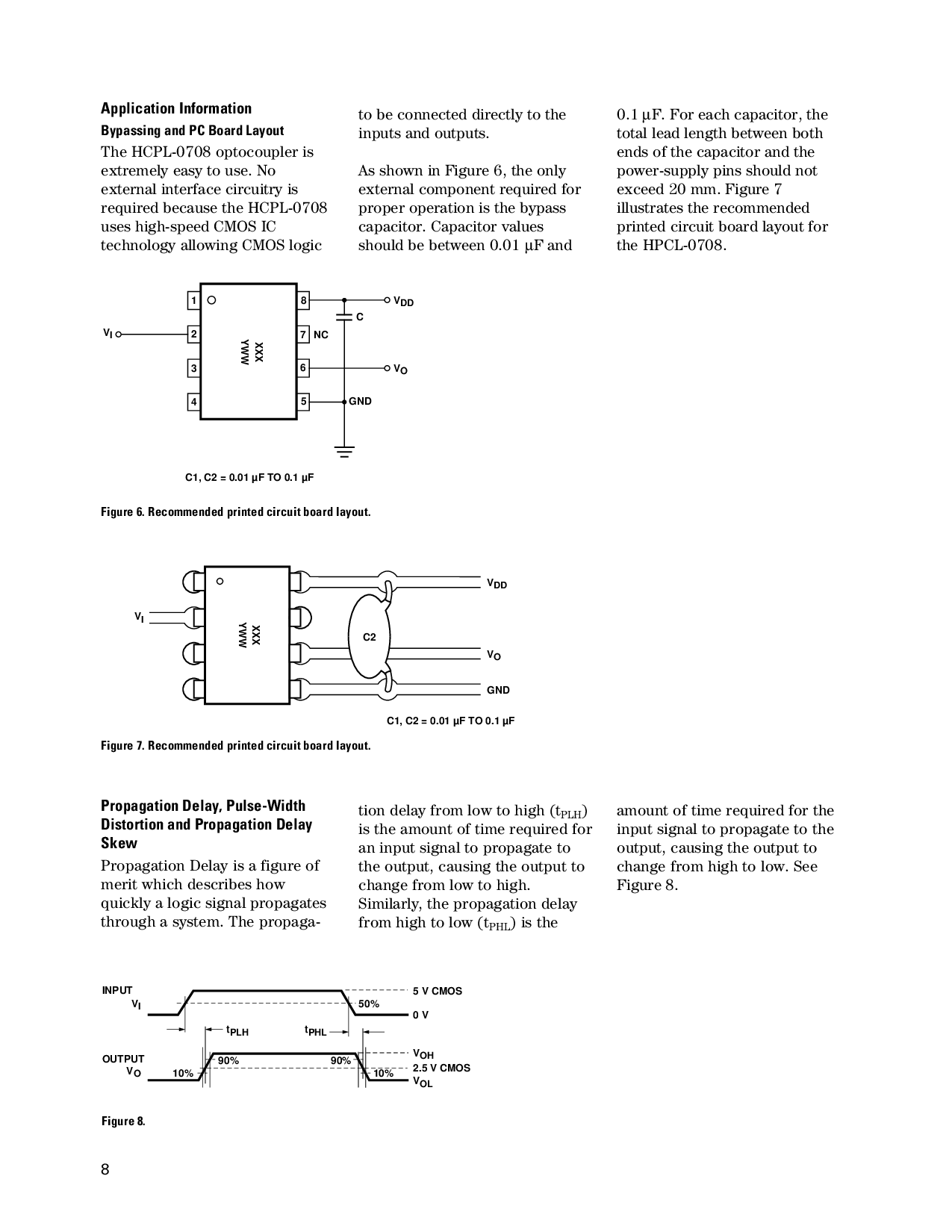

作 显示 在 图示 6, 这 仅有的

外部 组件 必需的 为

恰当的 运作 是 这 绕过

电容. 电容 值

应当 是 在 0.01

µ

f 和

0.1

µ

f. 为 各自 电容, 这

总的 含铅的 长度 在 两个都

ends 的 这 电容 和 这

电源-供应 管脚 应当 不

超过 20 mm. 图示 7

illustrates 这 推荐

打印 电路 板 布局 为

这 hpcl-0708.

图示 6. 推荐 打印 电路 板 布局.

图示 7. 推荐 打印 电路 板 布局.

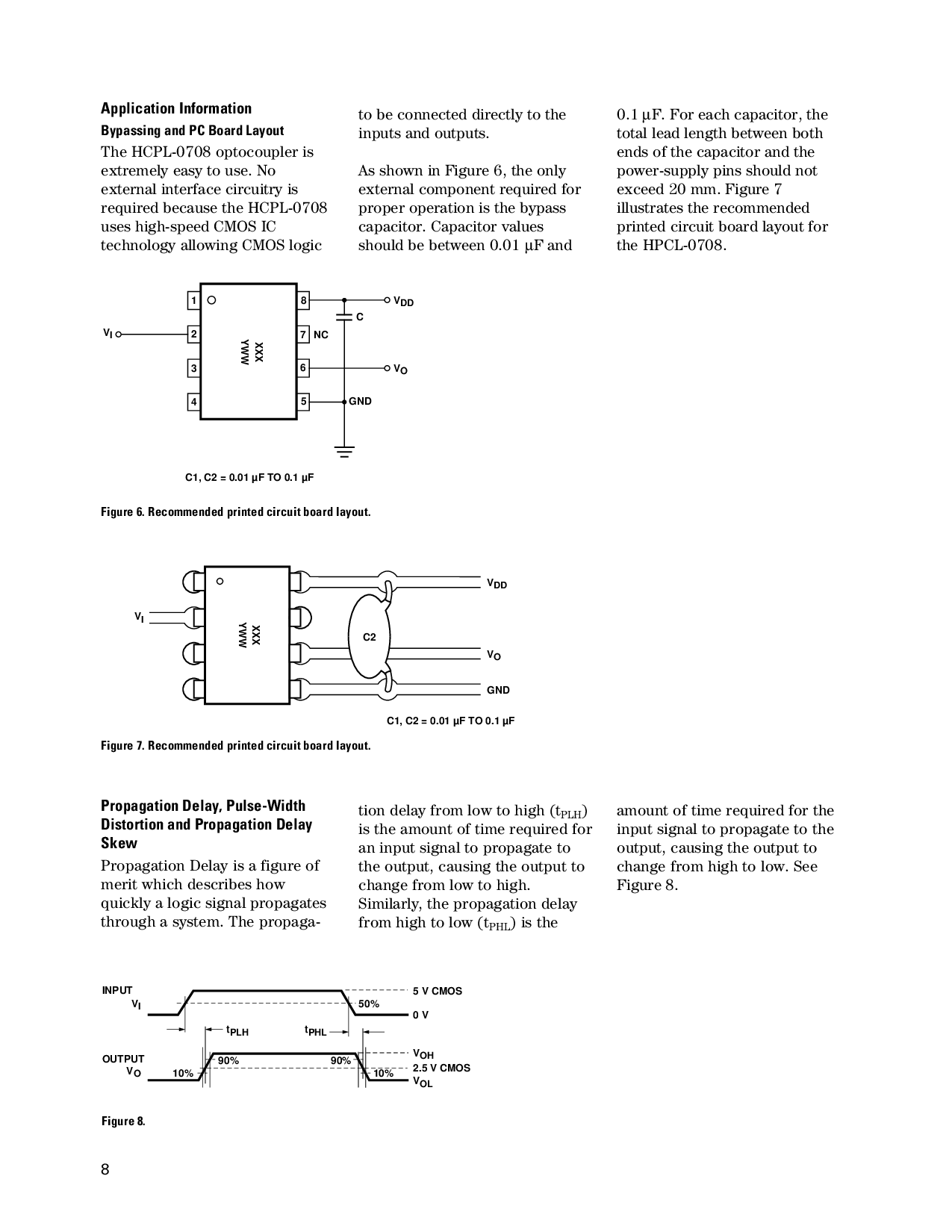

传播 延迟, 脉冲波-宽度

扭曲量 和 传播 延迟

Skew

传播 延迟 是 一个 图示 的

merit 这个 describes 如何

quickly 一个 逻辑 信号 propagates

通过 一个 系统. 这 propaga-

tion 延迟 从 低 至 高 (t

PLH

)

是 这 数量 的 时间 必需的 为

一个 输入 信号 至 propagate 至

这 输出, 造成 这 输出 至

改变 从 低 至 高.

similarly, 这 传播 延迟

从 高 至 低 (t

PHL

) 是 这

数量 的 时间 必需的 为 这

输入 信号 至 propagate 至 这

输出, 造成 这 输出 至

改变 从 高 至 低. 看

图示 8.

图示 8.

输入

t

PLH

t

PHL

输出

V

I

V

O

10%

90%90%

10%

V

OH

V

OL

0 v

50%

5 v cmos

2.5 v cmos

7

5

6

8

2

3

4

1

地

C

NC

V

DD

V

O

V

I

XXX

YWW

c1, c2 = 0.01 µf 至 0.1 µf

V

DD

C2

XXX

YWW

V

O

地

V

I

c1, c2 = 0.01 µf 至 0.1 µf