ics9112-18

零 延迟, 低 skew 缓存区

mds 9112-18 f

2 修订 050400 打印 11/15/00

整体的 电路 系统, inc.• 525 race 街道 • san jose • ca • 95126 • (408)295-9800tel• www.icst.com

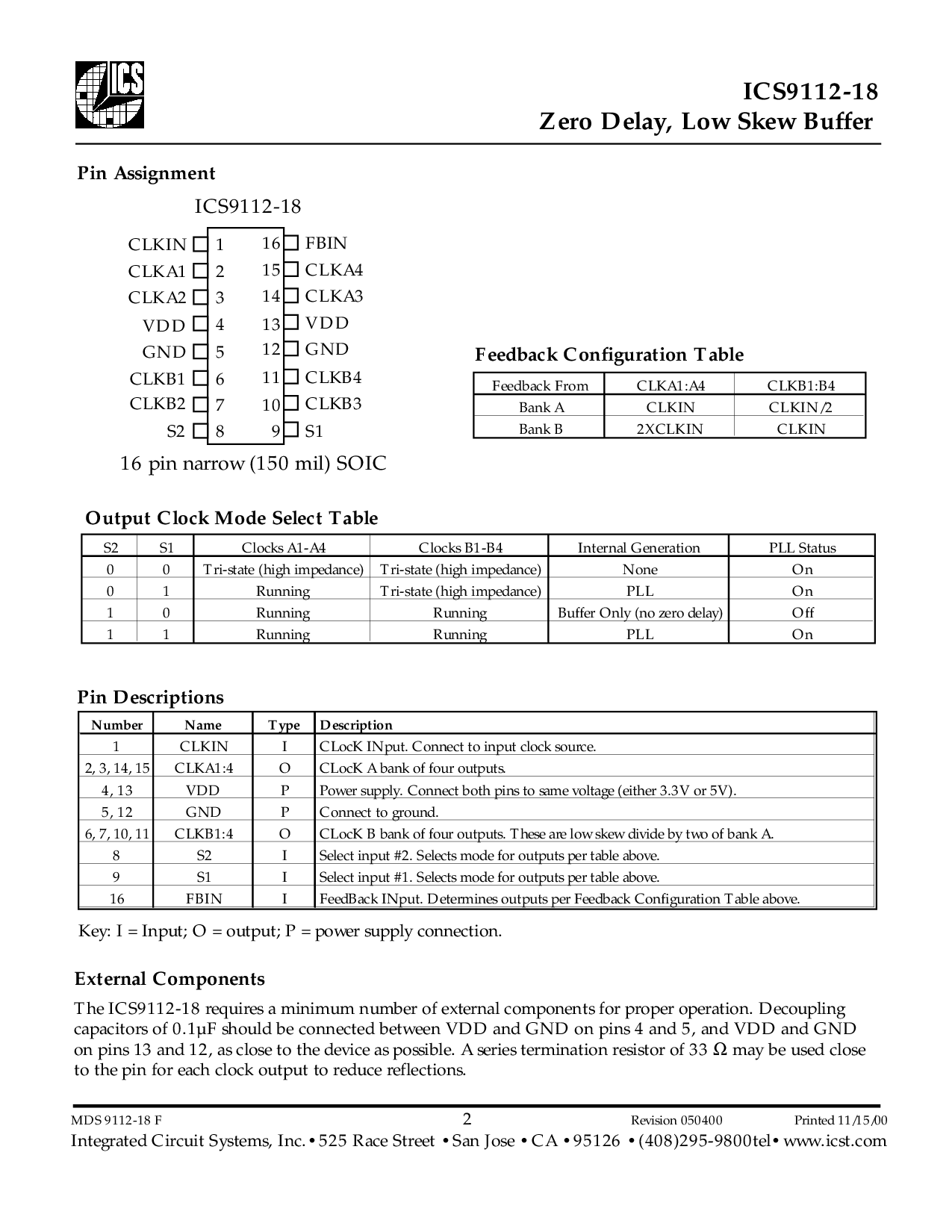

管脚 描述

关键: i = 输入; o = 输出; p = 电源 供应 连接.

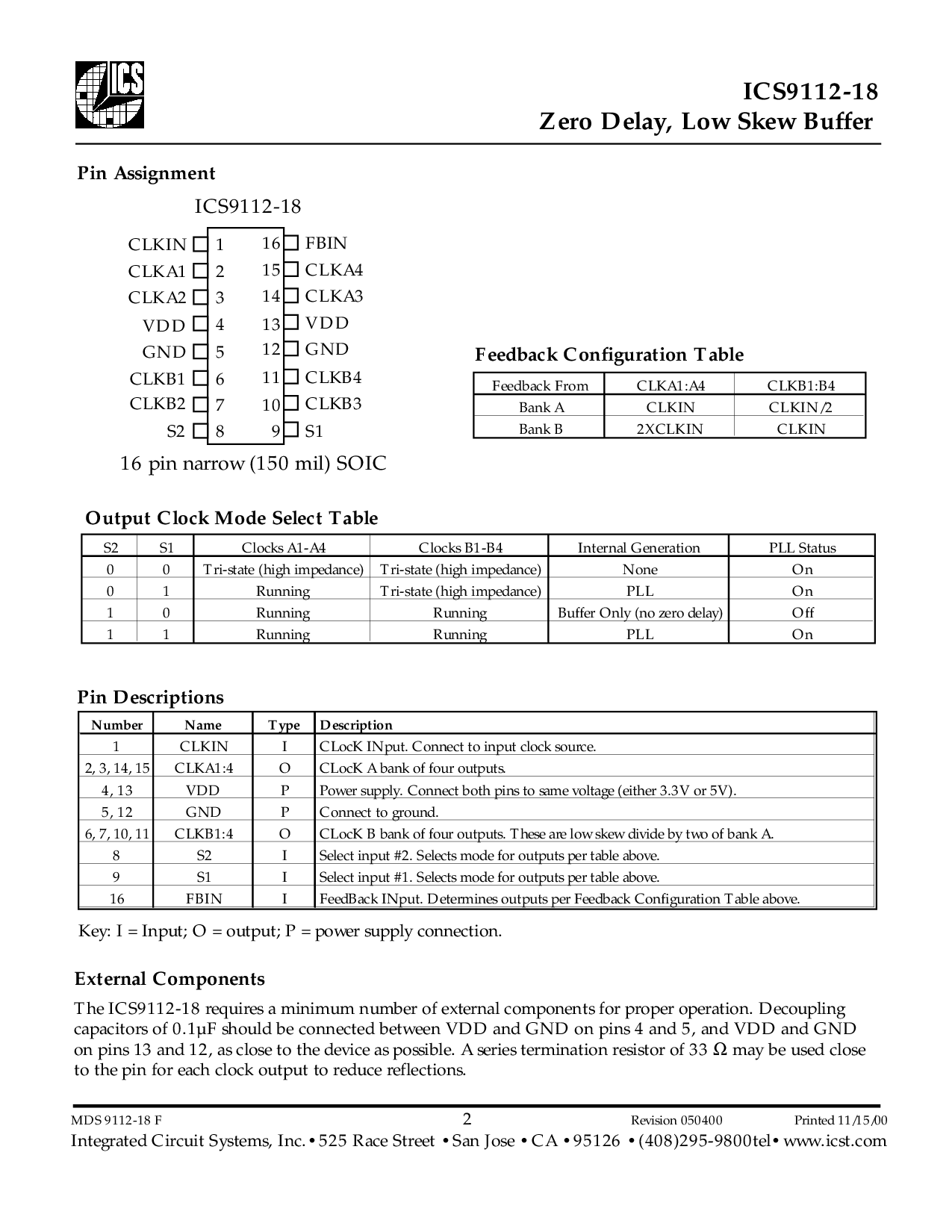

管脚 分派

ics9112-18

外部 组件

这 ics9112-18 需要 一个 最小 号码 的 外部 组件 为 恰当的 运作. 解耦

电容 的 0.1µf 应当 是 连接 在 vdd 和 地 在 管脚 4 和 5, 和 vdd 和 地

在 管脚 13 和 12, 作 关闭 至 这 设备 作 可能. 一个 序列 末端 电阻 的 33

Ω

将 是 使用 关闭

至 这 管脚 为 各自 时钟 输出 至 减少 reflections.

16

15

14

13

16 管脚 narrow (150 mil) soic

12

11

10

9

1

2

3

4

5

6

7

8

CLKA1

地

FBIN

CLKIN

VDD

S2

CLKB1

CLKB2

VDD

地

CLKB3

S1

CLKB4

CLKA4

CLKA3

CLKA2

S2 S1 clocks a1-a4 clocks b1-b4 内部的 一代 pll 状态

0 0 触发-状态 (高 阻抗) 触发-状态 (高 阻抗) 毫无 在

0 1 运动 触发-状态 (高 阻抗) PLL 在

1 0 运动 运动 缓存区 仅有的 (非 零 延迟) 止

1 1 运动 运动 PLL 在

反馈 从 clka1:a4 clkb1:b4

bank 一个 CLKIN clkin/2

bank b 2XCLKIN CLKIN

号码 名字 类型 描述

1 CLKIN I 时钟 输入. 连接 至 输入 时钟 源.

2, 3, 14, 15 clka1:4 O 时钟 一个 bank 的 四 输出.

4, 13 VDD P 电源 供应. 连接 两个都 管脚 至 一样 电压 (也 3.3v 或者 5v).

5, 12 地 P 连接 至 地面.

6, 7, 10, 11 clkb1:4 O 时钟 b bank 的 四 输出. 这些 是 低 skew 分隔 用 二 的 bank 一个.

8 S2 I 选择 输入 #2. 选择 模式 为 输出 每 表格 在之上.

9 S1 I 选择 输入 #1. 选择 模式 为 输出 每 表格 在之上.

16 FBIN I 反馈 输入. 确定 输出 每 反馈 配置 表格 在之上.

输出 时钟 模式 选择 表格

反馈 配置 表格