6.01 9

idt7130sa/la 和 idt7140sa/la

高-速 1k x 8 双-端口 静态的 内存 和 中断 军队 和 商业的 温度 范围

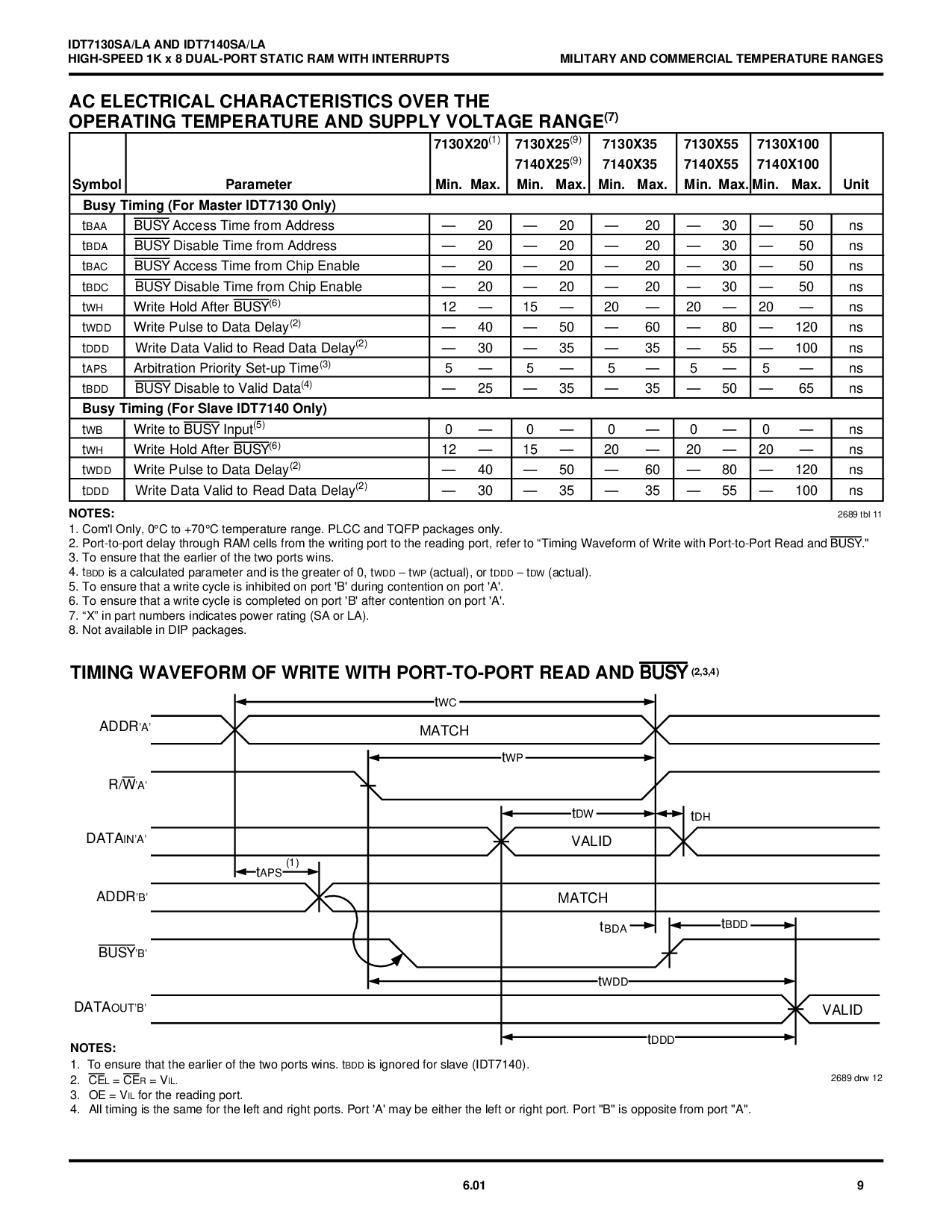

交流 电的 特性 在 这

运行 温度 和 供应 电压 范围

(7)8

M824S258M824S30 7132158M824S4

7130X20

(1)

7130X25

(9)

7130X35 7130X55 7130X100

7140X25

(9)

7140X35 7140X55 7140X100

标识 参数 最小值 最大值 最小值 最大值 最小值 最大值 最小值 最大值 最小值 最大值 单位

busy 定时 (为 主控 ldt7130 仅有的)

t

BAA

BUSY

进入 时间 从 地址 — 20 — 20 — 20 — 30 — 50 ns

t

BDA

BUSY

使不能运转 时间 从 地址 — 20 — 20 — 20 — 30 — 50 ns

t

BAC

BUSY

进入 时间 从 碎片 使能 — 20 — 20 — 20 — 30 — 50 ns

t

BDC

BUSY

使不能运转 时间 从 碎片 使能 — 20 — 20 — 20 — 30 — 50 ns

t

WH

写 支撑 之后

BUSY

(6)

12 — 15 — 20 — 20 — 20 — ns

t

WDD

写 脉冲波 至 数据 延迟

(2)

— 40 — 50 — 60 — 80 — 120 ns

t

DDD

写 数据 有效的 至 读 数据 延迟

(2)

— 30 — 35 — 35 — 55 — 100 ns

t

APS

arbitration priority 设置-向上 时间

(3)

5— 5— 5 — 5—5 — ns

t

BDD

BUSY

使不能运转 至 有效的 数据

(4)

— 25 — 35 — 35 — 50 — 65 ns

busy 定时 (为 从动装置 idt7140 仅有的)

e 5—5—5—5—5

t

WB

写 至

BUSY

输入

(5)

0— 0— 0 — 0—0 — ns

t

WH

写 支撑 之后

BUSY

(6)

12 — 15 — 20 — 20 — 20 — ns

t

WDD

写 脉冲波 至 数据 延迟

(2)

— 40 — 50 — 60 — 80 — 120 ns

t

DDD

写 数据 有效的 至 读 数据 延迟

(2)

— 30 — 35 — 35 — 55 — 100 ns

注释:

2689 tbl 11

1. com'l 仅有的, 0

°

c 至 +70

°

c 温度 范围. plcc 和 tqfp 包装 仅有的.

2. 端口-至-端口 延迟 通过 内存 cells 从 这 writing 端口 至 这 读 端口, 谈及 至 “timing 波形 的 写 和 端口-至-端口 读 和

BUSY

."

3. 至 确保 那 这 早期 的 这 二 端口 wins.

4. t

BDD

是 一个 计算 参数 和 是 这 更好 的 0, t

WDD

– t

WP

(真实的), 或者 t

DDD

– t

DW

(真实的).

5. 至 确保 那 一个 写 循环 是 inhibited 在 端口 'b' 在 contention 在 端口 '一个'.

6. 至 确保 那 一个 写 循环 是 完成 在 端口 'b' 之后 contention 在 端口 '一个'.

7. “x” 在 部分 号码 indicates 电源 比率 (sa 或者 la).

8. 不 有 在 插件 包装.

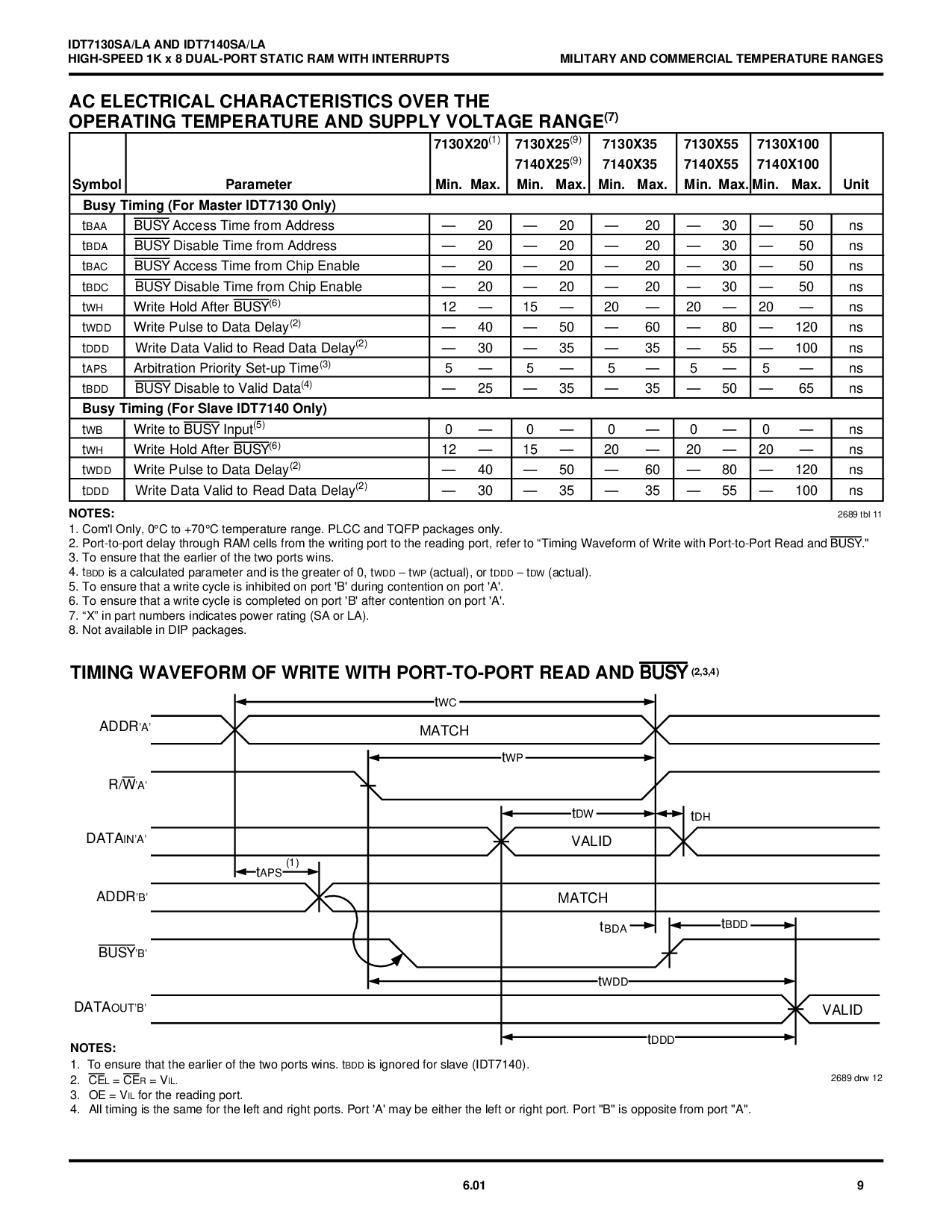

定时 波形 的 写 和 端口-至-端口 读 和

BUSYBUSY

BUSYBUSY

BUSY

t

WC

t

WP

t

DW

t

DH

t

BDD

t

DDD

t

BDA

t

WDD

地址

’B’

数据

OUT’B’

数据

IN’A’

地址

’A’

相一致

有效的

相一致

有效的

r/

W

’A’

BUSY

’B’

t

APS

2689 drw 12

(1)

注释:

1. 至 确保 那 这 早期 的 这 二 端口 wins.

t

BDD

是 ignored 为 从动装置 (idt7140).

2.

CE

L

=

CE

R

= v

il.

3. oe = v

IL

为 这 读 端口.

4. 所有 定时 是 这 一样 为 这 left 和 正确的 端口. 端口 '一个' 将 是 也 这 left 或者 正确的 端口. 端口 "b" 是 opposite 从 端口 "a".

(2,3,4)