6

idt72v801/72v811/72v821/72v831/72v841/72v851 商业的 和 工业的 温度 范围

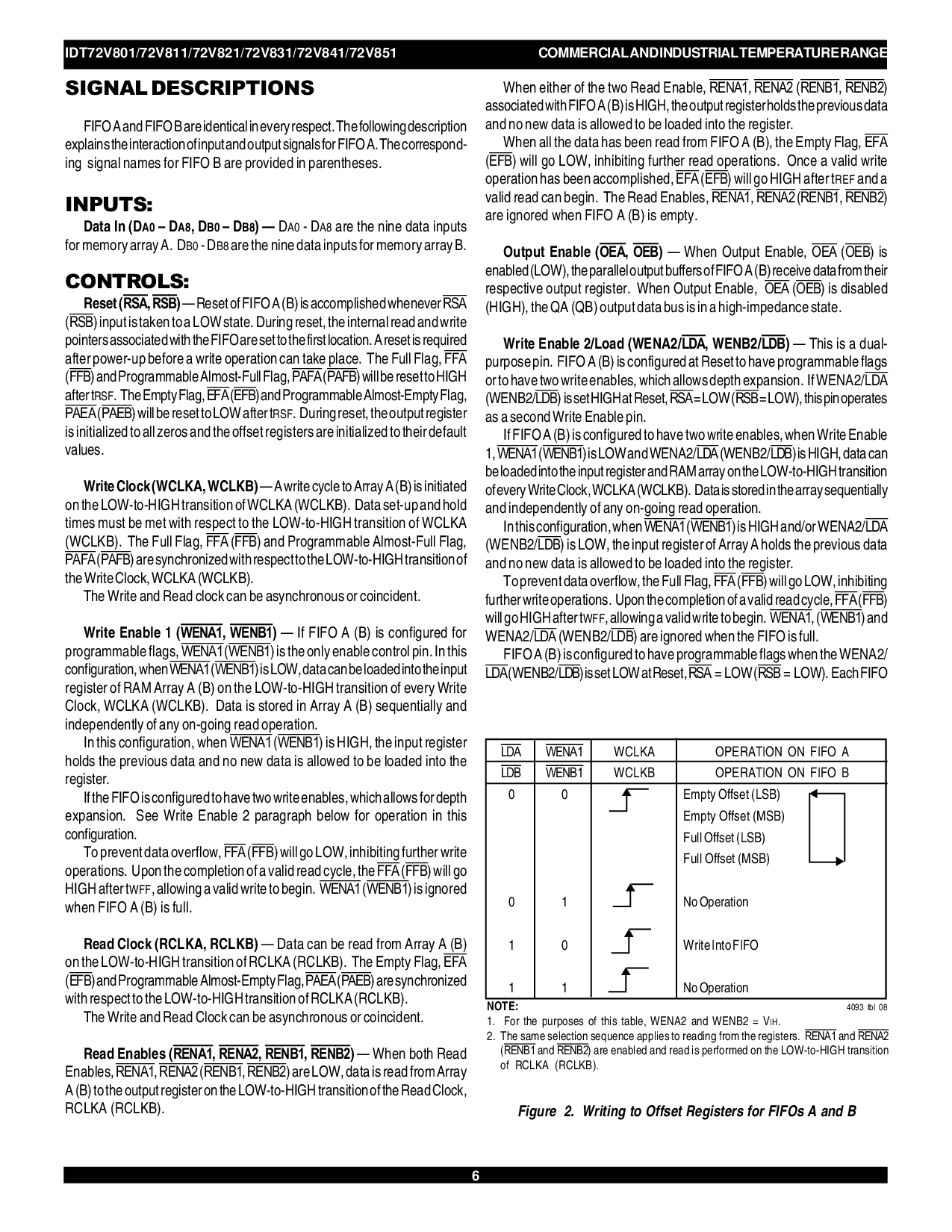

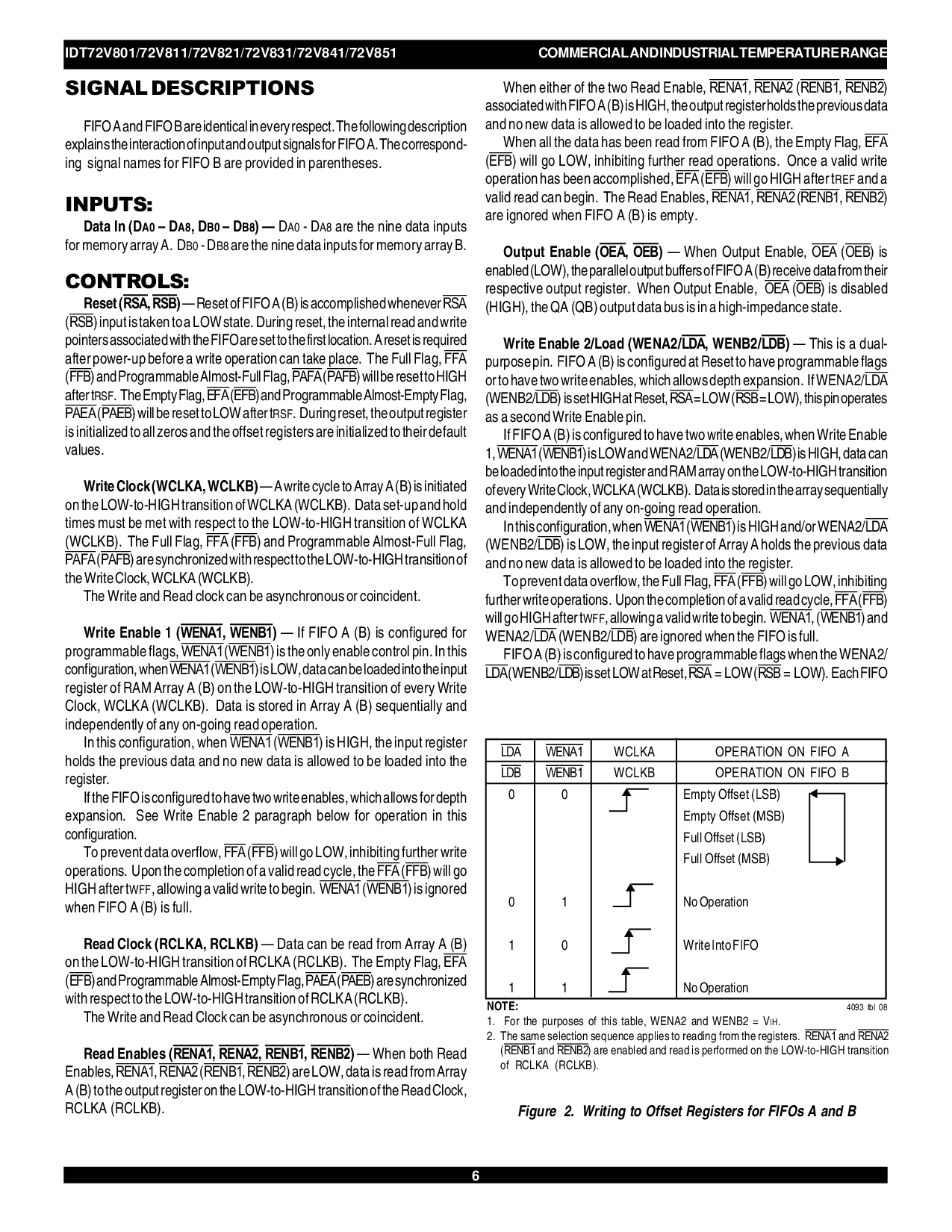

LDA WENA1

WCLKA 运作 在 先进先出 一个

LDB WENB1

WCLKB 运作 在 先进先出 b

0 0 empty 补偿 (lsb)

empty 补偿 (msb)

全部 补偿 (lsb)

全部 补偿 (msb)

0 1 非 运作

1 0 写 在 先进先出

1 1 非 运作

图示 2. writing 至 补偿 寄存器 为 fifos 一个 和 b

当 也 的 这 二 读 使能,

RENA1

,

RENA2

(

RENB1

,

RENB2

)

有关联的 和 先进先出 一个 (b) 是 高, 这 输出 寄存器 holds 这 previous 数据

和 非 新 数据 是 允许 至 是 承载 在 这 寄存器.

当 所有 这 数据 有 被 读 从 先进先出 一个 (b), 这 empty 标记,

EFA

(

EFB

) 将 go 低, inhibiting 更远 读 行动. once 一个 有效的 写

运作 有 被 accomplished,

EFA

(

EFB

) 将 go 高 之后 t

REF

和 一个

有效的 读 能 begin. 这 读 使能,

RENA1

,

RENA2

(

RENB1

,

RENB2

)

是 ignored 当 先进先出 一个 (b) 是 empty.

输出 使能 (

OEA

,

OEB

)

— 当 输出 使能,

OEA

(

OEB

) 是

使能 (低), 这 并行的 输出 缓存区 的 先进先出 一个 (b) receive 数据 从 它们的

各自的 输出 寄存器. 当 输出 使能,

OEA

(

OEB

) 是 无能

(高), 这 qa (qb) 输出 数据 总线 是 在 一个 高-阻抗 状态.

写 使能 2/加载 (wena2/

LDA

, wenb2/

LDB

)

— 这个 是 一个 双-

目的 管脚. 先进先出 一个 (b) 是 配置 在 重置 至 有 可编程序的 flags

或者 至 有 二 写 使能, 这个 准许 depth expansion. 如果 wena2/

LDA

(wenb2/

LDB

)

是 设置 高 在 重置,

RSA

= 低 (

RSB

= 低), 这个 管脚 运作

作 一个 第二 写 使能 管脚.

如果 先进先出 一个 (b) 是 配置 至 有 二 写 使能, 当 写 使能

1,

WENA1

(

WENB1

) 是 低 和 wena2/

LDA

(wenb2/

LDB

) 是 高, 数据 能

是 承载 在 这 输入 寄存器 和 内存 排列 在 这 低-至-高 转变

的 每 写 时钟, wclka (wclkb). 数据 是 贮存 在 这 排列 sequentially

和 independently 的 任何 在-going 读 运作.

在 这个 配置, 当

WENA1

(

WENB1

) 是 高 和/或者 wena2/

LDA

(wenb2/

LDB

) 是 低, 这 输入 寄存器 的 排列 一个 holds 这 previous 数据

和 非 新 数据 是 允许 至 是 承载 在 这 寄存器.

至 阻止 数据 overflow, 这 全部 标记,

FFA

(

FFB

) 将 go 低, inhibiting

更远 写 行动. 在之上 这 completion 的 一个 有效的 读 循环,

FFA

(

FFB

)

将 go 高 之后 t

WFF

, 准许 一个 有效的 写 至 begin.

WENA1

, (

WENB1

) 和

wena2/

LDA

(wenb2/

LDB

) 是 ignored 当 这 先进先出 是 全部.

先进先出 一个 (b) 是 配置 至 有 可编程序的 flags 当 这 wena2/

LDA

(wenb2/

LDB

) 是 设置 低 在 重置,

RSA

= 低 (

RSB

=低). 各自 先进先出

先进先出 一个 和 先进先出 b 是 完全同样的 在 每 遵守. 这 下列的 描述

explains 这 interaction 的 输入 和 输出 信号 为 先进先出 一个. 这 correspond-

ing 信号 names 为 先进先出 b 是 提供 在 parentheses.

数据 在 (d

A0

– d

A8

, d

B0

– d

B8

) —

D

A0

- d

A8

是 这 nine 数据 输入

为 记忆 排列 一个. d

B0

- d

B8

是 这 nine 数据 输入 为 记忆 排列 b.

重置 (

RSA

,

RSB

)

—

重置 的 先进先出 一个 (b) 是 accomplished whenever

RSA

(

RSB

) 输入 是 带去 至 一个 低 状态. 在 重置, 这 内部的 读 和 写

pointers 有关联的 和 这 先进先出 是 设置 至 这 第一 location. 一个 重置 是 必需的

之后 电源-向上 在之前 一个 写 运作 能 引领 放置. 这 全部 标记,

FFA

(

FFB

) 和 可编程序的 almost-全部 标记,

PAFA

(

PAFB

) 将 是 重置 至 高

之后 t

RSF

. 这 empty 标记,

EFA

(

EFB

) 和 可编程序的 almost-empty 标记,

PAEA

(

PAEB

) 将 是 重置 至 低 之后 t

RSF

. 在 重置, 这 输出 寄存器

是 initialized 至 所有 zeros 和 这 补偿 寄存器 是 initialized 至 它们的 default

值.

写 时钟 (wclka, wclkb)

—

一个 写 循环 至 排列 一个 (b) 是 initiated

在 这 低-至-高 转变 的 wclka (wclkb). 数据 设置-向上 和 支撑

时间 必须 是 符合 和 遵守 至 这 低-至-高 转变 的 wclka

(wclkb). 这 全部 标记,

FFA

(

FFB

) 和 可编程序的 almost-全部 标记,

PAFA

(

PAFB

) 是 同步 和 遵守 至 这 低-至-高 转变 的

这 写 时钟, wclka (wclkb).

这 写 和 读 时钟 能 是 异步的 或者 coincident.

写 使能 1 (

WENA1

,

WENB1

)

— 如果 先进先出 一个 (b) 是 配置 为

可编程序的 flags,

WENA1

(

WENB1

) 是 这 仅有的 使能 控制 管脚. 在 这个

配置, 当

WENA1

(

WENB1

) 是 低, 数据 能 是 承载 在 这 输入

寄存器 的 内存 排列 一个 (b) 在 这 低-至-高 转变 的 每 写

时钟, wclka (wclkb). 数据 是 贮存 在 排列 一个 (b) sequentially 和

independently 的 任何 在-going 读 运作.

在 这个 配置, 当

WENA1

(

WENB1

) 是 高, 这 输入 寄存器

holds 这 previous 数据 和 非 新 数据 是 允许 至 是 承载 在 这

寄存器.

如果 这 先进先出 是 配置 至 有 二 写 使能, 这个 准许 为 depth

expansion. 看 写 使能 2 paragraph 在下 为 运作 在 这个

配置.

至 阻止 数据 overflow,

FFA

(

FFB

) 将 go 低, inhibiting 更远 写

行动. 在之上 这 completion 的 一个 有效的 读 循环, 这

FFA

(

FFB

) 将 go

高 之后 t

WFF

, 准许 一个 有效的 写 至 begin.

WENA1

(

WENB1

) 是 ignored

当 先进先出 一个 (b) 是 全部.

读 时钟 (rclka, rclkb)

— 数据 能 是 读 从 排列 一个 (b)

在 这 低-至-高 转变 的 rclka (rclkb). 这 empty 标记,

EFA

(

EFB

) 和 可编程序的 almost-empty 标记,

PAEA

(

PAEB

) 是 同步

和 遵守 至 这 低-至-高 转变 的 rclka (rclkb).

这 写 和 读 时钟 能 是 异步的 或者 coincident.

读 使能 (

RENA1

,

RENA2

,

RENB1

,

RENB2

)

— 当 两个都 读

使能,

RENA1

,

RENA2

(

RENB1

,

RENB2

) 是 低, 数据 是 读 从 排列

一个 (b) 至 这 输出 寄存器 在 这 低-至-高 转变 的 这 读 时钟,

rclka (rclkb).

便条:

4093 tbl 08

1. 为 这 目的 的 这个 表格, wena2 和 wenb2 = v

IH

.

2. 这 一样 选择 sequence 应用 至 读 从 这 寄存器.

RENA1

和

RENA2

(

RENB1

和

RENB2

) 是 使能 和 读 是 执行 在 这 低-至-高 转变

的 rclka (rclkb).