7

idt82v3012 t1/e1/oc3 wan pll 和双 涉及 输入 工业的 温度 范围

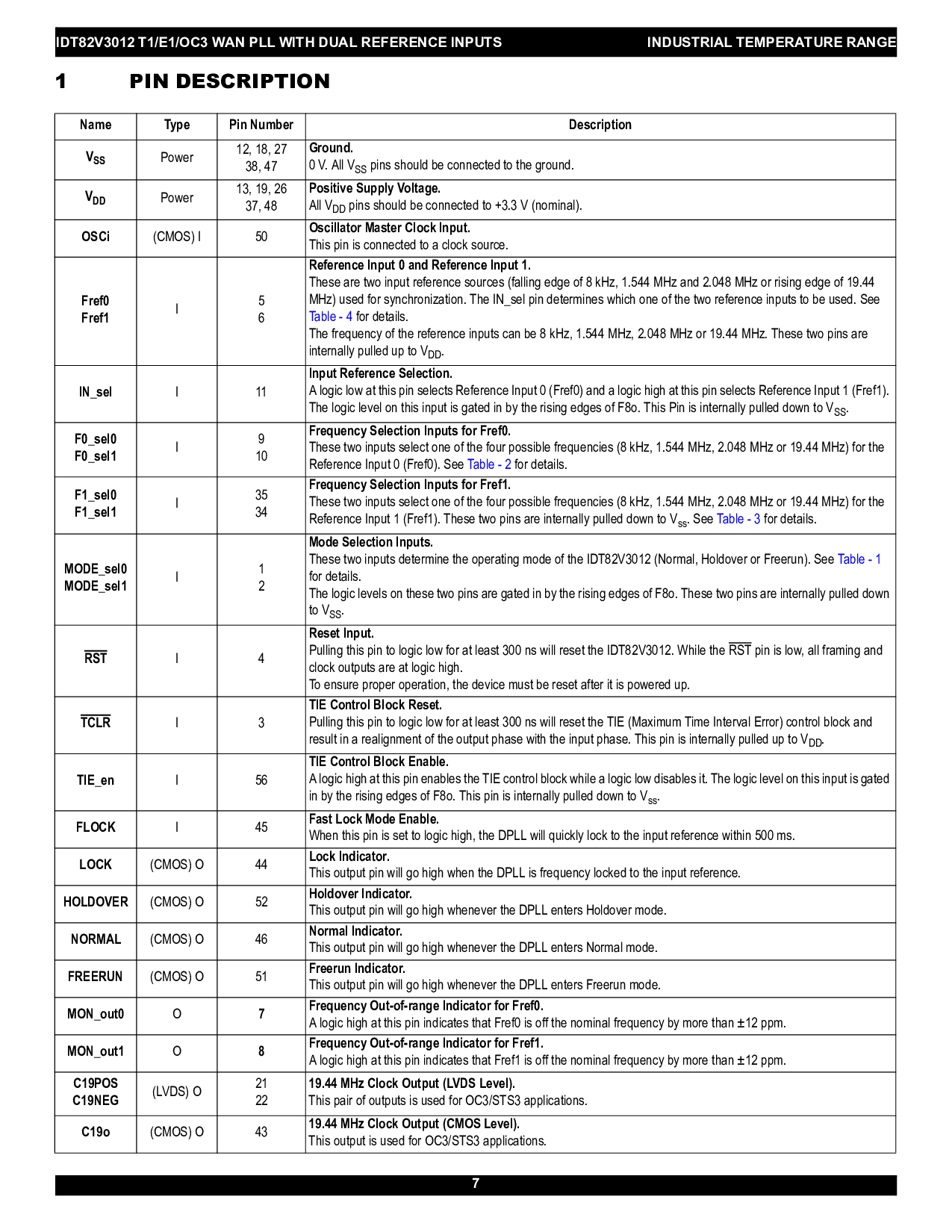

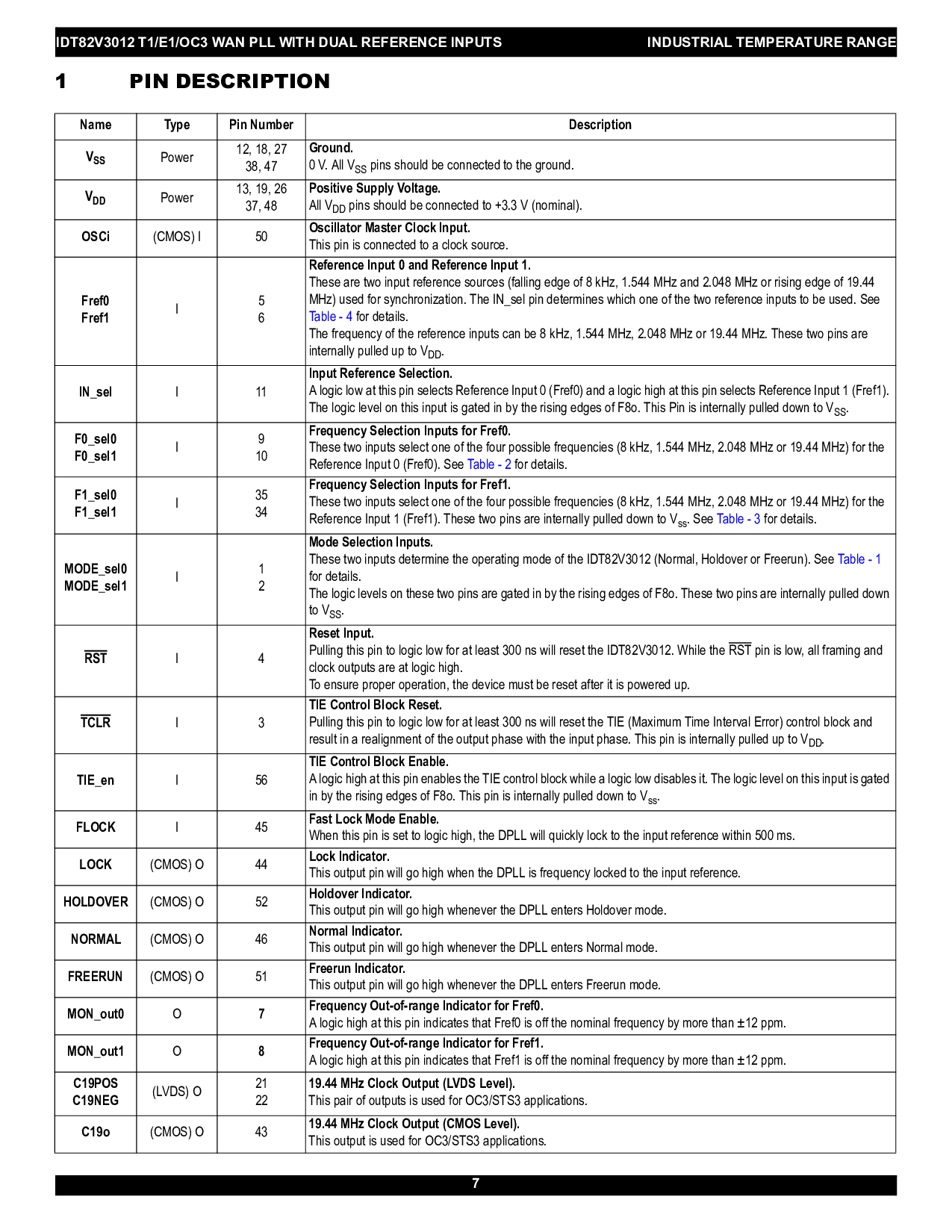

1 管脚 描述

名字 类型 管脚 号码 描述

V

SS

电源

12, 18, 27

38, 47

地面.

0 v. 所有 v

SS

管脚 应当 是 连接 至 这 地面.

V

DD

电源

13, 19, 26

37, 48

积极的 供应 电压.

所有 v

DD

管脚 应当 是 连接 至 +3.3 v (名义上的).

OSCi

(cmos) i 50

振荡器 主控 时钟 输入.

这个 管脚 是 连接 至 一个 时钟 源.

Fref0

Fref1

I

5

6

涉及 输入 0 和 涉及 输入 1.

这些 是 二 输入 涉及 来源 (下落 边缘 的 8 khz, 1.544 mhz 和 2.048 mhz 或者 rising 边缘 的 19.44

mhz) 使用 为 同步. 这 在_sel 管脚 确定 这个 一个 的 这 二 涉及 输入 至 是 使用. 看

Table-4为 详细信息.

这 频率 的 这 涉及 输入 能 是 8 khz, 1.544 mhz, 2.048 mhz 或者 19.44 mhz. 这些 二 管脚 是

内部 牵引的 向上 至 v

DD

.

在_sel

I11

输入 涉及 选择.

一个 逻辑 低 在 这个 管脚 选择 涉及 输入 0 (fref0) 和 一个 逻辑 高 在 这个 管脚 选择 涉及 输入 1 (fref1).

这 逻辑 水平的 在 这个 输入 是 gated 在 用 这 rising edges 的 f8o. 这个 管脚 是 内部 牵引的 向下 至 v

SS

.

f0_sel0

f0_sel1

I

9

10

频率 选择 输入 为 fref0.

这些 二 输入 选择 一个 的 这 四 可能 发生率 (8 khz, 1.544 mhz, 2.048 mhz 或者 19.44 mhz) 为 这

涉及 输入 0 (fref0). 看表格 - 2为 详细信息.

f1_sel0

f1_sel1

I

35

34

频率 选择 输入 为 fref1.

这些 二 输入 选择 一个 的 这 四 可能 发生率 (8 khz, 1.544 mhz, 2.048 mhz 或者 19.44 mhz) 为 这

涉及 输入 1 (fref1). 这些 二 管脚 是 内部 牵引的 向下 至 v

ss

. 看表格 - 3为 详细信息.

模式_sel0

模式_sel1

I

1

2

模式 选择 输入.

这些 二 输入 决定 这 运行 模式 的 the idt82v3012 (正常的, holdover 或者 freerun). 看Table-1

为 详细信息.

这 逻辑 水平 在 这些 二 管脚 是 gated 在 用 这 rising edges 的 f8o. 这些 二 管脚 是 内部 牵引的 向下

至 v

SS

.

RST

I4

重置 输入.

拉 这个 管脚 至 逻辑 低 为 在 least 300 ns 将 重置 这 idt82v3012. 当 这

RST

管脚 是 低, 所有 framing 和

时钟 输出 是 在 逻辑 高.

至 确保 恰当的 运作, 这 设备 必须 是 重置 之后 它 是 powered 向上.

TCLR

I3

系 控制 块 重置.

拉 这个 管脚 至 逻辑 低 为 在 least 300 ns 将 重置 这 系 (最大 时间 间隔 错误) 控制 块 和

结果 在 一个 realignment 的 这 输出 阶段 和 这 输入 阶段. 这个 管脚 是 内部 牵引的 向上 至 v

DD

.

系_en

I56

系 控制 块 使能.

一个 逻辑 高 在 这个 管脚 使能 这 系 控制 块 当 一个 逻辑 低 使不能运转 它. 这 逻辑 水平的 在 这个 输入 是 gated

在 用 这 rising edges 的 f8o. 这个 管脚 是 内部 牵引的 向下 至 v

ss

.

FLOCK

I45

快 锁 模式 使能.

当 这个 管脚 是 设置 至 逻辑 高, 这 dpll 将 quickly 锁 至 这 输入 涉及 在里面 500 ms.

锁

(cmos) o 44

锁 指示信号.

这个 输出 管脚 将 go 高 当 这 dpll 是 频率 锁 至 这 输入 涉及.

HOLDOVER

(cmos) o 52

holdover 指示信号.

这个 输出 管脚 将 go 高 whenever 这 dpll enters holdover 模式.

正常的

(cmos) o 46

正常的 指示信号.

这个 输出 管脚 将 go 高 whenever 这 dpll enters 正常的 模式.

FREERUN

(cmos) o 51

freerun 指示信号.

这个 输出 管脚 将 go 高 whenever 这 dpll enters freerun 模式.

mon_out0

O

7

频率 输出-的-范围 指示信号 为 fref0.

一个 逻辑 高 在 这个 管脚 indicates 那 fref0 是 止 这 名义上的 频率 用 更多 比 ±12 ppm.

mon_out1

O

8

频率 输出-的-范围 指示信号 为 fref1.

一个 逻辑 高 在 这个 管脚 indicates 那 fref1 是 止 这 名义上的 频率 用 更多 比 ±12 ppm.

C19POS

C19NEG

(lvds) o

21

22

19.44 mhz 时钟 输出 (lvds 水平的).

这个 一双 的 输出 是 使用 为 oc3/sts3 产品.

C19o

(cmos) o 43

19.44 mhz 时钟 输出 (cmos 水平的).

这个 输出 是 使用 为 oc3/sts3 产品.