rev. 0

信息 陈设 用 相似物 设备 是 相信 至 是 精确 和

可依靠的. 不管怎样, 非 责任 是 assumed 用 相似物 设备 为 它的

使用, 也不 为 任何 infringements 的 专利权 或者 其它 权利 的 第三 部

这个 将 结果 从 它的 使用. 非 执照 是 准予 用 牵涉 或者

否则 下面 任何 专利权 或者 专利权 权利 的 相似物 设备.

一个

AD6620

一个 技术 方法, p.o. 盒 9106, norwood, 毫安 02062-9106, 美国

电话: 781/329-4700 world 宽 网 站点: http://www.相似物.com

传真: 781/326-8703 © 相似物 设备, inc., 1998

65 msps 数字的 receive

信号 处理器

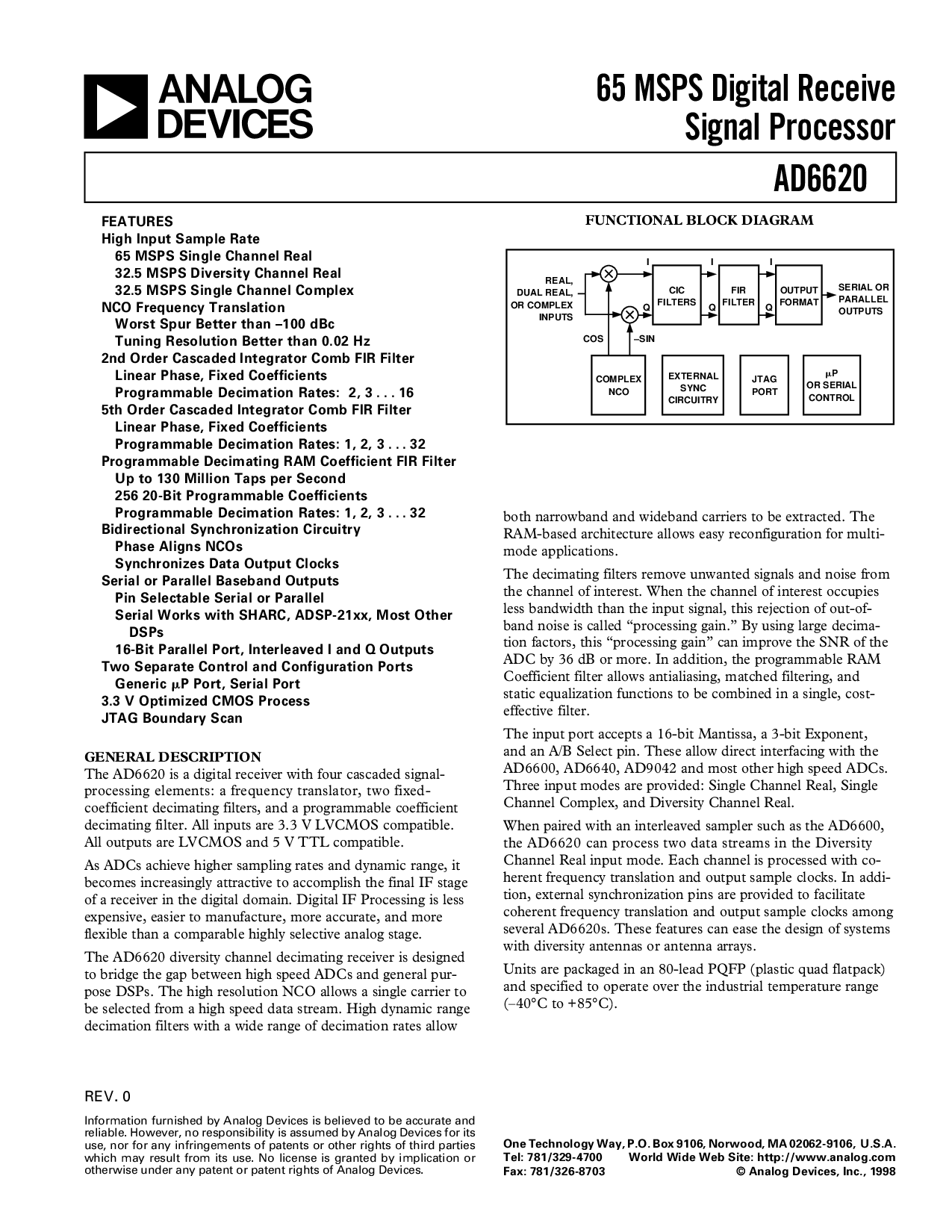

函数的 块 图解

real,

双 real,

或者 complex

输入

串行 或者

并行的

输出

CIC

过滤

输出

FORMAT

COMPLEX

NCO

P

或者 串行

控制

I

Q

–SINCOS

FIR

过滤

外部

同步

电路系统

JTAG

端口

II

QQ

特性

高 输入 样本 比率

65 msps 单独的 频道 real

32.5 msps diversity 频道 real

32.5 msps 单独的 频道 complex

nco 频率 转变

worst spur 更好的 比 –100 dbc

tuning 决议 更好的 比 0.02 hz

2nd 顺序 倾泻 积分器 comb fir 过滤

直线的 阶段, fixed coefficients

可编程序的 decimation 比率: 2, 3 . . . 16

5th 顺序 倾泻 积分器 comb fir 过滤

直线的 阶段, fixed coefficients

可编程序的 decimation 比率: 1, 2, 3 . . . 32

可编程序的 decimating 内存 系数 fir 过滤

向上 至 130 million taps 每 第二

256 20-位 可编程序的 coefficients

可编程序的 decimation 比率: 1, 2, 3 . . . 32

双向的 同步 电路系统

阶段 aligns ncos

synchronizes 数据 输出 clocks

串行 或者 并行的 baseband 输出

管脚 可选择的 串行 或者 并行的

串行 工作 和 sharc, adsp-21xx, 大多数 其它

DSPs

16-位 并行的 端口, interleaved i 和 q 输出

二 独立的 控制 和 配置 端口

Generic

p 端口, 串行 端口

3.3 v 优化 cmos 处理

jtag boundary scan

一般 描述

这 ad6620 是 一个 数字的 接受者 和 四 倾泻 信号-

处理 elements: 一个 频率 翻译, 二 fixed-

coefficient decimating 过滤, 和 一个 可编程序的 系数

decimating 过滤. 所有 输入 是 3.3 v lvcmos 兼容.

所有 输出 是 lvcmos 和 5 v ttl 兼容.

作 adcs 达到 高等级的 抽样 比率 和 动态 范围, 它

变为 increasingly attractive 至 accomplish 这 最终 如果 平台

的 一个 接受者 在 这 数字的 domain. 数字的 如果 处理 是 较少

expensive, easier 至 制造, 更多 精确, 和 更多

有伸缩性的 比 一个 comparable 高级地 选择性的 相似物 平台.

这 ad6620 diversity 频道 decimating 接受者 是 设计

至 桥 这 间隙 在 高 速 adcs 和 一般 pur-

pose dsps. 这 高 决议 nco 准许 一个 单独的 运输车 至

是 选择 从 一个 高 速 数据 stream. 高 动态 范围

decimation 过滤 和 一个 宽 范围 的 decimation 比率 准许

两个都 narrowband 和 wideband carriers 至 是 提取. 这

内存-为基础 architecture 准许 容易 reconfiguration 为 multi-

模式 产品.

这 decimating 过滤 除去 unwanted 信号 和 噪音 从

这 频道 的 interest. 当 这 频道 的 interest occupies

较少 带宽 比 这 输入 信号, 这个 拒绝 的 输出-的-

带宽 噪音 是 called “processing 增益.” 用 使用 大 decima-

tion factors, 这个 “processing gain” 能 改进 这 snr 的 这

模数转换器 用 36 db 或者 更多. 在 增加, 这 可编程序的 内存

系数 过滤 准许 消除走样, matched 过滤, 和

静态的 equalization 功能 至 是 联合的 在 一个 单独的, 费用-

有效的 过滤.

这 输入 端口 accepts 一个 16-位 mantissa, 一个 3-位 exponent,

和 一个 一个/b 选择 管脚. 这些 准许 直接 接合 和 这

ad6600, ad6640, ad9042 和 大多数 其它 高 速 adcs.

三 输入 模式 是 提供: 单独的 频道 real, 单独的

频道 complex, 和 diversity 频道 real.

当 paired 和 一个 interleaved sampler 此类 作 这 ad6600,

这 ad6620 能 处理 二 数据 streams 在 这 diversity

频道 real 输入 模式. 各自 频道 是 processed 和 co-

herent 频率 转变 和 输出 样本 clocks. 在 addi-

tion, 外部 同步 管脚 是 提供 至 facilitate

coherent 频率 转变 和 输出 样本 clocks among

一些 ad6620s. 这些 特性 能 使容易 这 设计 的 系统

和 diversity antennas 或者 触角 arrays.

单位 是 packaged 在 一个 80-含铅的 pqfp (塑料 四方形 flatpack)

和 指定 至 运作 在 这 工业的 温度 范围

(–40

°

c 至 +85

°

c).