© 2001 xilinx, 公司 所有 权利 保留. 所有 xilinx 商标, 注册 商标, patents, 和 免责声明 是 作 列表 一个t

http://www.xilinx.com/legal.htm

.

所有 其它 商标 和 注册 商标 是 这 恰当的ty 的 它们的 各自的 所有权人. 所有 规格 是 主题 至 change 没有 注意.

ds003-1 (v2.5 ) april 2, 2001

www.xilinx.com

单元 1 的 4

产品 规格

1-800-255-7778 1

特性

• 快, 高-密度 地方-可编程序的 门 arrays

- densities 从 50k 至 1m 系统 门

- 系统 效能 向上 至 200 mhz

- 66-mhz pci 一致的

- hot-swappable 为 紧凑的 pci

• multi-标准 selectio™ 接口

- 16 高-效能 接口 standards

- connects 直接地 至 zbtram 设备

• 建造-在 时钟-管理 电路系统

- 四 专心致志的 延迟-锁 循环 (dlls) 为

先进的 时钟 控制

- 四 primary 低-skew global 时钟 分发

nets, 加 24 secondary local 时钟 nets

• hierarchical 记忆 系统

- luts configurable 作 16-位 内存, 32-位 内存,

16-位 双-ported 内存, 或者 16-位 变换 寄存器

- configurable 同步的 双-ported 4k-位

RAMs

- 快 接口 至 外部 高-效能 rams

• 有伸缩性的 architecture 那 balances 速 和 密度

- 专心致志的 carry 逻辑 为 高-速 arithmetic

- 专心致志的 乘法器 支持

- cascade chain 为 宽-输入 功能

- abundant 寄存器/latches 和 时钟 使能, 和

双 同步的/异步的 设置 和 重置

- 内部的 3-状态 bussing

- ieee 1149.1 boundary-scan 逻辑

- 消逝-温度 传感器 二极管

• supported 用 fpga foundation™ 和 alliance

开发 系统

- 完全 support 为 unified libraries, relationally

放置 macros, 和 设计 manager

- 宽 选择 的 pc 和 workstation platforms

• sram-为基础 在-系统 配置

- unlimited re-programmability

- 四 程序编制 模式

•0.22

m

m 5-layer metal 处理

• 100% 工厂 测试

描述

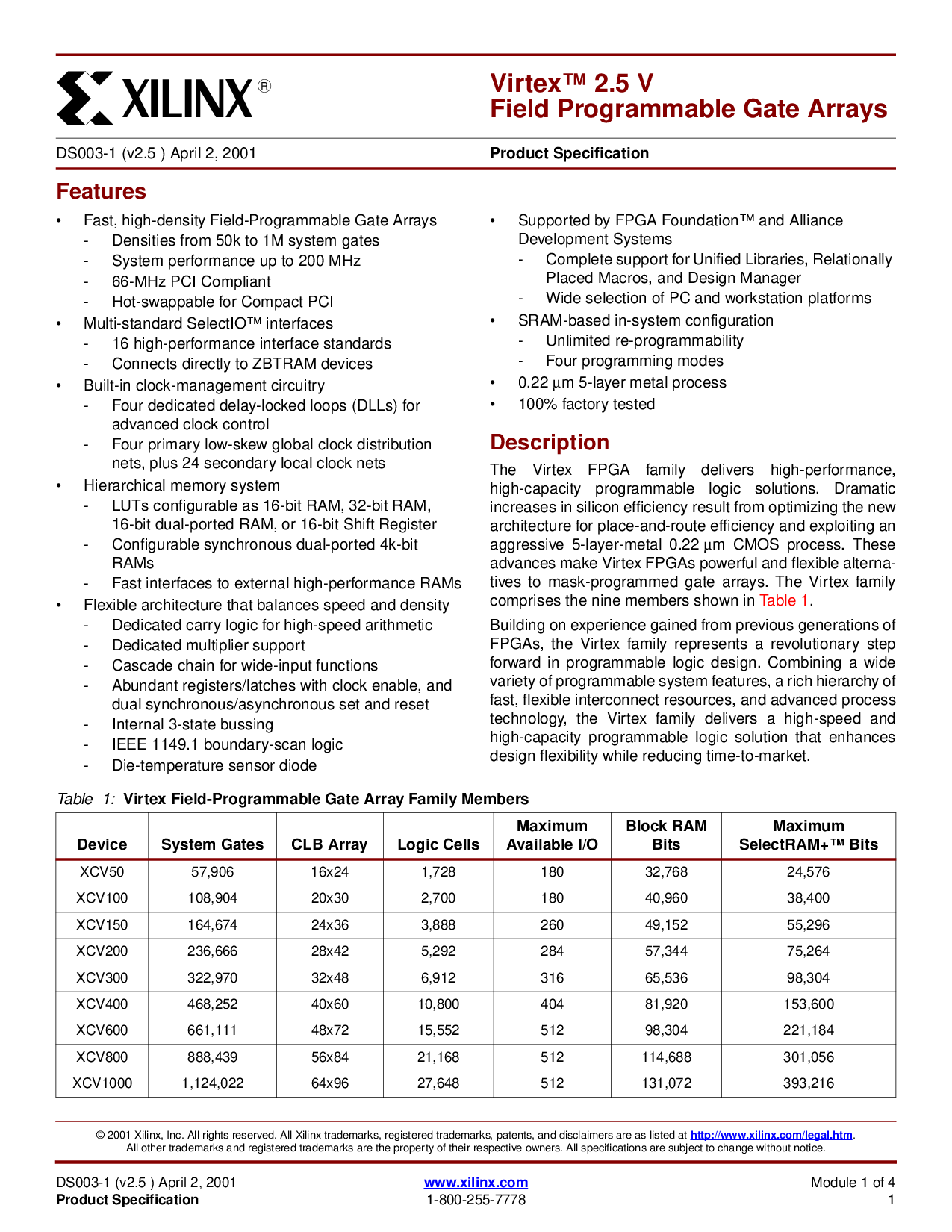

这 virtex fpga 家族 delivers 高-效能,

高-capacity 可编程序的 逻辑 解决方案. dramatic

增加 在 硅 效率 结果 从 optimizing 这 新

architecture 为 放置-和-route 效率 和 exploiting 一个

aggressive 5-layer-metal 0.22

m

m cmos 处理. 这些

advances 制造 virtex fpgas powerful 和 有伸缩性的 alterna-

tives 至 掩饰-编写程序 门 arrays. 这 virtex 家族

comprises 这 nine members 显示 在Table 1.

building 在 experience gained 从 previous generations 的

fpgas, 这 virtex 家族 代表 一个 revolutionary 步伐

向前 在 可编程序的 逻辑 设计. 结合 一个 宽

多样性 的 可编程序的 系统 特性, 一个 rich hierarchy 的

快, 有伸缩性的 interconnect resources, 和 先进的 处理

技术, 这 virtex 家族 delivers 一个 高-速 和

高-capacity 可编程序的 逻辑 解决方案 那 enhances

设计 flexibility 当 减少 时间-至-market.

0

virtex™ 2.5 v

地方 可编程序的 门 Arrays

ds003-1 (v2.5 ) april 2, 2001

03

产品 规格

R

表格 1:

virtex 地方-可编程序的 门 排列 家族 members

设备 系统 门 clb 排列 逻辑 cells

最大

有 i/o

块 内存

位

最大

SelectRAM+

™

位

XCV50 57,906 16x24 1,728 180 32,768 24,576

XCV100 108,904 20x30 2,700 180 40,960 38,400

XCV150 164,674 24x36 3,888 260 49,152 55,296

XCV200 236,666 28x42 5,292 284 57,344 75,264

XCV300 322,970 32x48 6,912 316 65,536 98,304

XCV400 468,252 40x60 10,800 404 81,920 153,600

XCV600 661,111 48x72 15,552 512 98,304 221,184

XCV800 888,439 56x84 21,168 512 114,688 301,056

XCV1000 1,124,022 64x96 27,648 512 131,072 393,216