将 2003

1

© 2003 actel 公司

*see actel’s 网站 用于 这 最新 版本 的 这 数据表.

v3.0

ProASIC

加号

闪光灯 家庭 fpgas

tm

特点 和 好处

高 容量

• 75,000 至 1 百万 系统 盖茨

• 27k 至 198kbits 的 两个-港口 sram

• 66 至 712 用户 我/操作系统

可重新编程 闪光灯 技术

•0.22

µ 4

lm 闪光灯-基于 cmos 流程

• live 在 电源-向上, 单芯片 解决方案

• 否 配置 设备 必填项

• 保留 编程 设计 期间 电源-向下/

通电 循环次数

业绩

• 3.3v, 32-有点 pci (向上 至 50 mhz)

• 两个 综合 plls

• 外部 系统 业绩 向上 至 150 mhz

安全 编程

• 这 行业’s 大多数 有效 安全 钥匙 (flashlock

)

防止 阅读 背面 的 编程 比特流

低 电源

• 低 阻抗 闪光灯 开关

• 分段 hierarchical 路由 结构

• 小, 高效, 可配置 (组合 或

顺序) 逻辑 细胞

高 业绩 路由 层次结构

• 超-快 本地 和 长-线 网络

• 高 速度 很 长-线 网络

• 高 业绩, 低 偏斜, splittable 全球 网络

• 100% routability 和 利用率

我/o

• 施密特-触发器 选项 开启 每 输入

• 混合 2.5v/3.3v 支持 与 单独-可选择

电压 和 回转 费率

• 双向 全球 我/操作系统

• 合规性 与 pci 规格 修订 2.2

• 边界扫描 测试一下 ieee 标准. 1149.1 (jtag) 符合

• 管脚 兼容 软件包 跨越 proasic

加号

家庭

独一无二 时钟 调节 电路

• pll 与 灵活 相位, 相乘/除法 和 延迟

能力

• 内部 和/或 外部 动态 pll 配置

• 两个 lvpecl 差速器 对 用于 时钟 或 数据 输入

标准 fpga 和 asic 设计 流量

• 灵活性 与 选择 的 行业标准 frontend

工具

• 高效 设计 通过 frontend 计时 和 闸门

优化

isp 支持

• 在系统内 编程 (isp) 通过 jtag 港口

srams 和 fifos

• actgen 网表 世代 确保 最优 用法 的

嵌入式 记忆 块

• 24 sram 和 先进先出 配置 与 同步 和

异步 操作 向上 至 150 mhz (典型)

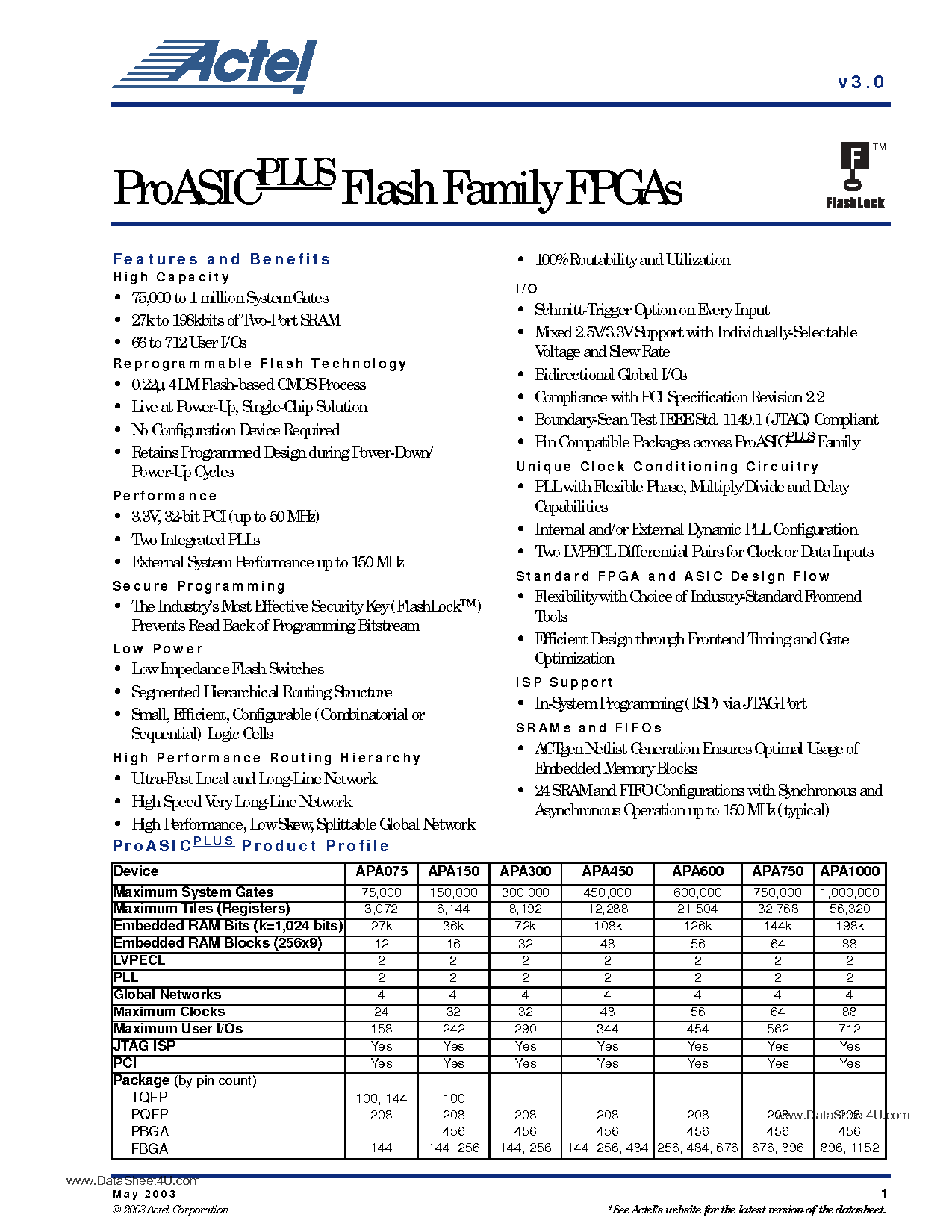

ProASIC

加号

产品 配置文件

设备 APA075 APA150 APA300 APA450 APA600 APA750 APA1000

最大值 系统 盖茨

75,000 150,000 300,000 450,000 600,000 750,000 1,000,000

最大值 tiles (寄存器)

3,072 6,144 8,192 12,288 21,504 32,768 56,320

嵌入式 ram 比特 (k=1,024 比特)

27k 36k 72k 108k 126k 144k 198k

嵌入式 ram 块 (256x9)

12 16 32 48 56 64 88

lvpe?cl

222 2 2 22

PLL

222 2 2 22

全球 网络

444 4 4 44

最大值 时钟

24 32 32 48 56 64 88

最大值 用户 我/操作系统

158 242 290 344 454 562 712

jtag isp

Yes Yes Yes Yes Yes Yes Yes

PCI

Yes Yes Yes Yes Yes Yes Yes

包装

(由 管脚 计数)

TQFP

PQFP

PBGA

FBGA

100, 144

208

144

100

208

456

144, 256

208

456

144, 256

208

456

144, 256, 484

208

456

256, 484, 676

208

456

676, 896

208

456

896, 1152

www.datasheet4u.com

www.datasheet4u.com

www.datasheet4u.com