200-mhz 24-输出 缓冲区 用于 4 ddr

或 3 sdram dimms

W255

柏树 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文件 #: 38-07255 rev. *c 修订 12月 14, 2002

特点

• 一个 输入 至 24-输出 缓冲区/驾驶员

• 支架 向上 至 4 ddr dimms 或 3 sdram dimms

• 一个 附加 输出 用于 反馈

• smbus 接口 用于 个人 输出 控制

• 低 偏斜 产出 (&指示灯; 100 ps)

• 支架 266-, 333-, 和 400-mhz ddr sdram

• 专用 管脚 用于 电源 管理 支持

• 节省空间 48-管脚 ssop 包装

功能 描述

这 w255 是 一个 3.3v/2.5v 缓冲区 设计 至 分发

高速 时钟 入点 pc 应用程序. 这 零件 有 24 产出.

设计师 可以 配置 这些 产出 至 支持 四 unbuf-

fered ddr dimms 或 至 支持 三个 无缓冲 标准

sdram dimms 和 两个 ddr dimms. 这 w255 可以 是 已使用

入点 连接词 与 这 w250 或 类似 时钟 合成器 用于

这 通过 专业版 266 芯片组.

这 w255 也 包括 一个 smbus 接口 哪个 可以 启用

或 禁用 每个 输出 时钟. 开启 电源-向上, 全部 输出 时钟

是 已启用 (内部 拉 向上).

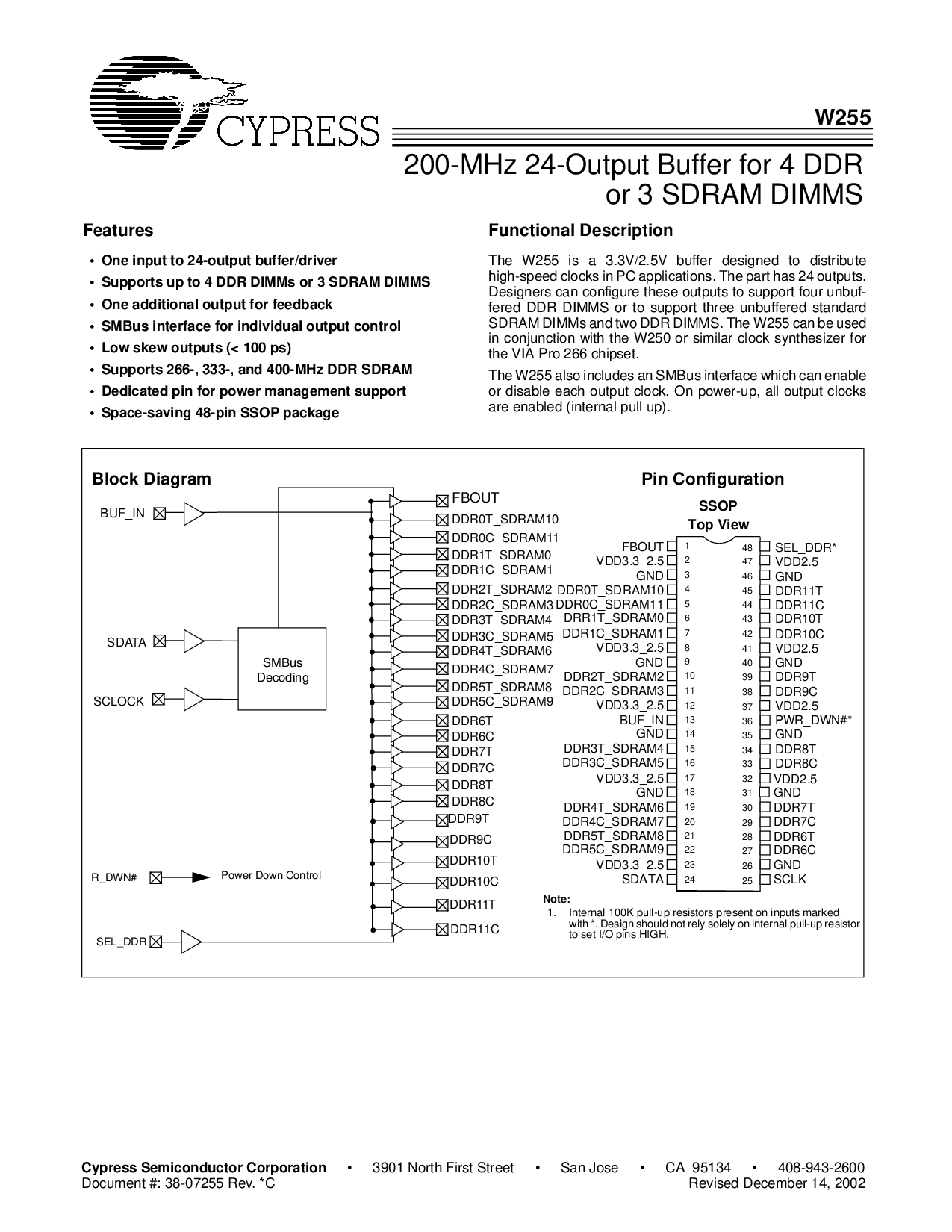

块 图表

SMBus

buf_入点

SDATA

SCLOCK

ddr0t_sdram10

ddr0c_sdram11

ddr1t_sdram0

ddr1c_sdram1

ddr2t_sdram2

ddr2c_sdram3

ddr3t_sdram4

ddr3c_sdram5

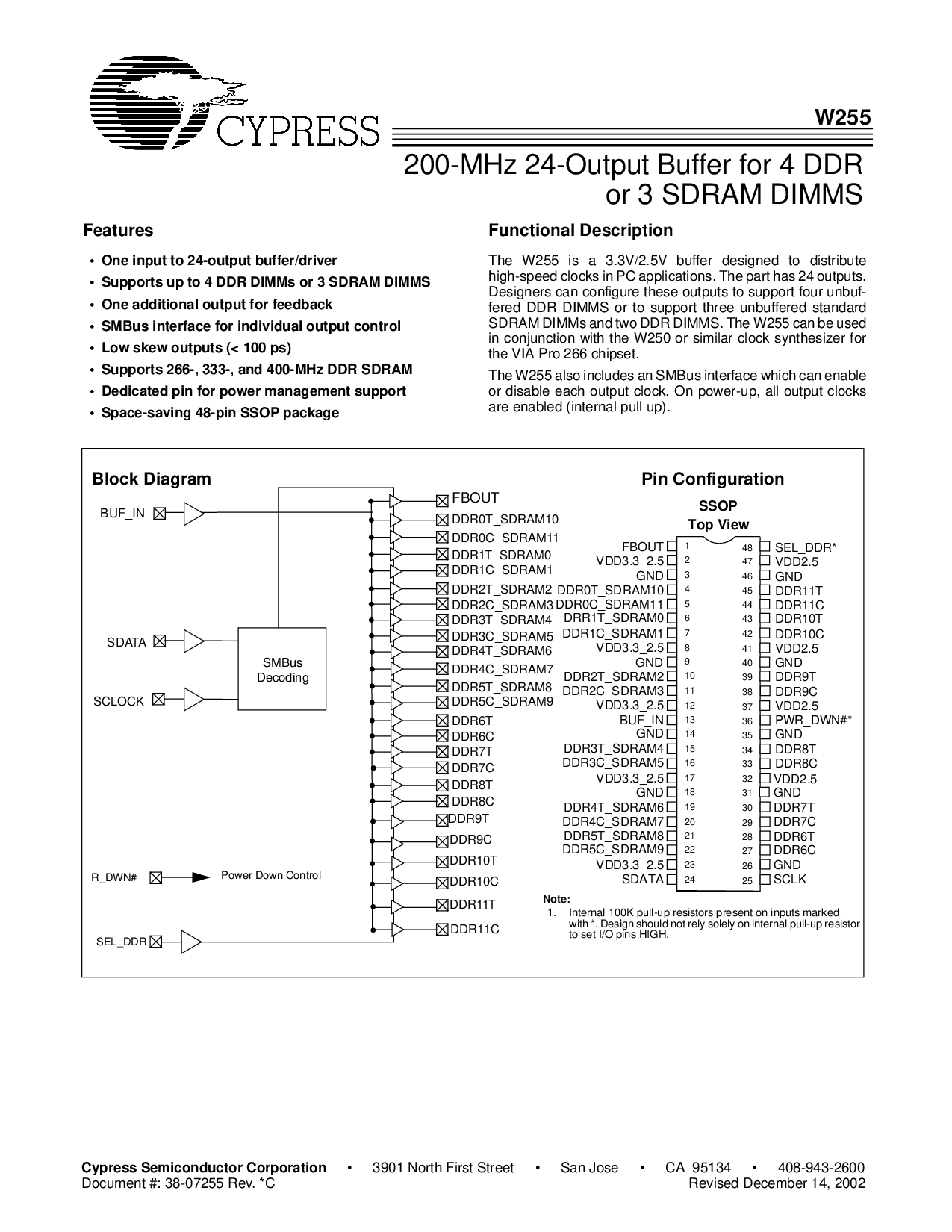

1

2

3

4

选择_ddr*

vdd2.5

地

DDR11T

DDR11C

DDR10T

DDR10C

vdd2.5

SSOP

顶部 查看

管脚 配置

解码

8

5

6

7

12

9

10

11

13

14

15

16

20

17

18

19

24

21

22

23

48

47

46

45

41

44

43

42

37

40

39

38

36

35

34

33

29

32

31

30

25

28

27

26

地

DDR9T

DDR9C

vdd2.5

pwr_dwn#*

地

DDR8T

DDR8C

vdd2.5

地

DDR7T

DDR7C

DDR6T

DDR6C

地

SCLK

FBOUT

vdd3.3_2.5

地

ddr0t_sdram10

ddr0c_sdram11

drr1t_sdram0

ddr1c_sdram1

vdd3.3_2.5

ddr2t_sdram2

ddr2c_sdram3

vdd3.3_2.5

buf_入点

地

ddr3t_sdram4

ddr3c_sdram5

vdd3.3_2.5

地

ddr4t_sdram6

ddr4c_sdram7

ddr5t_sdram8

ddr5c_sdram9

vdd3.3_2.5

SDATA

地

ddr4t_sdram6

ddr4c_sdram7

ddr5t_sdram8

ddr5c_sdram9

DDR6T

DDR6C

DDR7T

DDR7C

DDR8T

DDR8C

右_dwn#

DDR9T

DDR9C

DDR10T

DDR10C

DDR11T

DDR11C

FBOUT

电源 向下 控制

选择_ddr

备注:

1. 内部 100k 上拉 电阻 目前 开启 输入 已标记

与 *. 设计 应该 不 依靠 仅 开启 内部 上拉 电阻

至 设置 我/o 针脚 高.