ics9112-18

零 延迟, 低 skew 缓存区

mds 9112-18 f

1 修订 050400 打印 11/15/00

整体的 电路 系统, inc.• 525 race 街道 • san jose • ca • 95126 • (408)295-9800tel• www.icst.com

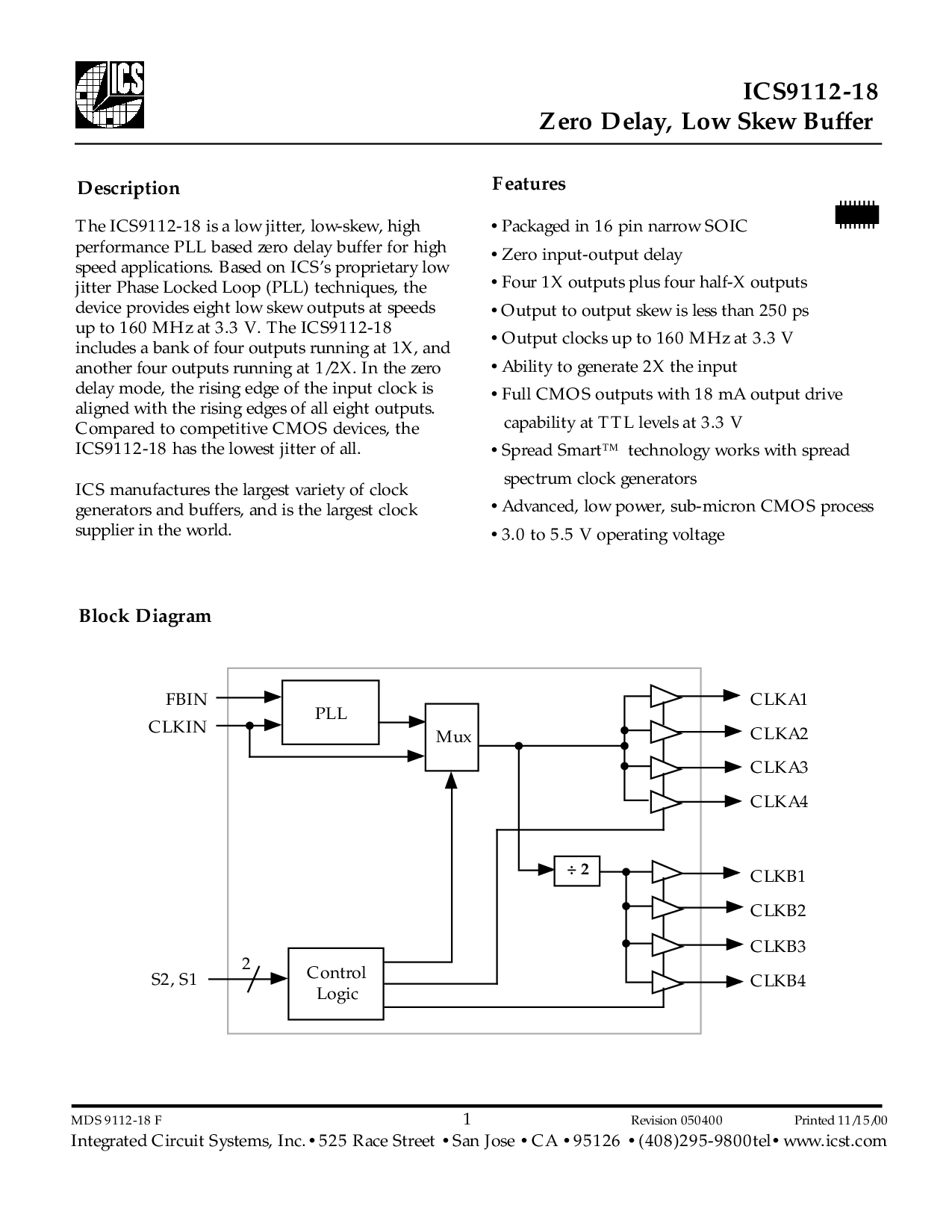

块 图解

描述

特性

这 ics9112-18 是 一个 低 jitter, 低-skew, 高

效能 pll 为基础 零 延迟 缓存区 为 高

速 产品. 为基础 在 ics’s 专卖的 低

jitter 阶段 锁 循环 (pll) 技巧, 这

设备 提供 第八 低 skew 输出 在 speeds

向上 至 160 mhz 在 3.3 v. 这 ics9112-18

包含 一个 bank 的 四 输出 运动 在 1x, 和

另一 四 输出 运动 在 1/2x. 在 这 零

延迟 模式, 这 rising 边缘 的 这 输入 时钟 是

排整齐 和 这 rising edges 的 所有 第八 输出.

对照的 至 competitive cmos 设备, 这

ics9112-18 有 这 最低 jitter 的 所有.

ics manufactures 这 largest 多样性 的 时钟

发生器 和 缓存区, 和 是 这 largest 时钟

供应者 在 这 world.

• packaged 在 16 管脚 narrow soic

• 零 输入-输出 延迟

• 四 1x 输出 加 四 half-x 输出

• 输出 至 输出 skew 是 较少 比 250 ps

• 输出 clocks 向上 至 160 mhz 在 3.3 v

• 能力 至 发生 2x 这 输入

• 全部 cmos 输出 和 18 毫安 输出 驱动

能力 在 ttl 水平 在 3.3 v

• 展开 smart™ 技术 工作 和 展开

spectrum 时钟 发生器

• 先进的, 低 电源, sub-micron cmos 处理

• 3.0 至 5.5 v 运行 电压

PLL

CLKA1FBIN

Mux

CLKA2

s2, s1

2

÷ 2

CLKA3

CLKA4

CLKB1

CLKB2

CLKB3

CLKB4

控制

逻辑

CLKIN