应用 Hints

(持续)

width 如果 这个 做 不 提供 一个 sufficient 数据 支撑 时间 在

这 终止 的 这 写 cycle 一个 负的 边缘 triggered 一个-

shot 能 是 包含 在 这 系统 写 strobe 和

这 WR

管脚 的 这 DAC 这个 是 illustrated 在

图示 6

为 一个

exemplary 系统 这个 提供 一个 250 ns WR

strobe 时间

和 一个 数据 支撑 时间 的 仅有的 10 ns

这 恰当的 数据 设置-向上 时间 较早的 至 这 闭锁 边缘 (低

至 高 转变) 的 这 WR

strobe 是 insured 如果 这 WR

脉冲波 宽度 是 在里面 规格 和 这 数据 是 有效的 在 这 总线 为

这 持续时间 的 这 DAC WR

strobe

19 数字的 信号 Feedthrough

一个 典型 微处理器 是 一个 tremendous 潜在的 源

的 高 频率 噪音 这个 能 是 结合 至 敏感的

相似物 circuitry 这 快 edges 的 这 数据 和 地址 总线

信号 发生 频率 组件 的 10’s 的 mega-

hertz 和 将 导致 快 过往旅客 至 呈现 在 这 DAC

output 甚至 当 数据 是 latched internally

在 低 频率 或者 直流 applications 低 通过 过滤 能

减少 这 巨大 的 任何 快 transients 这个 是 大多数

容易地 accomplished 用 在-compensating 这 DAC 输出

放大器 用 增加 这 值 的 它的 反馈 capacitor

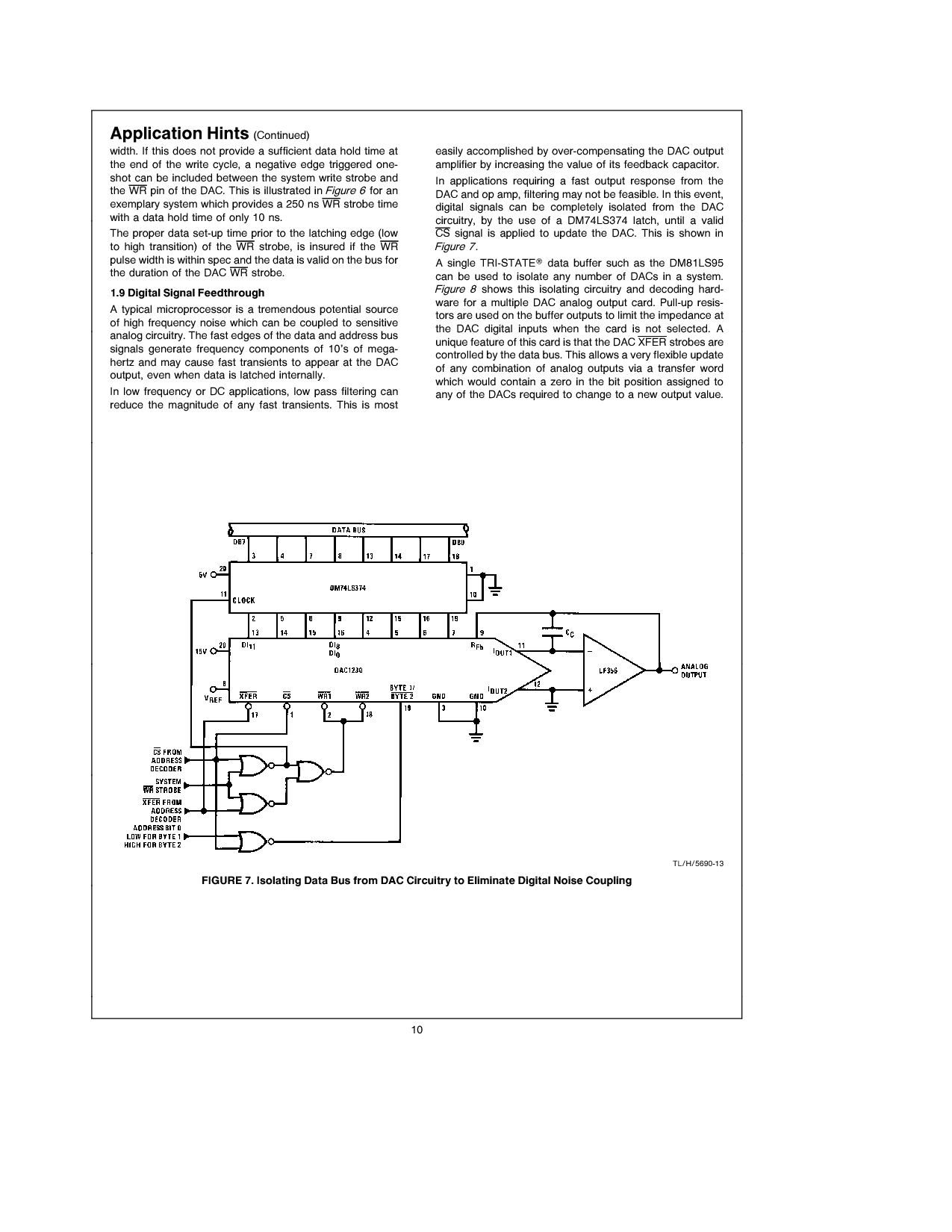

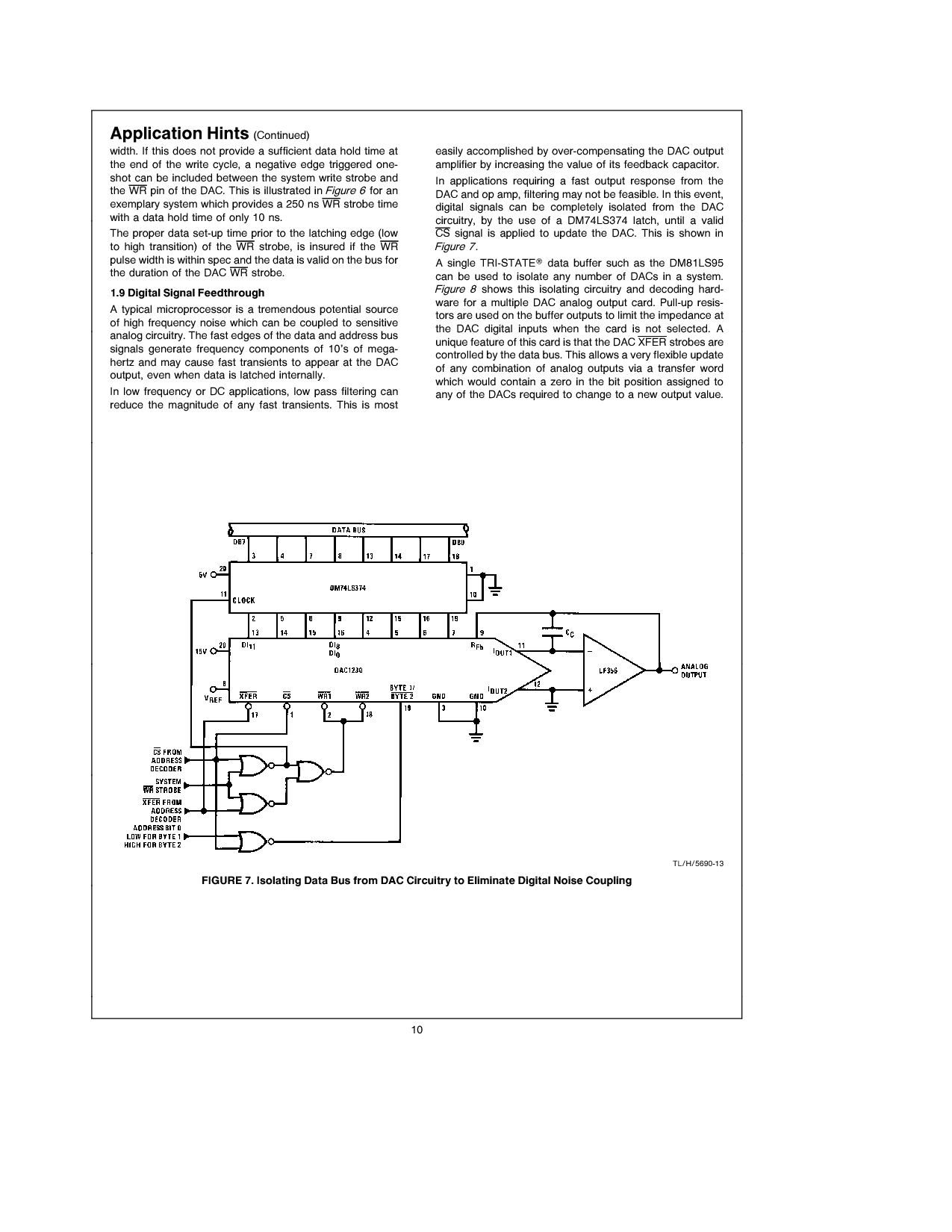

在 产品 需要 一个 快 输出 回馈 从 这

DAC 和 运算 amp 过滤 将 不 是 feasible 在 这个 event

数字的 信号 能 是 完全地 分开的 从 这 DAC

circuitry 用 这 使用 的 一个 DM74LS374 latch 直到 一个 有效的

CS

信号 是 应用 至 更新 这 DAC 这个 是 显示 在

图示 7

一个 单独的 触发-状态

数据 缓存区 此类 作 这 DM81LS95

能 是 使用 至 分开 任何 号码 的 DACs 在 一个 system

图示 8

显示 这个 isolating 电路系统 和 解码 hard-

ware 为 一个 多样的 DAC 相似物 输出 card 拉-向上 resis-

tors 是 使用 在 这 缓存区 输出 至 限制 这 阻抗 在

这 DAC 数字的 输入 当 这 card 是 不 selected 一个

唯一的 特性 的 这个 card 是 那 这 DAC XFER

strobes 是

控制 用 这 数据 bus 这个 准许 一个 非常 有伸缩性的 更新

的 任何 结合体 的 相似物 输出 通过 一个 转移 文字

这个 将 包含 一个 零 在 这 位 位置 assigned 至

任何 的 这 DACs 必需的 至 改变 至 一个 新 输出 value

tlh5690-13

图示 7 Isolating 数据 总线 从 DAC 电路系统 至 Eliminate 数字的 噪音 连接

10