rev. 0

AD1958

–5–

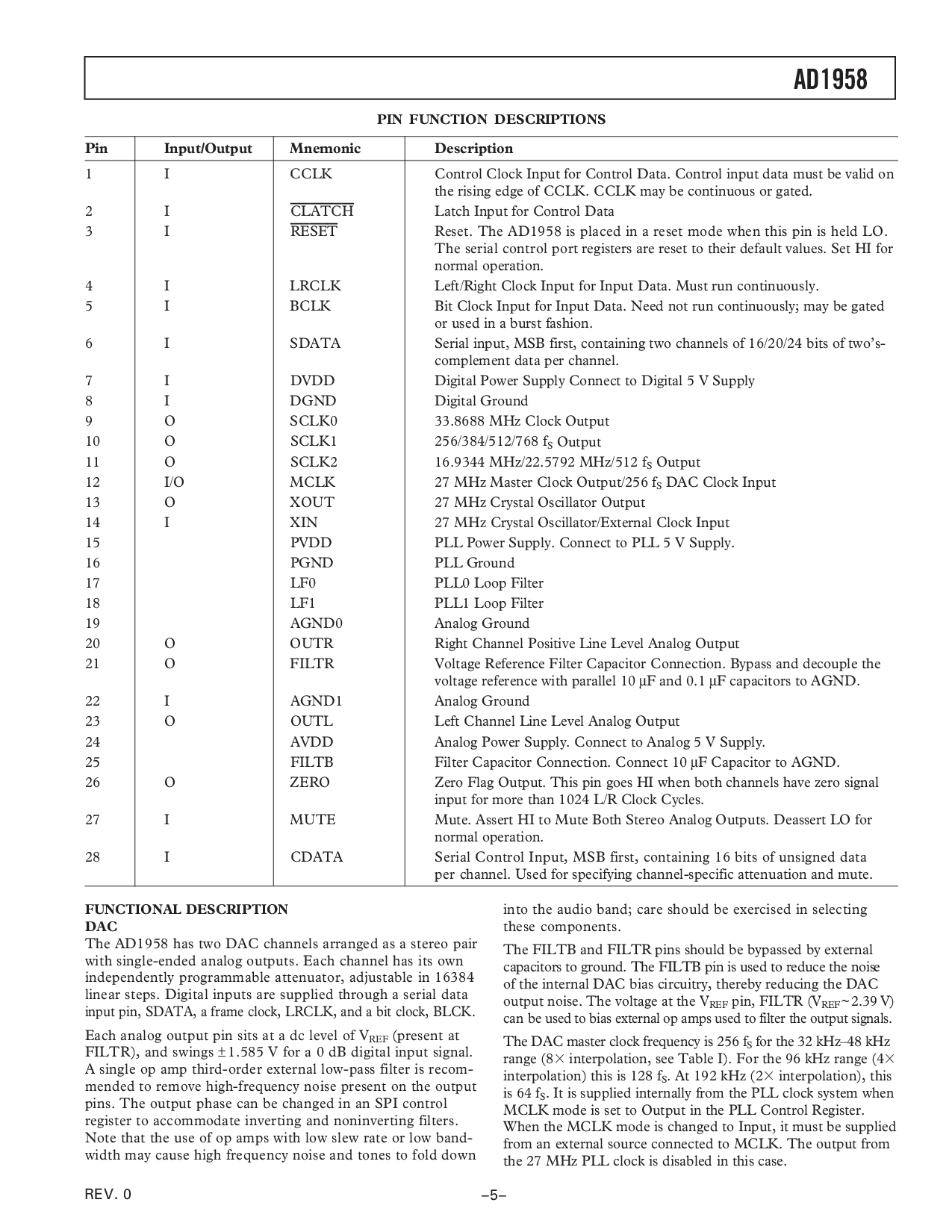

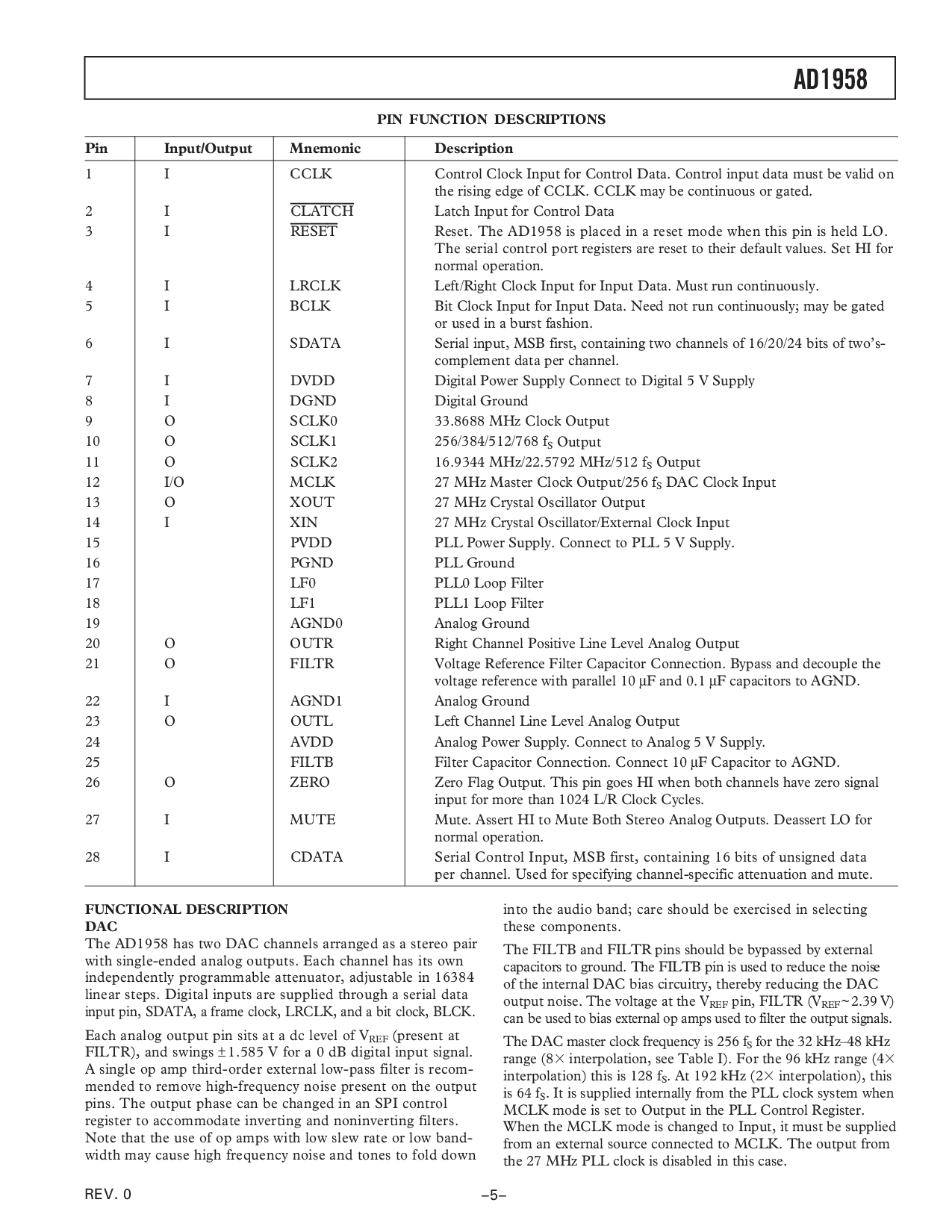

管脚 函数 描述

管脚 输入/输出 Mnemonic 描述

1 I CCLK 控制 时钟 输入 为 控制 数据. 控制 输入 数据 必须 是 有效的 在

这 rising 边缘 的 cclk. cclk 将 是 持续的 或者 gated.

2I

CLATCH

获得 输入 为 控制 数据

3I

重置

重置. 这 ad1958 是 放置 在 一个 重置 模式 当 这个 管脚 是 使保持 lo.

这 串行 控制 端口寄存器 是 重置 至 它们的 default 值. 设置 hi 为

正常的 运作.

4 I LRCLK left/正确的 时钟 输入 为 输入 数据. 必须 run continuously.

5 I BCLK 位 时钟 输入 为 输入 数据. 需要 不 run continuously; 将 是 gated

或者 使用 在 一个 burst fashion.

6 I SDATA 串行 输入, msb 第一, containing 二 途径 的 16/20/24 位 的 二’s-

complement 数据 每 频道.

7 I DVDD 数字的 电源 供应 连接 至 数字的 5 v 供应

8 I DGND 数字的 地面

9 O SCLK0 33.8688 mhz 时钟 输出

10 O SCLK1 256/384/512/768 f

S

输出

11 O SCLK2 16.9344 mhz/22.5792 mhz/512 f

S

输出

12 i/o MCLK 27 mhz 主控 时钟 输出/256 f

S

dac 时钟 输入

13 O XOUT 27 mhz 结晶 振荡器 输出

14 I XIN 27 mhz 结晶 振荡器/外部 时钟 输入

15 PVDD pll 电源 供应. 连接 至 pll 5 v 供应.

16 PGND pll 地面

17 LF0 pll0 循环 过滤

18 LF1 pll1 循环 过滤

19 AGND0 相似物 地面

20 O OUTR 正确的 频道 积极的 线条 水平的 相似物 输出

21 O FILTR 电压 涉及 过滤 电容 连接. 绕过 和 分离 这

电压 涉及 和 并行的 10

µ

f 和 0.1

µ

f 电容 至 agnd.

22 I AGND1 相似物 地面

23 O OUTL left 频道 线条 水平的 相似物 输出

24 AVDD 相似物 电源 供应. 连接 至 相似物 5 v 供应.

25 FILTB 过滤 电容 连接. 连接 10

µ

f 电容 至 agnd.

26 O 零 零 标记 输出. 这个 管脚 变得 hi 当 两个都 途径 有 零 信号

输入 为 更多 比 1024 l/r 时钟 循环.

27 I 沉默的 沉默的. assert hi 至 沉默的 两个都 立体的 相似物 输出. deassert lo 为

正常的 运作.

28 I CDATA 串行 控制 输入, msb 第一, containing 16 位 的 unsigned 数据

每频道. 使用 为 specifying 频道-明确的 attenuation 和 沉默的.

函数的 描述

DAC

这 ad1958 有 二 dac 途径 arranged 作 一个 立体的 一双

和 单独的-结束 相似物 输出. 各自 频道 有 它的 自己的

independently 可编程序的 attenuator, 可调整的 在 16384

直线的 步伐. 数字的 输入 是 有提供的 通过 一个 串行 数据

输入 管脚, sdata, 一个 框架 时钟, lrclk, 和 一个 位 clock, blck.

各自 相似物 输出 管脚 sits 在 一个 直流 水平的 的 v

REF

(呈现 在

filtr), 和 swings

±

1.585 v 为 一个 0 db 数字的 输入 信号.

一个 单独的 运算 放大 第三-顺序 外部 低-通过 过滤 是 recom-

mended 至 除去 高-频率 噪音 呈现 在 这 输出

管脚. 这 输出 阶段 能 是 changed 在 一个 spi 控制

寄存器 至 accommodate 反相的 和 同相 过滤.

便条 那 这 使用 的 运算 放大器 和 低 回转 比率 或者 低 带宽-

宽度 将 导致 高 频率 噪音 和 tones 至 fold 向下

在 这 音频的 带宽; 小心 应当 是 exercised 在 selecting

这些 组件.

这 filtb 和 filtr 管脚 应当 是 绕过 用 外部

电容 至 地面. 这 filtb 管脚 是 使用 至 减少 这 噪音

的 这 内部的 dac 偏差 电路系统, 因此 减少 这 dac

输出 噪音. 这 电压 在 这 v

REF

管脚, filtr (v

REF

~ 2.39 v)

能 是 使用 至 偏差 外部 运算 放大器 使用 至 过滤 这 输出 信号.

这 dac 主控 时钟 频率 是 256 f

S

为 这 32 khz–48 khz

范围 (8

interpolation, 看 表格 i). 为 这 96 khz 范围 (4

interpolation) 这个 是 128 f

S

. 在 192 khz (2

interpolation), 这个

是 64 f

S

. 它 是 有提供的 内部 从 这 pll 时钟 系统 当

mclk 模式 是 设置 至 输出 在 这 pll 控制 寄存器.

当 这 mclk 模式 是 changed 至 输入, 它 必须 是 有提供的

从 一个 外部 源 连接 至 mclk. 这 输出 从

这 27 mhz pll 时钟 是 无能 在 这个 情况.