飞利浦半导体 产品 规格

SC26C94Quad普遍的 异步的 接受者/传输者 (quart)

1995 将 1

4

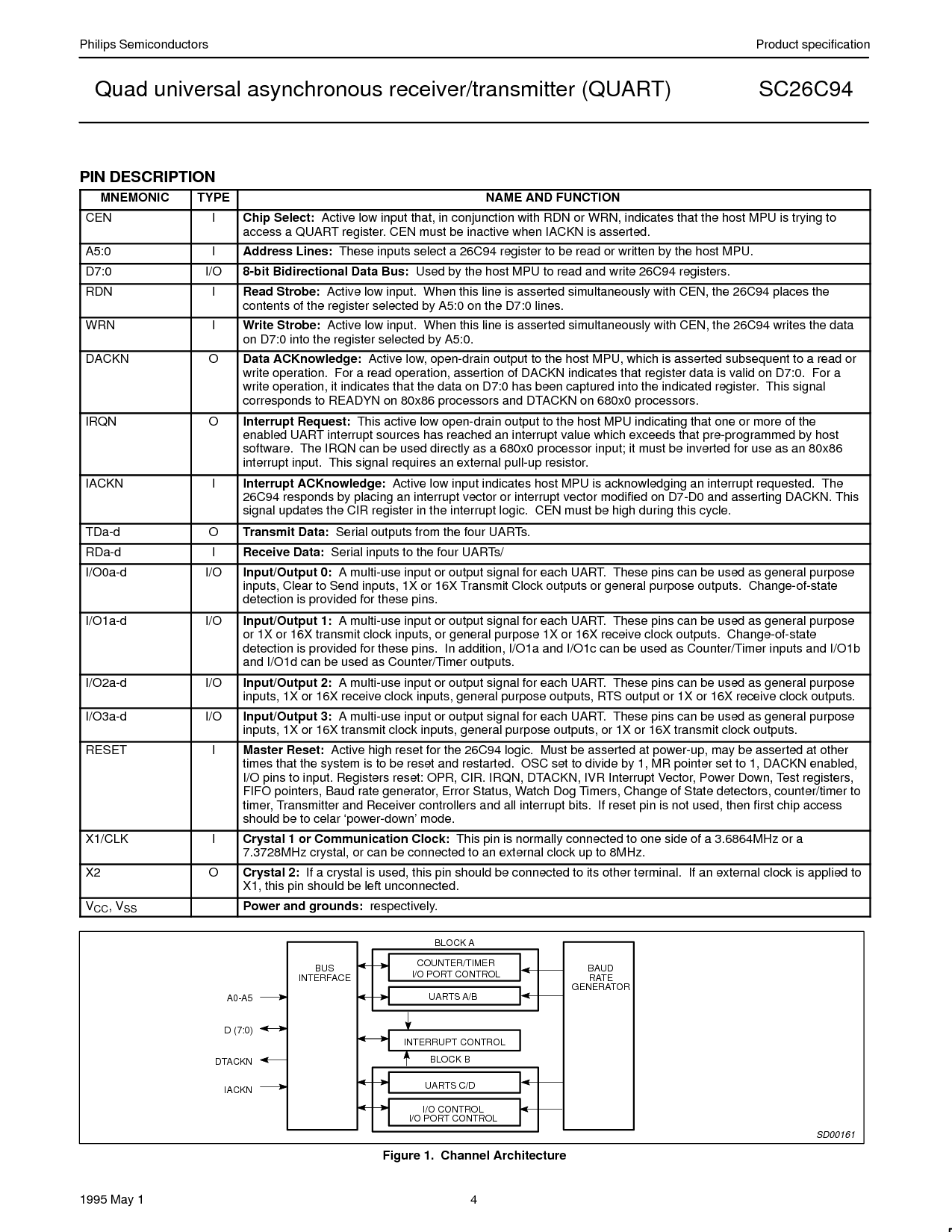

管脚描述

MNEMONIC 类型 名字 和 函数

CEN I

碎片 选择:

起作用的 低 输入 那, 在 conjunction 和 rdn 或者 wrn, indicates 那 这 host mpu 是 trying 至

进入 一个 quart 寄存器. cen 必须 是 inactive 当 iackn 是 asserted.

a5:0 I

地址 线条:

这些 输入 选择 一个 26c94 寄存器 至 是 读 或者 写 用 这 host mpu.

d7:0 i/o

8-位 双向的 数据 总线:

使用 用 这 host mpu 至 读 和 写 26c94 寄存器.

RDN I

读 strobe:

起作用的 低 输入. 当 这个 线条 是 asserted 同时发生地 和 cen, 这 26c94 places 这

内容 的 这 寄存器 选择 用 a5:0 在 这 d7:0 线条.

WRN I

Write strobe:

起作用的 低 输入. 当 这个 线条 是 asserted 同时发生地 和 cen, 这 26c94 写 这 数据

在 d7:0 在 这 寄存器 选择 用 a5:0.

DACKN O

数据 acknowledge:

起作用的 低, 打开-流 输出 至 这 host mpu, 这个 是 asserted subsequent 至 一个 读 或者

写 运作. 为 一个 读 运作, assertion 的 dackn indicates 那 寄存器 数据 是 有效的 在 d7:0. 为 一个

写 运作, 它 indicates 那 这 数据 在 d7:0 有 被 captured 在 这 表明 寄存器. 这个 信号

corresponds 至 readyn 在 80x86 processors 和 dtackn 在 680x0 processors.

IRQN O

中断 要求:

这个 起作用的 低 打开-流 输出 至 这 host mpu 表明 那 一个 或者 更多 的 这

使能 uart 中断 来源 有 reached 一个 中断 值 这个 超过 那 前-编写程序 用 host

软件. 这 irqn 能 是 使用 直接地 作 一个 680x0 处理器 输入; 它 必须 是 inverted 为 使用 作 一个 80x86

中断 输入. 这个 信号 需要 一个 外部 拉-向上 电阻.

IACKN I

中断 acknowledge:

起作用的 低 输入 indicates host mpu 是 acknowledging 一个 中断 要求. 这

26c94 responds 用 放置 一个 中断 vector 或者 中断 vector 修改 在 d7-d0 和 asserting dackn. 这个

信号 updates 这 cir 寄存器 在 这 中断 逻辑. cen 必须 是 高 在 这个 循环.

tda-d O

Transmit 数据:

串行 输出 从 这 四 uarts.

rda-d I

receive 数据:

串行 输入 至 这 四 uarts/

i/o0a-d i/o

输入/输出 0:

一个 multi-使用 输入 或者 输出 信号 为 各自 uarT. 这些 管脚 能 是 使用 作 一般 目的

输入, clear 至 send 输入, 1x 或者 16x transmit 时钟 输出 或者 一般 目的 输出. 改变-的-状态

发现 是 提供 为 这些 管脚.

i/o1a-d i/o

输入/输出 1:

一个 multi-使用 输入 或者 输出 信号 为 各自 uarT. 这些 管脚 能 是 使用 作 一般 目的

或者 1x 或者 16x transmit 时钟 输入, 或者 一般 目的 1x 或者 16x receive 时钟 输出. 改变-的-状态

发现 是 提供 为 这些 管脚. 在 增加, i/o1a 和 i/o1c 能 是 使用 作 counter/timer 输入 和 i/o1b

和 i/o1d 能 是 使用 作 计数器/timer 输出.

i/o2a-d i/o

输入/输出 2:

一个 multi-使用 输入 或者 输出 信号 为 各自 uarT. 这些 管脚 能 是 使用 作 一般 目的

输入, 1x 或者 16x receive 时钟 输入, 一般 目的 输出, rts 输出 或者 1x 或者 16x receive 时钟 输出.

i/o3a-d i/o

输入/输出 3:

一个 multi-使用 输入 或者 输出 信号 为 各自 uarT. 这些 管脚 能 是 使用 作 一般 目的

输入, 1x 或者 16x transmit 时钟 输入, 一般 目的 输出, 或者 1x 或者 16x transmit 时钟 输出.

重置 I

主控 重置:

起作用的 高 重置 为 这 26c94 逻辑. 必须 是 asserted 在 电源-向上, 将 是 asserted 在 其它

时间 那 这 系统 是 至 是 重置 和 restarted. osc 设置 至 分隔 用 1, mr pointer 设置 至 1, dackn 使能,

i/o 管脚 至 输入. 寄存器 重置: opr, cir. irqn, dtackn, ivr 中断 vector, 电源 向下, test 寄存器,

先进先出 pointers, 波特 比率 发生器, 错误 状态, watch dog timers, 改变 的 状态 detectors, 计数器/计时器 至

计时器, transmitter 和 接受者 控制者 和 所有 中断 位. 如果 重置 管脚 是 不 使用, 然后 第一 碎片 进入

应当 是 至 celar ‘power-向下’ 模式.

x1/clk I

结晶 1 或者 交流 时钟:

这个 管脚 是 正常情况下 连接 至 一个 一侧 的 一个 3.6864mhz 或者 一个

7.3728mhz 结晶, 或者 能 是 连接 至 一个 外部 时钟 向上 至 8mhz.

X2 O

结晶 2:

如果 一个 结晶 是 使用, 这个 管脚 应当 是 连接 至 它的 其它 终端. 如果 一个 外部 时钟 是 应用 至

x1, 这个 管脚 应当 是 left unconnected.

V

CC

, v

SS

电源 和 grounds:

各自.

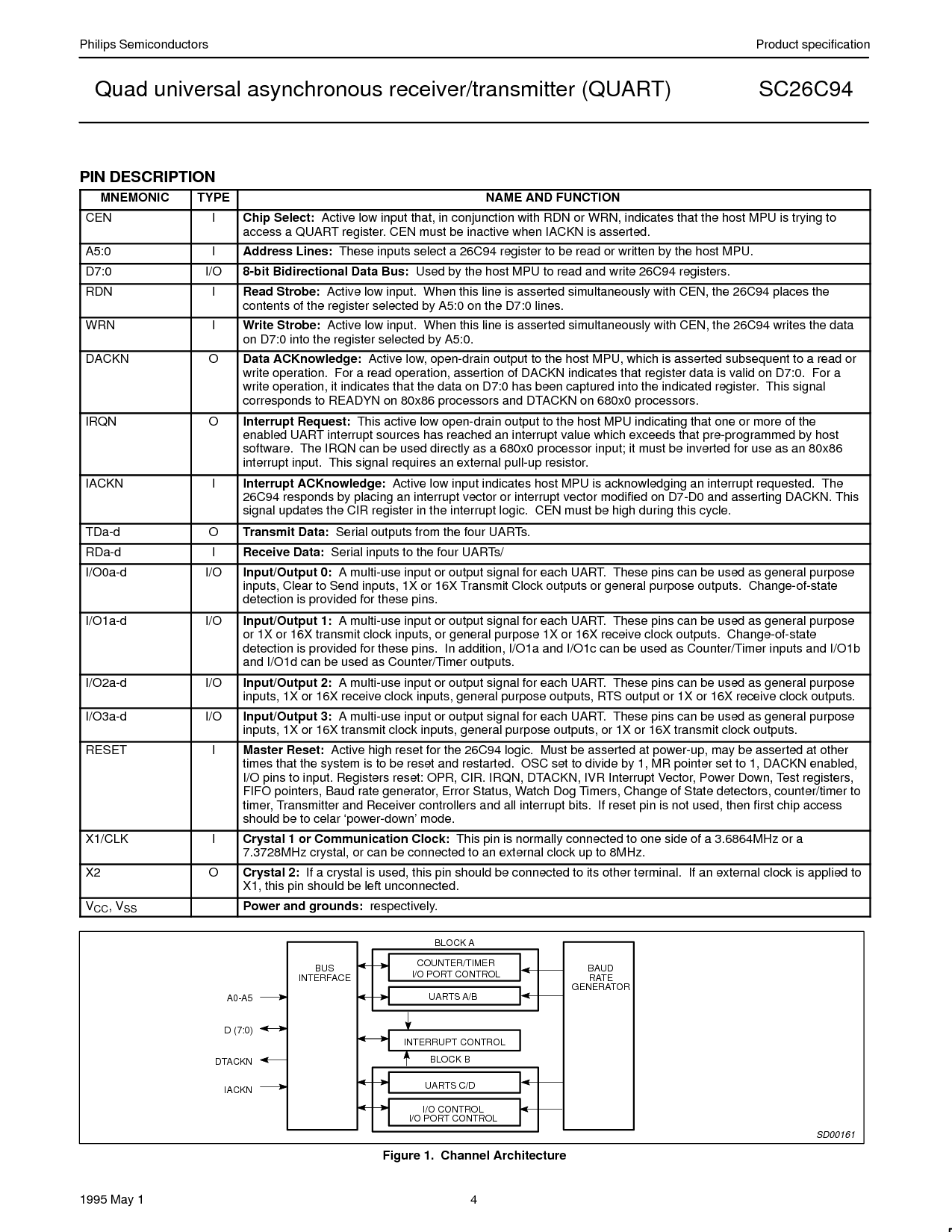

计数器/计时器

i/o 端口控制

uarts 一个/b

中断控制

块 b

uarts c/d

i/o 控制

i/o 端口控制

a0-a5

d (7:0)

DTACKN

IACKN

波特

比率

发生器

总线

接口

块 一个

SD00161

图示 1. 频道 architecture