9

64mb: x32 sdram micron 技术, inc., reserves 这 正确的 至 改变 产品 或者 规格 没有 注意.

64msdramx32_5.p65 – rev. b; pub. 6/02 ©2002, micron 技术, 公司

64mb: x32

SDRAM

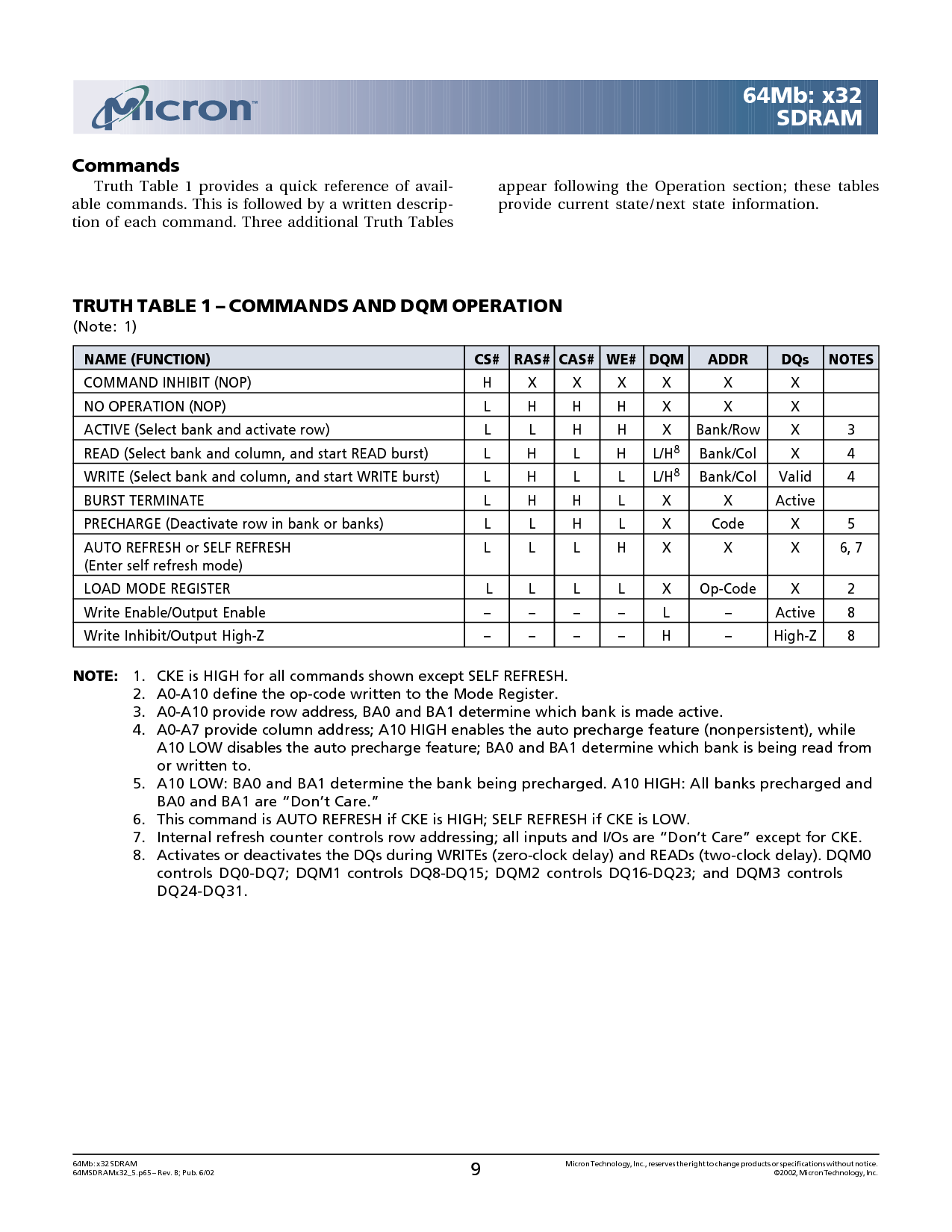

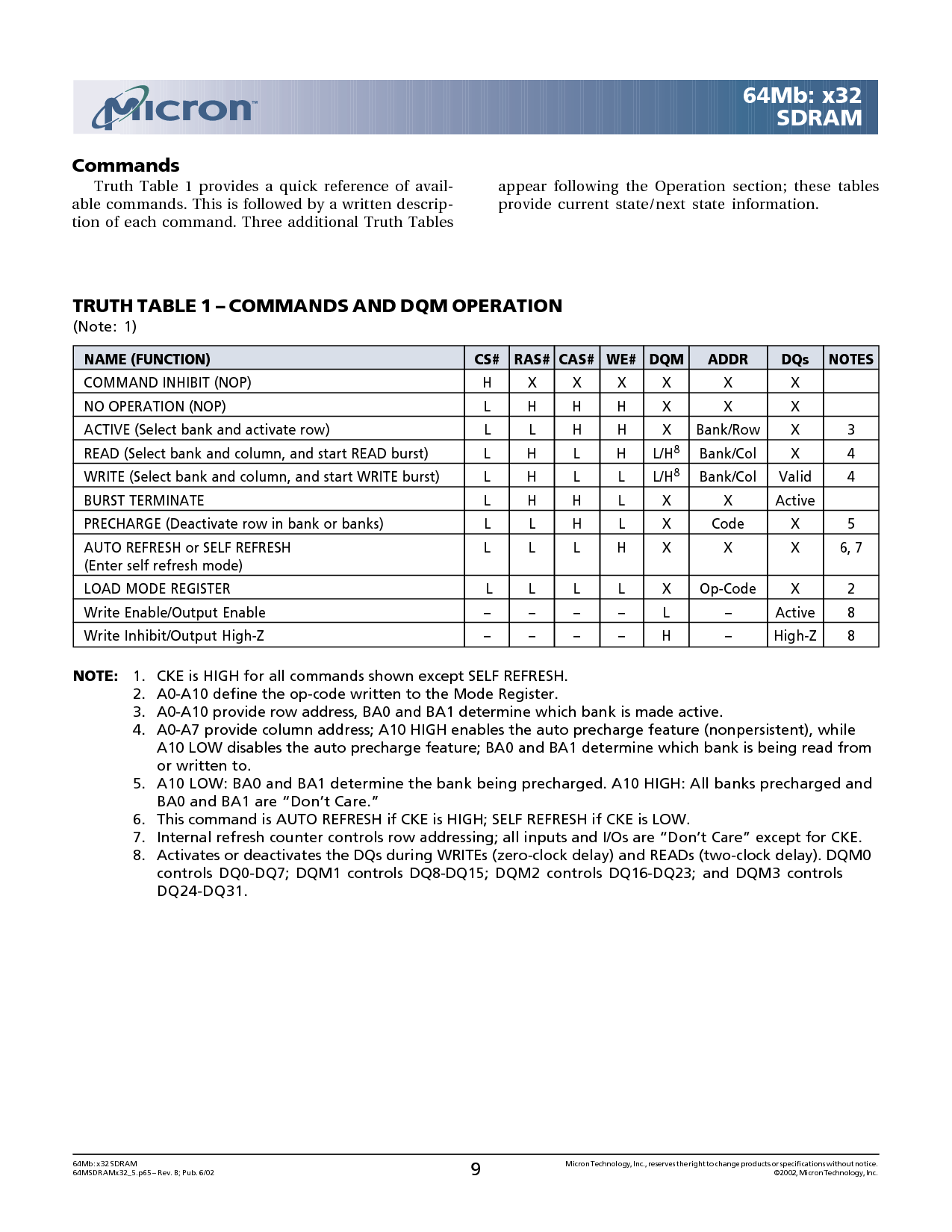

真实 表格 1 – commands 和 dqm 运作

(便条: 1)

名字 (函数) CS# RAS# CAS# WE# DQM 地址 DQs 注释

command inhibit (nop) H XXXX X X

非 运作 (nop) L H H H X X X

起作用的 (选择 bank 和 活动 行) L L H H X bank/行 X 3

读 (选择 bank 和 column, 和 开始 读 burst) L H L H l/h

8

bank/col X 4

写 (选择 bank 和 column, 和 开始 写 burst) L H L L l/h

8

bank/col 有效的 4

burst terminate L H H L X X 起作用的

precharge (deactivate 行 在 bank 或者banks) L L H L X 代号 X 5

自动 refresh 或者 自 refresh L L L H X X X 6, 7

(enter 自 refresh 模式)

加载 模式 寄存器 L L L L X 运算-代号 X 2

写 使能/输出 使能 ––––L – 一个ctive 8

写 inhibit/输出 高-z ––––H – 高-z 8

呈现 下列的 这 运作 部分; 这些 tables

提供 电流 状态/next 状态 信息.

Commands

真实 表格 1 提供 一个 快 涉及 的 avail-

能 commands. 这个 是 followed 用 一个 写 descrip-

tion 的 各自 command. 三 额外的 真实 tables

便条:

1. cke 是 高 为 所有 commands 显示 除了 自 refresh.

2. a0-a10 定义 这 运算-代号 写 至 这 模式 寄存器.

3. a0-a10 提供 行 地址, ba0 和 ba1 决定 这个 bank 是 制造 起作用的.

4. a0-a7 提供 column 地址; a10 高 使能 这 自动 precharge 特性 (nonpersistent), 当

a10 低 使不能运转 这 自动 precharge 特性; ba0 和 ba1 决定 这个 bank 是 正在 读 从

或者 写 至.

5. a10 低: ba0 和 ba1 决定 这 bank 正在 precharged. a10 高: 所有 banks precharged 和

ba0 和 ba1 是 “don’t 小心.”

6. 这个 command 是 自动 refresh 如果 cke 是 高; 自 refresh 如果 cke 是 低.

7. 内部的 refresh 计数器 控制 行 寻址; 所有 输入 和 i/os 是 “don’t care” 除了 为 cke.

8. activates 或者 deactivates 这 dqs 在 写 (零-时钟 延迟) 和 读 (二-时钟 延迟). dqm0

控制 dq0-dq7; dqm1 控制 dq8-dq15; dqm2 控制 dq16-dq23; 和 dqm3 控制

dq24-dq31.