sprs095e – march 1999 – 修订 将 2000

7

邮递 办公室 盒 1443

•

houston, 德州 77251–1443

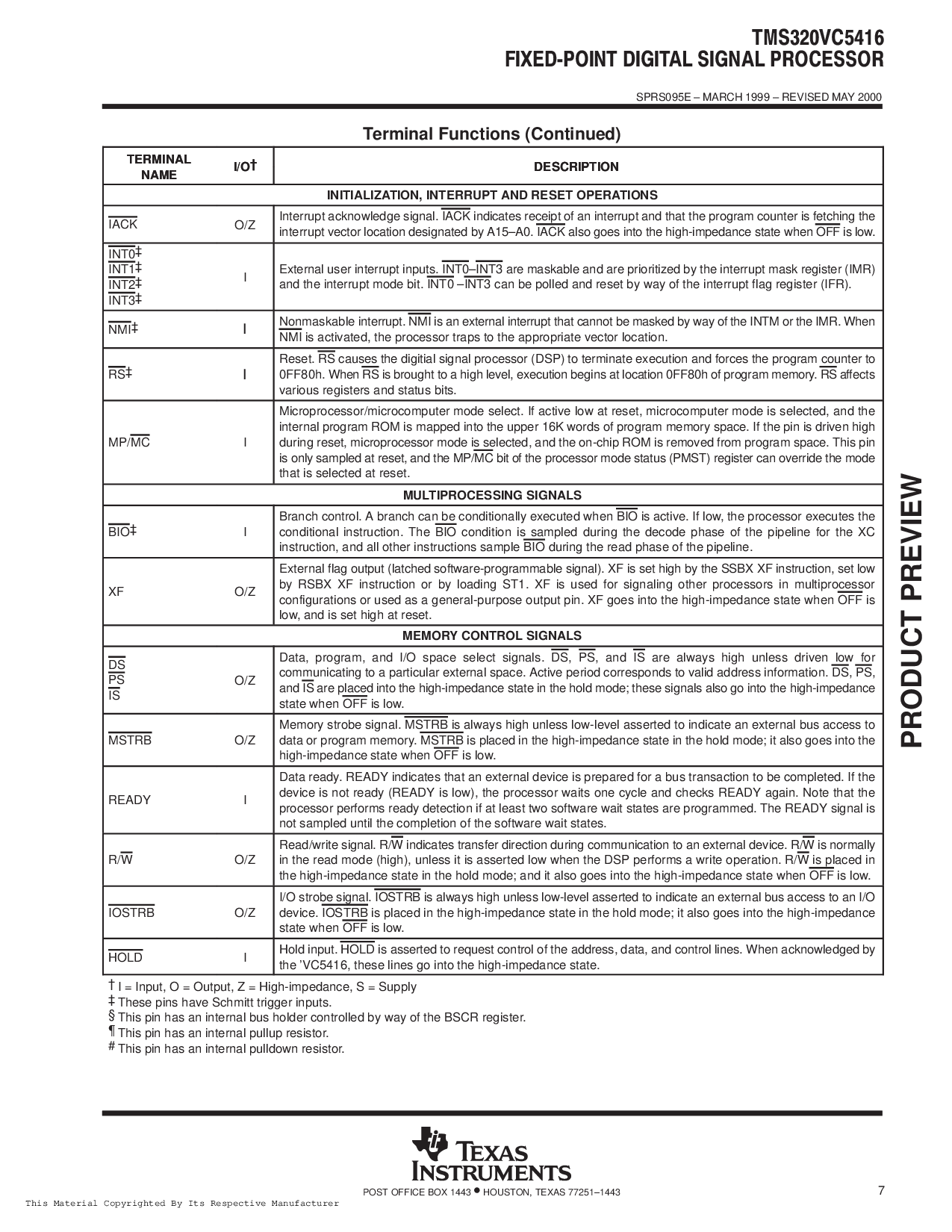

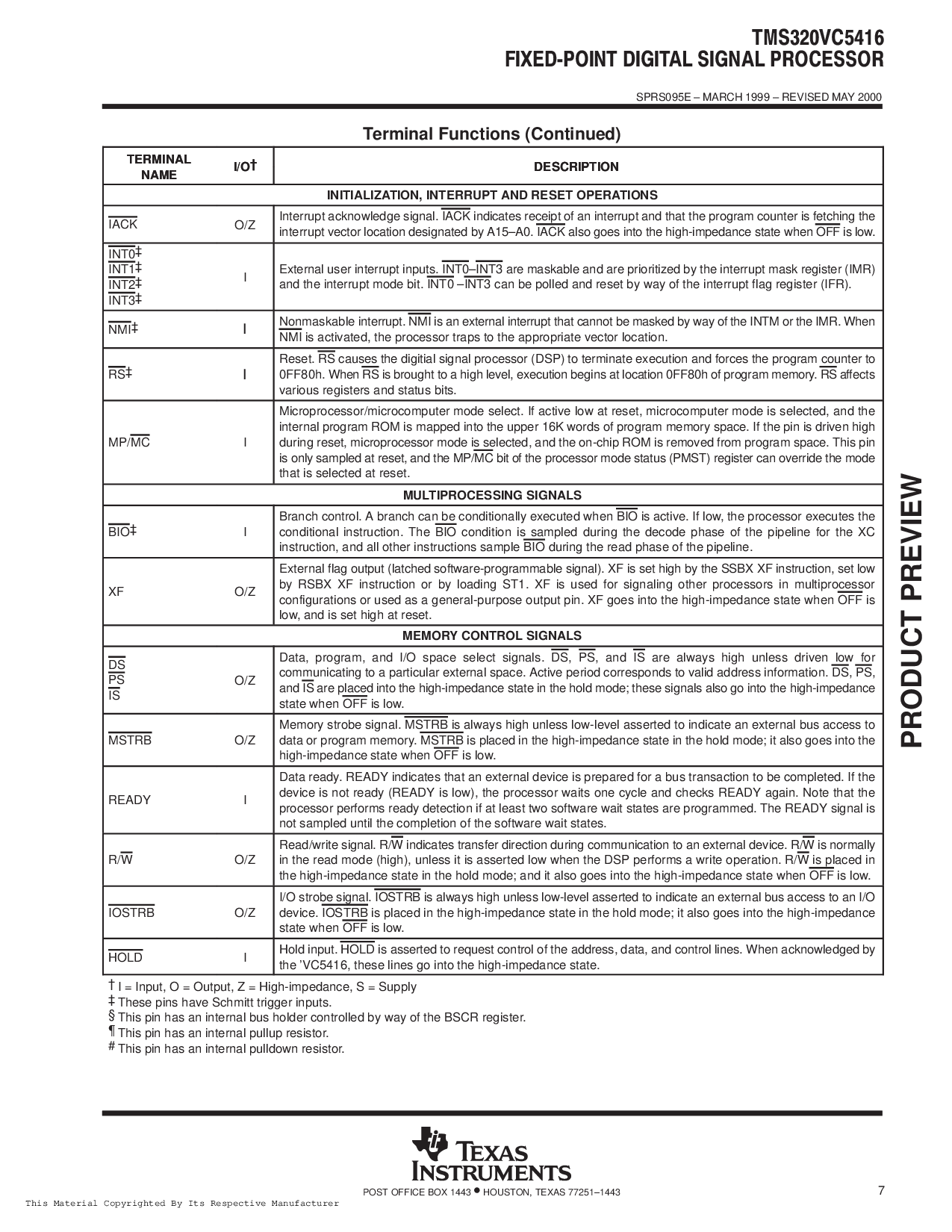

终端 功能 (持续)

终端

名字

descriptioni/o

†

终端

名字

descriptioni/o

†

initialization, 中断 和 重置 行动

IACK

o/z

中断 acknowledge信号. iackindicates receipt 的 一个 中断 和 那 这 程序 计数器 是 fetching 这

中断vector location designated 用 a15–a0. iack

也 变得 在 这 高-阻抗 状态 当 止是 低.

INT0

‡

INT1

‡

INT2

‡

INT3

‡

I

外部 用户 中断 输入. int0–INT3是 maskable 和 是 prioritized 用 这 中断 掩饰 寄存器 (imr)

和 这 中断 模式 位. int0

–int3 能 是 polled 和 重置 用 方法 的 这 中断 标记 寄存器 (ifr).

NMI

‡

I

Nonmaskable中断. nmi是 一个 外部 中断 那 不能 是 masked 用 方法 的 这 intm 或者 这 imr. 当

NMI

是 使活动, 这 处理器 traps 至 这 适合的 vector location.

RS

‡

I

重置. rs导致 这 digitial 信号 处理器 (dsp) 至 terminate 执行 和 forces 这 程序 计数器 至

0ff80h.当 rs

是 brought 至 一个 高 水平的, 执行 begins 在 location 0ff80h 的 程序 记忆. rsaffects

各种各样的 寄存器 和 状态 位.

mp/mc I

微处理器/microcomputer 模式 选择. 如果 起作用的 低 在 重置, microcomputer 模式 是 选择, 和 这

内部的 程序 只读存储器 是 编排 在 这 upper 16k words 的 程序 记忆 空间. 如果 这 管脚 是 驱动 高

在重置, 微处理器 模式 是 选择, 和 这 在-碎片 只读存储器 是 移除 从 程序 空间. 这个 管脚

是 仅有的 抽样 在 重置, 和 这 mp/mc

位 的 这 处理器 模式 状态 (pmst) 寄存器 能 override 这 模式

那 是 选择 在 重置.

multiprocessing 信号

BIO

‡

I

branch 控制. 一个 branch 能 是 conditionally executed 当 bio是 起作用的. 如果 低, 这 处理器 executes 这

conditional 操作指南. 这 bio

情况 是 抽样 在 这 decode 阶段 的 这 pipeline 为 这 xc

操作指南, 和 所有 其它 说明 样本 bio

在 这 读 阶段 的 这 pipeline.

XF o/z

外部标记 输出 (latched 软件-可编程序的 信号). xf 是 设置 高 用 这 ssbx xf 操作指南, 设置 低

用 rsbx xf 操作指南 或者 用 加载 st1. xf 是 使用 为 signaling 其它 processors 在 multiprocessor

配置 或者 使用 作 一个 一般-目的 输出 管脚. xf 变得 在 这 高-阻抗 状态 当 止

是

低, 和 是 设置 高 在 重置.

记忆 控制 信号

DS

PS

是

o/z

数据, 程序, 和 i/o 空间 选择 信号. ds, ps, 和 是是 总是 高 除非 驱动 低 为

communicating 至 一个 particular 外部 空间. 起作用的 时期 corresponds 至 有效的 地址 信息. ds

, ps,

和 是

是 放置 在 这 高-阻抗 状态 在 这 支撑 模式; 这些 信号 也 go 在 这 高-阻抗

状态 当 止

是 低.

MSTRB o/z

记忆 strobe 信号. mstrb是 总是 高 除非 低-水平的 asserted 至 表明 一个 外部 总线 进入 至

数据 或者 程序 记忆. mstrb

是 放置 在 这 高-阻抗 状态 在 这 支撑 模式; 它 也 变得 在 这

高-阻抗 状态 当 止

是 低.

准备好 I

数据 准备好. 准备好 indicates 那 一个 外部 设备 是 准备好 为 一个 总线 transaction 至 是 完成. 如果 这

设备 是 不 准备好 (准备好 是 低), 这 处理器 waits 一个 循环 和 checks 准备好 又一次. 便条 那 这

处理器 执行 准备好 发现 如果 在 least 二 软件 wait states 是 编写程序. 这 准备好 信号 是

不 抽样 直到 这 completion 的 这 软件 wait states.

r/w o/z

读/写信号. r/windicates 转移 方向 在 交流 至 一个 外部 设备. r/w是 正常情况下

在 这 读 模式 (高), 除非 它 是 asserted 低 当 这 dsp 执行 一个 写 运作. r/w

是 放置 在

这 高-阻抗 状态 在 这 支撑 模式; 和 它 也 变得 在 这 高-阻抗 状态 当 止

是 低.

IOSTRB o/z

i/o strobe 信号. iostrb是 总是 高 除非 低-水平的 asserted 至 表明 一个 外部 总线 进入 至 一个 i/o

设备. iostrb

是 放置 在 这 高-阻抗 状态 在 这 支撑 模式; 它 也 变得 在 这 高-阻抗

状态 当 止

是 低.

支撑 I

支撑输入. 支撑 是 asserted 至 要求 控制 的 这 地址, 数据, 和 控制 线条. 当 acknowledged 用

这 ’vc5416, 这些 线条 go 在 这 高-阻抗 状态.

†

i = 输入, o = 输出, z = 高-阻抗, s = 供应

‡

这些 管脚 有 施密特 触发 输入.

§

这个 管脚 有 一个 内部的 总线 holder 控制 用 方法 的 这 bscr 寄存器.

¶

这个 管脚 有 一个 内部的 pullup 电阻.

#

这个 管脚 有 一个 内部的 pulldown 电阻.

产品 预告(展)

这个 材料 版权 用 它的 各自的 生产者