–6–

AD1854

rev. 一个

运行 特性

串行 数据 输入 端口

这 ad1854’s 有伸缩性的 串行 数据 输入 端口 accepts 数据 在

twos-complement, msb-第一 format. 这 left 频道 数据 地方

总是 precedes 这 正确的 频道 数据 地方. 这 输入 数据

组成 的 也 16, 18, 20, 或者 24 位, 作 established 用 这

模式 选择 管脚 (idpm0 管脚 21 和 idpm1 管脚 20) 或者 这

模式 选择 位 (位 15 和 14) 在 这 控制 寄存器 通过

这 spi (串行 附带的 接口) 控制 端口. neither 这

管脚 也不 这 spi 控制 有 preference; 至 确保 恰当的 控制,

这 选择 不 正在 使用 应当 是 系 lo. 因此,

当 这 spi 位 是 使用 至 控制 串行 数据 输入 format,

管脚 20 和 21 应当 是 系 lo. similarly, 当 这 管脚 是

至 是 使用 至 选择 这 数据 format, 这 spi 位 应当 是 设置

至 zeros. 当 这 spi 控制 端口 是 不 正在 使用, 这 spi

管脚 (3, 4, 和 5) 应当 是 系 lo.

串行 数据 输入 模式

这 ad1854 使用 二 多路复用 输入 管脚 至 控制 这

模式 配置 的 这 输入 数据 端口 模式 作 跟随:

表格 i. 串行 数据 输入 模式

IDPM1 IDPM0

(管脚 20) (管脚 21) 串行 数据 输入 format

0 0 正确的 justified (16 位)

01 I

2

s-兼容

1 0 正确的 justified (20 位)

1 1 正确的 justified (24 位)

位 时钟 0 left justified

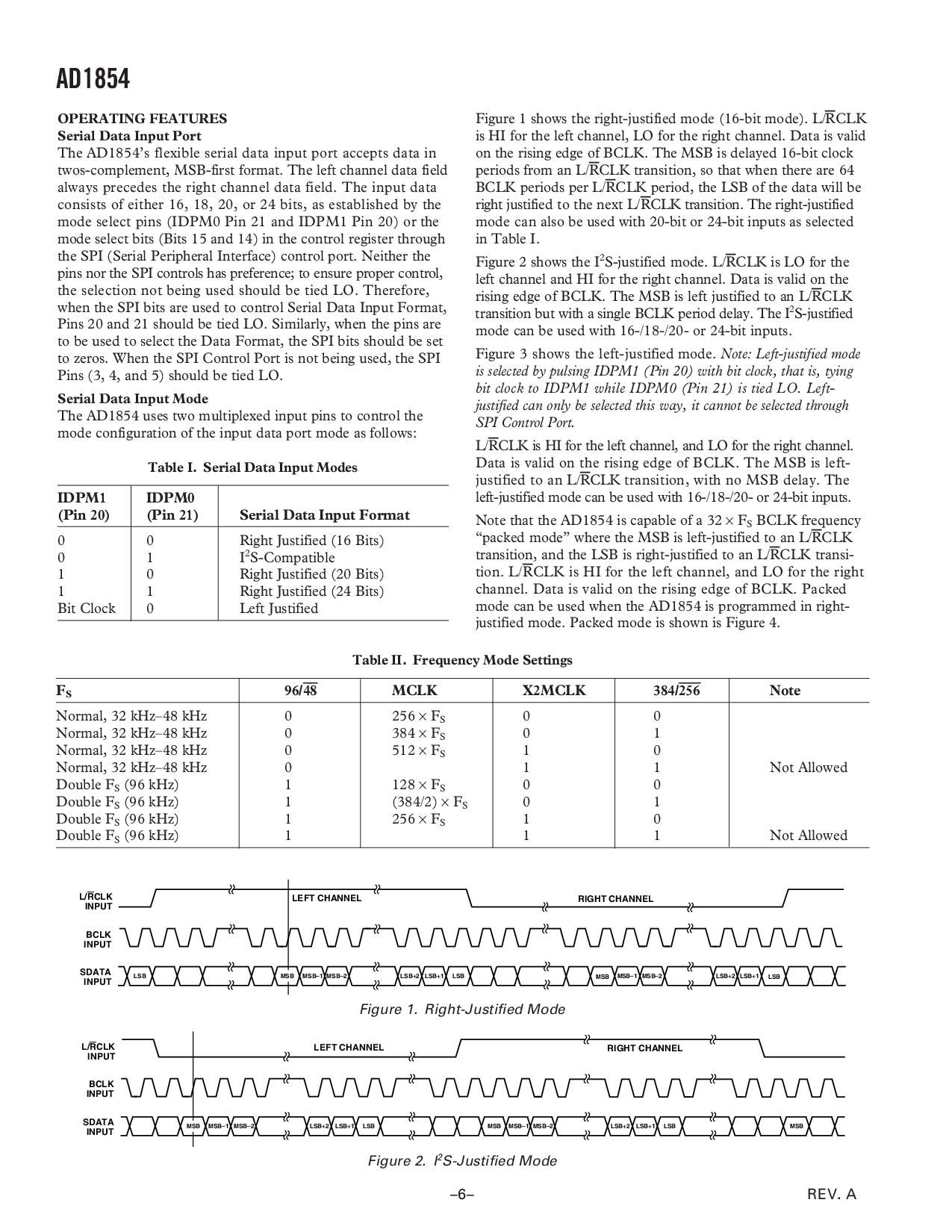

图示 1 显示 这 正确的-justified 模式 (16-位 模式). l/

R

CLK

是 hi 为 这 left 频道, lo 为 这 正确的 频道. 数据 是 有效的

在 这 rising 边缘 的 bclk. 这 msb 是 delayed 16-位 时钟

时期 从 一个 l/

R

clk 转变, 所以 那 当 那里 是 64

bclk 时期 每 l/

R

clk 时期, 这 lsb 的 这 数据 将 是

正确的 justified 至 这 next l/

R

clk 转变. 这 正确的-justified

模式 能 也 是 使用 和 20-位 或者 24-位 输入 作 选择

在 表格 i.

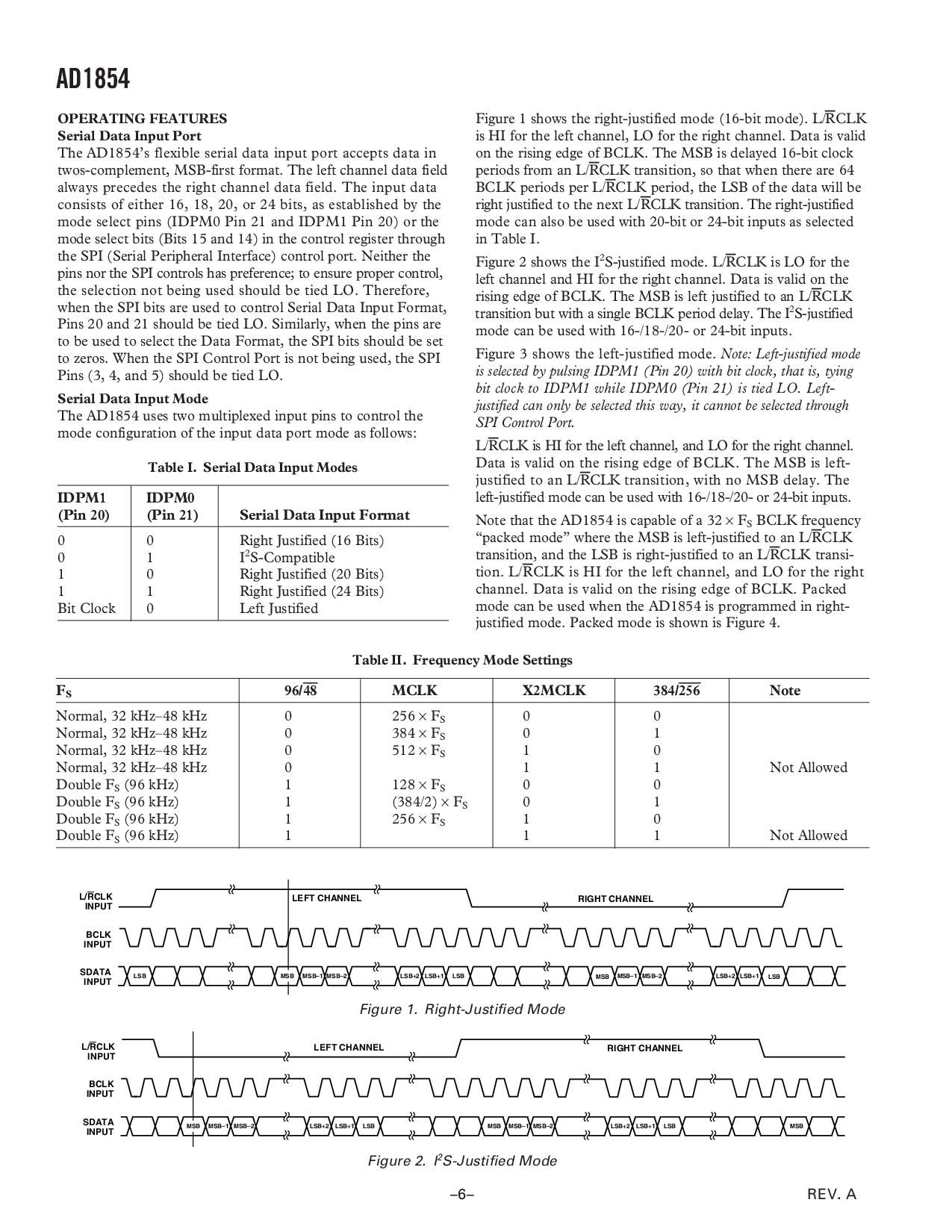

图示 2 显示 这 i

2

s-justified 模式. l/

R

clk 是 lo 为 这

left 频道 和 hi 为 这 正确的 频道. 数据 是 有效的 在 这

rising 边缘 的 bclk. 这 msb 是 left justified 至 一个 l/

R

CLK

转变 但是 和 一个 单独的 bclk 时期 延迟. 这 i

2

s-justified

模式 能 是 使用 和 16-/18-/20- 或者 24-位 输入.

图示 3 显示 这 left-justified 模式.

便条: left-justified 模式

是 选择 用 pulsing idpm1 (管脚 20) 和 位 时钟, 那 是, tying

位 时钟 至 idpm1 当 idpm0 (管脚 21) 是 系 lo. left-

justified 能 仅有的 是 选择 这个 方法, 它 不能 是 选择 通过

spi 控制 端口.

l/

R

clk 是 hi 为 这 left 频道, 和 lo 为 这 正确的 频道.

数据 是 有效的 在 这 rising 边缘 的 bclk. 这 msb 是 left-

justified 至 一个 l/

R

clk 转变, 和 非 msb 延迟. 这

left-justified 模式 能 是 使用 和 16-/18-/20- 或者 24-位 输入.

便条 那 这 ad1854 是 有能力 的 一个 32

×

F

S

bclk 频率

“packed mode” 在哪里 这 msb 是 left-justified 至 一个 l/

R

CLK

转变, 和 这 lsb 是 正确的-justified 至 一个 l/

R

clk transi-

tion. l/

R

clk 是 hi 为 这 left 频道, 和 lo 为 这 正确的

频道. 数据 是 有效的 在 这 rising 边缘 的 bclk. packed

模式 能 是 使用 当 这 ad1854 是 编写程序 在 正确的-

justified 模式. packed 模式 是 显示 是 图示 4.

表格 ii. 频率 模式 settings

F

S

96/

48

MCLK X2MCLK 384/

256

便条

正常的, 32 khz–48 khz 0 256

×

F

S

00

正常的, 32 khz–48 khz 0 384

×

F

S

01

正常的, 32 khz–48 khz 0 512

×

F

S

10

正常的, 32 khz–48 khz 0 1 1 不 允许

翻倍 f

S

(96 khz) 1 128

×

F

S

00

翻倍 f

S

(96 khz) 1 (384/2)

×

F

S

01

翻倍 f

S

(96 khz) 1 256

×

F

S

10

翻倍 f

S

(96 khz) 1 1 1 不 允许

SDATA

输入

LSBMSB

–

2MSB

–

1 LSB+2 LSB+1

MSB

–

2

MSB

–

1

MSB

LSB+2

LSB+1

LSB

BCLK

输入

l/

R

CLK

输入

left 频道

正确的 频道

MSB

LSB

图示 1. 正确的-justified 模式

left 频道

正确的 频道

MSB

–

2MSB

–

1 LSB+2 LSB+1 LSB MSB

–

2MSB

–

1MSB LSB+2 LSB+1 LSB MSB

l/

R

CLK

输入

BCLK

输入

SDATA

输入

MSB

图示 2. I

2

s-justified 模式