AD7008

rev. b

–5–

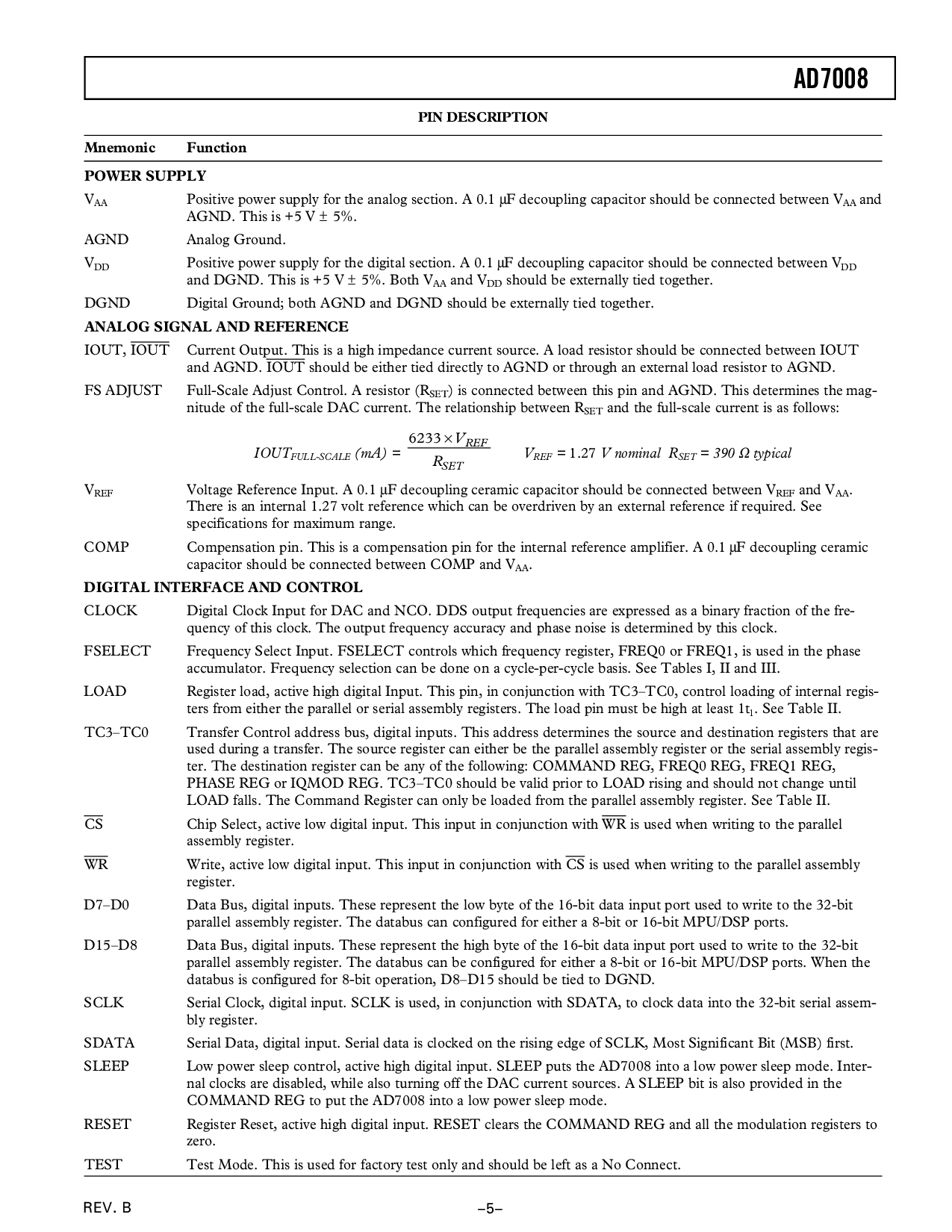

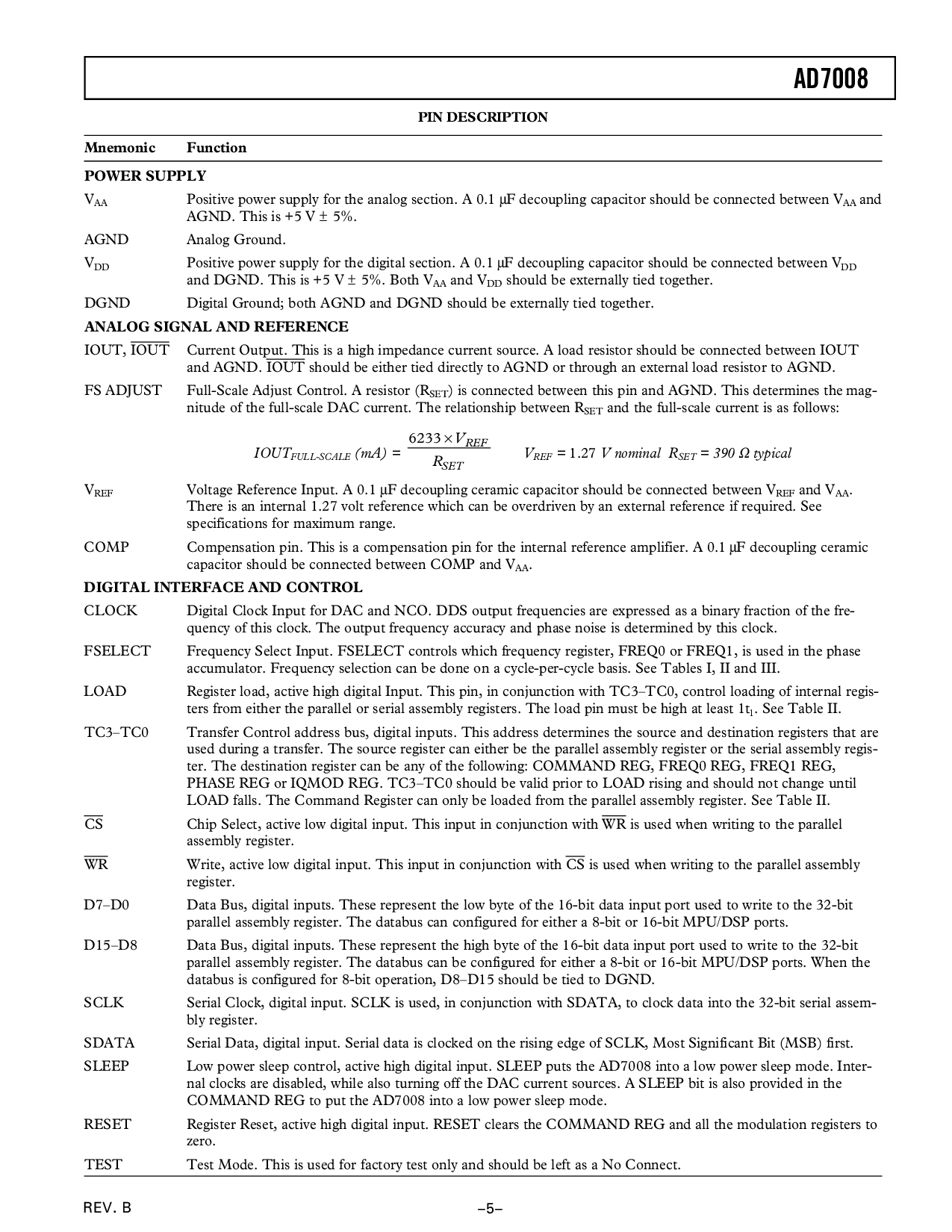

管脚 描述

Mnemonic 函数

电源 供应

V

AA

积极的 电源 供应 为 这 相似物 部分. 一个 0.1

µ

f 解耦 电容 应当 是 连接 在 v

AA

和

agnd. 这个 是 +5 v

±

5%.

AGND 相似物 地面.

V

DD

积极的 电源 供应 为 这 数字的 部分. 一个 0.1

µ

f 解耦 电容 应当 是 连接 在 v

DD

和 dgnd. 这个 是 +5 v

±

5%. 两个都 v

AA

和 v

DD

应当 是 externally 系 一起.

DGND 数字的 地面; 两个都 agnd 和 dgnd 应当 是 externally 系 一起.

相似物 信号 和 涉及

iout,

IOUT

电流 输出. 这个 是 一个 高 阻抗 电流 源. 一个 加载 电阻 应当 是 连接 在 iout

和 agnd.

IOUT

应当 是 也 系 直接地 至 agnd 或者 通过 一个 外部 加载 电阻 至 agnd.

fs 调整 全部-规模 调整 控制. 一个 电阻 (r

设置

) 是 连接 在 这个 管脚 和 agnd. 这个 确定 这 mag-

nitude 的 这 全部-规模 dac 电流. 这 relationship 在 r

设置

和 这 全部-规模 电流 是 作 跟随:

IOUT

全部-规模

(毫安) =

6233

×

V

REF

R

设置

V

REF

=

1.27

v 名义上的 r

设置

= 390

Ω

典型

V

REF

电压 涉及 输入. 一个 0.1

µ

f 解耦 陶瓷的 电容 应当 是 连接 在 v

REF

和 v

AA

.

那里 是 一个 内部的 1.27 volt 涉及 这个 能 是 过载 用 一个 外部 涉及 如果 必需的. 看

规格 为 最大 范围.

竞赛 补偿 管脚. 这个 是 一个 补偿 管脚 为 这 内部的 涉及 放大器. 一个 0.1

µ

f 解耦 陶瓷的

电容 应当 是 连接 在 竞赛 和 v

AA

.

数字的 接口 和 控制

时钟 数字的 时钟 输入 为 dac 和 nco. dds 输出 发生率 是 表示 作 一个 二进制的 fraction 的 这 fre-

quency 的 这个 时钟. 这 输出 频率 精度 和 阶段 噪音 是 决定 用 这个 时钟.

FSELECT 频率 选择 输入. fselect 控制 这个 频率 寄存器, freq0 或者 freq1, 是 使用 在 这 阶段

accumulator. 频率 选择 能 是 完毕 在 一个 循环-每-循环 基准. 看 tables i, ii 和 iii.

加载 寄存器 加载, 起作用的 高 数字的 输入. 这个 管脚, 在 conjunction 和 tc3–tc0, 控制 加载 的 内部的 regis-

ters 从 也 这 并行的 或者 串行 组装 寄存器. 这 加载 管脚 必须 是 高 在 least 1t

1

. 看 表格 ii.

TC3–TC0 转移 控制 地址 总线, 数字的 输入. 这个 地址 确定 这 源 和 destination 寄存器 那 是

使用 在 一个 转移. 这 源 寄存器 能 也 是 这 并行的 组装 寄存器 或者 这 串行 组装 regis-

ter. 这 destination 寄存器 能 是 任何 的 这 下列的: command reg, freq0 reg, freq1 reg,

阶段 reg 或者 iqmod reg. tc3–tc0 应当 是 有效的 较早的 至 加载 rising 和 应当 不 改变 直到

加载 falls. 这 command 寄存器 能 仅有的 是 承载 从 这 并行的 组装 寄存器. 看 表格 ii.

CS

碎片 选择, 起作用的 低 数字的 输入. 这个 输入 在 conjunction 和

WR

是 使用 当 writing 至 这 并行的

组装 寄存器.

WR

写, 起作用的 低 数字的 输入. 这个 输入 在 conjunction 和

CS

是 使用 当 writing 至 这 并行的 组装

寄存器.

D7–D0 数据 总线, 数字的 输入. 这些 代表 这 低 字节 的 这 16-位 数据 输入 端口 使用 至 写 至 这 32-位

并行的 组装 寄存器. 这 databus 能 配置 为 也 一个 8-位 或者 16-位 mpu/dsp ports.

D15–D8 数据 总线, 数字的 输入. 这些 代表 这 高 字节 的 这 16-位 数据 输入 端口 使用 至 写 至 这 32-位

并行的 组装 寄存器. 这 databus 能 是 配置 为 也 一个 8-位 或者 16-位 mpu/dsp ports. 当 这

databus 是 配置 为 8-位 运作, d8–d15 应当 是 系 至 dgnd.

SCLK 串行 时钟, 数字的 输入. sclk 是 使用, 在 conjunction 和 sdata, 至 时钟 数据 在 这 32-bit 串行 assem-

bly 寄存器.

SDATA 串行 数据, 数字的 输入. 串行 数据 是 clocked 在 这 rising 边缘 的 sclk, 大多数 重大的 位 (msb) first.

睡眠 低 电源 睡眠 控制, 起作用的 高 数字的 输入. 睡眠 puts 这 ad7008 在 一个 低 电源 睡眠 模式. inter-

nal clocks 是 无能, 当 也 turning 止 这 dac 电流 来源. 一个 睡眠 位 是 也 提供 在 这

command reg 至 放 这 ad7008 在 一个 低 电源 睡眠 模式.

重置 寄存器 重置, 起作用的 高 数字的 输入. 重置 clears 这 command reg 和 所有 这 调制 寄存器 至

零.

测试 测试 模式. 这个 是 使用 为 工厂 测试 仅有的 和 应当 是 left 作 一个 非 连接.